8- bis 10-bit-A/D-Wandler

Eine Plattform für die HF- und Messtechnik

Fortsetzung des Artikels von Teil 1

Phasenabgleichfehler und INL-Fehlanpassungen

Die Auswirkungen von Verstärkungs- Fehlanpassungen sind zwar ebenfalls unabhängig von Überabtastraten(OSR), allerdings skaliert der Fehler mit der Signalamplitude. Deshalb treten Verstärkungs-Fehler bei starken Eingangssignalen stärker zu Tage. Bild 2 zeigt die Auswirkungen eines Verstärkungs-Fehlers von 1% im Kanal B auf das rekonstruierte Interleaved- Signal bei 8 bit Auflösung. Verstärkungs- Anpassungsfehler sind im rekonstruierten Signal dann am stärksten, wenn der Vollausschlag der resultierenden relativen Fehler größer oder gleich einem LSB ist.

Mit der per SPI digital regelbaren Verstärkung im EV8AQ160 lässt sich jeder Kanal fein genug regeln (der Vollausschlag ist mit einer Genauigkeit von einem Fünftel LSB regelbar), so dass die Behebung relativer Verstärkungs- Fehler keine digitale Nachbearbeitung erfordert. Da wie bei der Offset-Einstellung alle vier A/D-Wandler-Cores denselben Fehler sehen, hat der absolute Fehler des externen Vorverstärkers oder Front-Ends keinen Einfluss auf den Interleaving-Vorgang.

Jobangebote+ passend zum Thema

Phasenabgleichsfehler

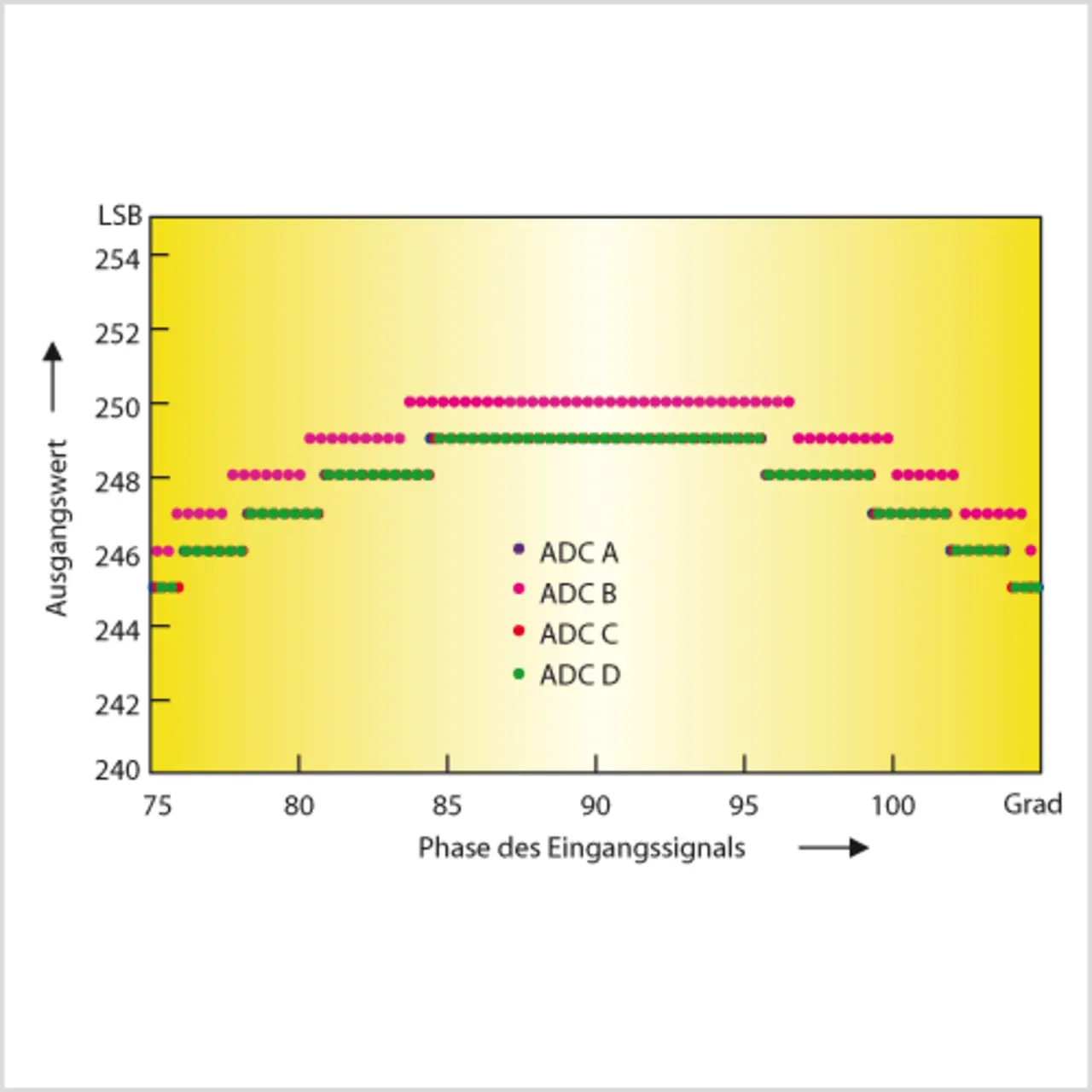

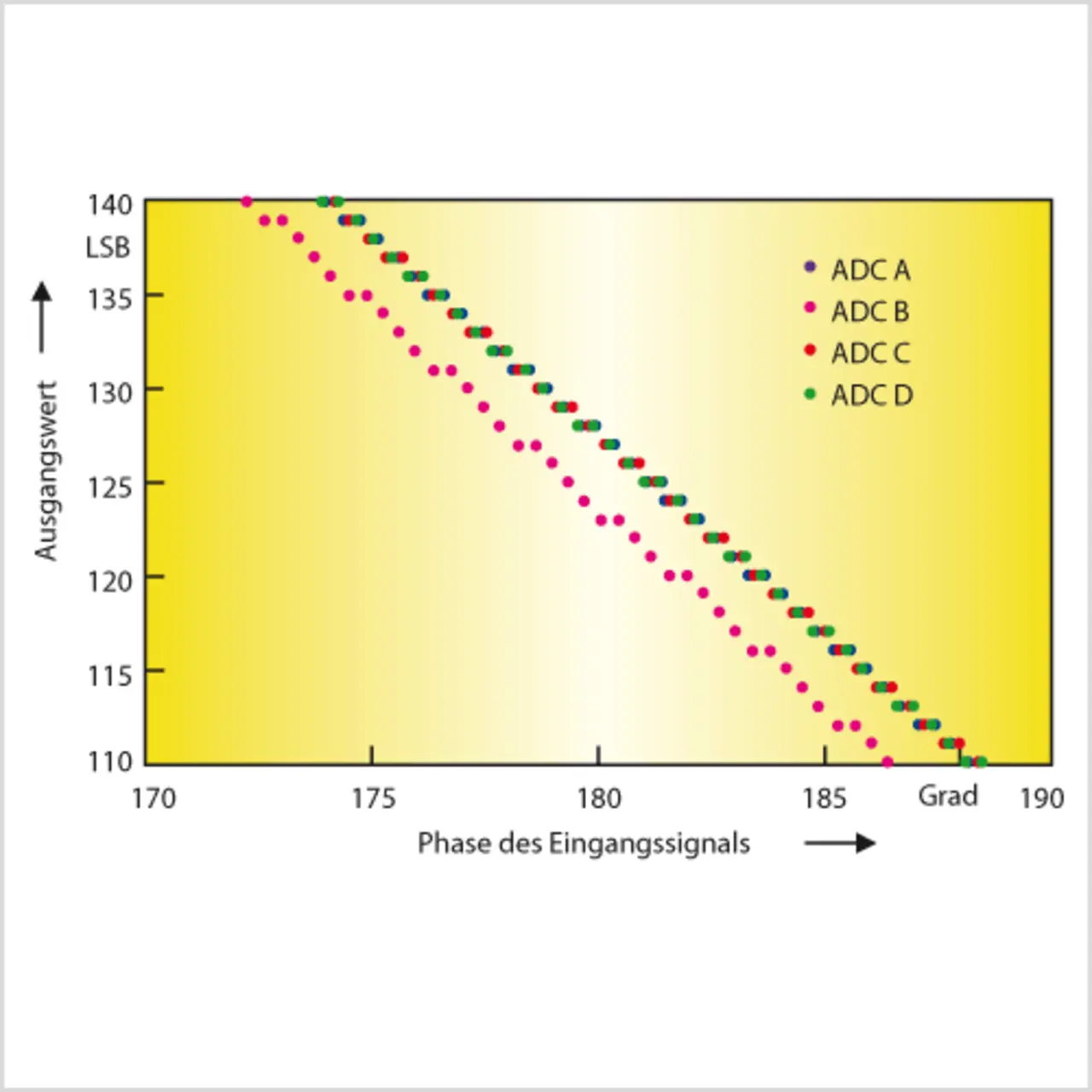

Eine weitere systematische Fehlerquelle beim Interleaving sind Fehler beim Phasenabgleich, also Abweichungen von der idealen Phase der Takte individueller A/D-Wandler. Theoretisch sind die Abtastzeitpunkte gleichmäßig auf dem Phasenkreis verteilt, doch ist dies wegen physikalischer Einschränkungen nicht realistisch. Systematische Taktphasenfehler einzelner A/D-Wandler wirken sich auf das Wandlungsergebnis aus. Bild 3 zeigt Auswirkung einer Phasenabweichung im Takt des B-Kanals um 1% auf einem nach dem Interleaving-Verfahren arbeitenden 8-bit-A/D-Wandler, wobei die einzelne OSR nahe bei 2 liegt.

Die Anfälligkeit für Phasenabgleichsfehler steigt, wenn die OSR abnimmt. Die Auswirkung wird ermittelt, indem die Taktphasenfehler durch die Überabtastrate (OSR) der einzelnen A/D-Wandler geteilt werden. Deshalb bringt die Verschaltung vieler „langsamer“ A/D-Wandler starke Einschränkungen der Phasenkalibrierung mit sich. Entsprechend ist es oft besser, eine kleinere Anzahl angemessen schneller A/D-Wandler zu verwenden. Die Phasenangleichung lässt sich entweder auf Systemebene auf analoger Seite durchführen oder auf der digitalen Seite im DSP. Da viele Spezialfunktionen der Einfachheit halber nicht in den A/D-Wandlern implementiert werden, ist eine Angleichung auf analoger Seite sehr mühsam. Der DSP dagegen berechnet Datenpunkte zur „Idealzeit“ durch Interpolation zwischen Messpunkten und verarbeitet diese dann. Dies erzeugt einen gewaltigen digitalen Overhead.

Um den digitalen Overhead zu vermeiden, muss die Phase sehr präzise im analogen Bereich eingestellt werden: Damit der Effekt in der rekonstruierten Wellenform nicht auffällt, müssen die Phasenfehler geteilt durch den OSR des schnellsten zu wandelnden Signals multipliziert mit der Zahl der quantisierten Level deutlich kleiner als 1 sein. Für eine 8-bit-Wandlung mit individuellem OSR von 2 (jeder A/DWandler arbeitet also in der ersten Nyquist-Zone) müssen die einzelnen Phasenfehler also deutlich unter 1 / (2π x256 / 2) Zyklen oder 0,45° liegen. Bei einem Takt von 1 GHz und einem 500-MHz-Eingangssignal sollte der Fehler des Abtastzeitpunkts unter 1,24 ps liegen. Auch hier ist die Spektralsignatur selbst bei kleinen Phasenabweichungen sichtbar, da es sich um ein deterministisches Phänomen handelt, dessen Energie in einem Frequenzbereich konzentriert ist. Phasenanpassung und Taktverteilung sind auf Systemebene immer ziemlich heikel.

Beim EV8AQ160 wurde das gelöst, indem das Interleaving der vier Cores über einen einzigen externen Taktgeber mit doppelter Geschwindigkeit erfolgt. Jeder interne Taktgeber lässt sich digital per SPI kontrolliert in Schritten von etwa 120 fs einstellen. Außerdem verringert der externe Taktgeber mit doppelter Geschwindigkeit den zusätzlichen Jitter des A/D-Wandlers, da der Takteingangspuffer die steileren Flanken „sieht“. nterleaving mehrerer verschiedener Chips kann aufgrund des unterschiedlichen Wärmemanagements die Rekalibrierung des Offsets bei Änderungen der Systemtemperatur erforderlich machen. Verknüpft man die zwei oder vier Kanäle des EV8AQ160, so ist dies dank der Temperaturüberwachung der vier A/D-Wandler auf einem Chip nicht notwendig.

INL-Fehlanpassungen

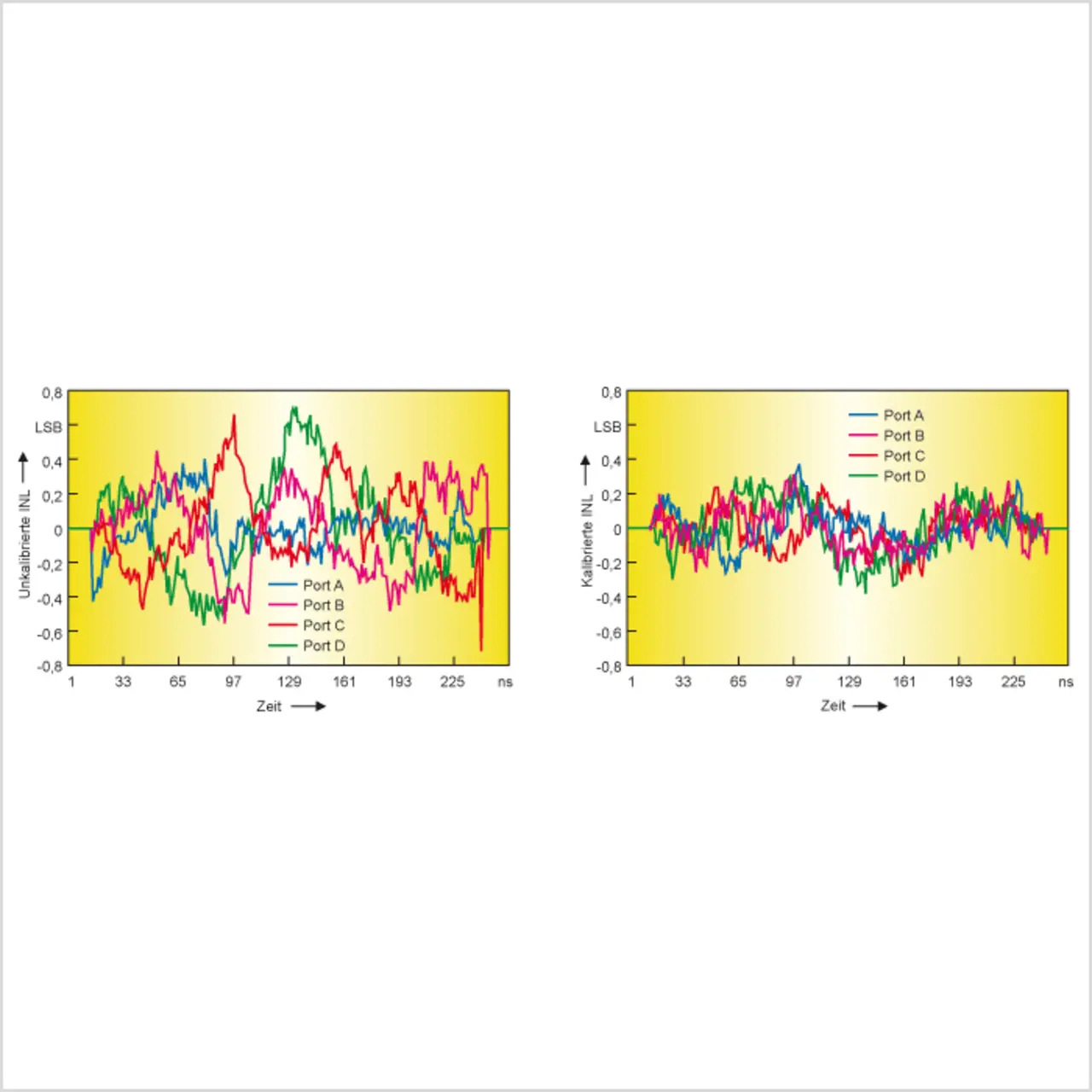

Die letzte mögliche Ursache für deterministische Fehler beim Interleaving ist die INL-Fehlanpassung zwischen den Kanälen. Die Nachteile der INL von mehreren A/D-Wandlern sind dieselben wie bei einem einzelnen schnellen A/D-Wandler. Tatsächlich hat die Verschränkung von m A/D-Wandlern unter dem Gesichtspunkt der gesamten INL sogar Vorteile, da jeder A/DWandler ein 1/m beiträgt und sie sich so nivelliert. Folglich kann der SFDR von m Interleave-A/D-Wandlern besser sein als der von einem A/D-Wandler, da jeder A/D-Wandler auch ein 1/m der Energie liefert und es so wahrscheinlich ist, dass die Spektren von individuellen INL-Profilen nicht übereinstimmen. Die Nachteile zeigen sich allerdings bei rekonstruierten Signalen und im Grundrauschen. INL lässt sich als code-abhängiger Offset betrachten, dementsprechend wirken sich individuelle INL-Fehlanpassungen zwischen A/D-Wandlern direkt auf das rekonstruierte Signal aus.

INL ist im Wesentlichen eine statistische Größe, die vom Abgleich der Komponenten in der (den) ersten Stufe( n) des Quantifizierers herrührt. Die INL-Amplitude lässt sich bereits vor der Fertigung vorhersagen, wenn die verwendeten Bauteile bekannt sind. Wobei das tatsächliche, zufallsbestimmte Profil nicht vorher bestimmt werden kann. Wenn das Signal genügend Zeit hat, den Quantifizierer zu durchlaufen, ist das INL-Profil eines Quantifizierers gegen die Eingangs- und Taktfrequenz ziemlich stabil. Wird ein quasi-statisches Verhalten vorausgesetzt, lässt sich dies mit Hilfe eines Front-End- T/H (Track/Hold) vor jedem Quantifizierer umsetzen.

Aus diesem Grund zählt die INL-Problematik zu den deterministischen Phänomenen, denn vom Gesichtspunkt der Anwendung ist sie tatsächlich deterministisch. So ist es möglich, die INL im analogen Teil zu verbessern, indem zur INL-Kalibrierung digital gesteuerte Offsets an kritischen Punkten der ersten Stufe(n) eingeführt werden, um den „natürlichen“ Offset, der vom Komponentenabgleich herrührt, zu kompensieren. Auf digitaler Seite ist das ebenfalls durch eine Look-Up-Tabelle im DSP möglich. Beim Interleaving sollte jeder einzelne A/D-Wandler über seine eigene Look-Up-Tabelle verfügen. Dies funktioniert allerdings nur, wenn nicht zu viele A/D-Wandler verbunden werden.

Beim Interleaving vieler A/D-Wandler in Echtzeit-Anwendungen ist das nicht möglich. Der EV8AQ160 mit vier 8-bit-A/DWandlern bringt per SPI digital regelbare INL-Einstellmöglichkeiten mit, was es ermöglicht, die INL jedes einzelnen A/D-Wandlers bis auf ±0,3 LSB zu reduzieren, also unter das thermische Grundrauschen. Anspruchsvolle Anwendungen benötigen daher keine Look-Up-Tabelle für die INL-Verbesserung im DSP, was das Design vereinfacht. Bild 4 zeigt die individuelle INL der vier Kanäle des EV8AQ160 vor und nach der Kalibrierung.

Statistische und zufällige Fehler

Einige Fehlerquellen sind nicht deterministisch und lassen sich nicht mit einer deterministischen Lösung beheben. Sie hängen mit thermischem Rauschen oder Jitter zusammen, doch können einige Vorsichtsmaßnahmen beim Entwurf des A/D-Wandlers oder im Systemdesign ihre Auswirkungen reduzieren. Für jeden A/D-Wandler lässt sich das Rauschen als zufällig hinzugefügter Offsetfehler bei jeder Abtastung betrachten. Ebenso kann der zeitliche Jitter jedes A/D-Wandlers als zufällig hinzugefügter Phasenfehler bei jeder Abtastung beschrieben werden. Das Rauschen jedes einzelnen A/D-Wandlers trägt zum Gesamtrauschen des Gesamt-A/D-Wandlers bei und der Takt-Jitter jedes A/D-Wandlers zum Gesamtjitter des Gesamt-A/D-Wandlers. Daraus folgt, dass die Jitter-Bedingungen für die Takte von Interleave- A/D-Wandlern genauso strikt sind wie jene eines schnellen A/D-Wandlers. Dementsprechend steigt in einem Interleave- A/D-Wandler-System die von den Takt-Treibern aufgenommene Leistung linear mit der Zahl der A/DWandler, obwohl jeder einzelne A/DWandler mit geringerem Takt arbeitet. Der Jitter in einem Pufferspeicher hängt ab vom Eingangsrauschen geteilt durch die Flankensteilheit am Eingang, weswegen die Flanken langsamer Takte ebenso steil sein müssen wie die eines schnellen Taktes. Deshalb ist Interleaving im großen Stil keine gute Lösung, wenn eine hohe Auflösung erreicht werden soll. Eine Möglichkeit, Jitter und Taktgenauigkeit eines Interleave-Systems im Griff zu behalten, erfordert einen externen Front-End-T/H (Track/Hold) bei voller Abtastrate des Systems; jeder einzelne A/D-Wandler muss dann die Ausgabe dieses T/H resampeln – häufig keine praktikable Lösung:

- Derartige Bauteile sind oft schwer verfügbar.

- Es wird ein zusätzliches thermisches Rauschen erzeugt.

- Es ist eine komplizierte Verteilung der Ausgabe des T/H an alle A/DWandler erforderlich.

- Sie weisen eine hohe Energiebilanz auf.

Eine andere Lösung des Problems ist es, eine geringe Zahl angemessen schneller A/D-Wandler zu verknüpfen, deren Front-Ends hochwertig genug sind, dass kein externer T/H nötig ist. Soll sich ein derartiges A/D-Wandler- System möglichst wie ein äquivalenter Hochgeschwindigkeits-A/D-Wandler verhalten, gilt es im ersten Schritt, die unkorrelierten Rausch- und Jitterquellen zwischen den verschiedenen A/DWandlern ausfindig zu machen. Grund dafür ist, den Takt- und den analogen Eingangspfad so lange wie möglich für alle A/D-Wandler gleich zu halten. Interleaving auf Chip-Ebene ist natürlich viel einfacher als auf der Systemebene.

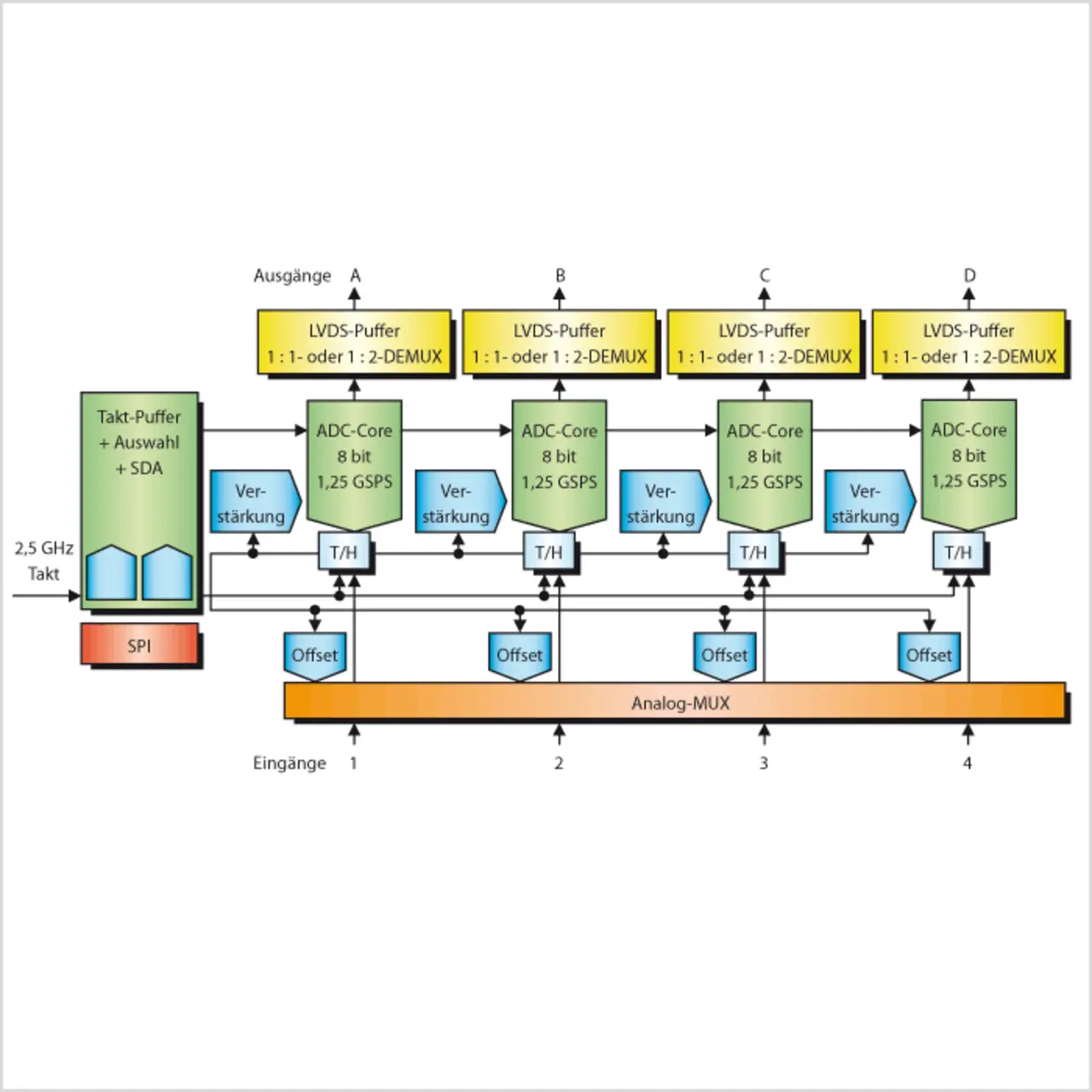

Darüber hinaus müssen die Temperaturen der einzelnen A/DWandler so weit wie möglich im Auge behalten werden, andernfalls muss das System viel öfter kalibriert werden als wünschenswert. Auch dies ist auf Chip-Ebene viel einfacher. Bei der Quad-/D-Wandler-Plattform EV8AQ160 wurden all diese Aspekte berücksichtigt und der vom Interleaving erzeugte Overhead auf dem Chip untergebracht. Eine eingebaute, per SPI gesteuerte Kreuzschaltung erlaubt es, die vier Cores mit einem einzigen differenziellen Analogeingang zu betreiben (Bild 5). Ebenfalls auf Chip-Ebene wird die Taktverteilung beim Verknüpfen von zwei oder vier Cores aus einem externen Taktgeber gesteuert, der mit der doppelten Abtastrate arbeitet und über SPI angesteuert wird. Das erleichtert den Umgang mit dem internen Jitter und vereinfacht die interne Taktverteilung in den drei möglichen Konfigurationen (kein Interleaving, zweifaches Interleaving oder vierfaches Interleaving), was optimierten Jitter und optimierte Energieverteilung zur Folge hat. Verstärkung, Offset und Phase jedes einzelnen A/D-Wandlers des EV8AQ160 lassen sich digital per SPIgesteuertem 8-bit-D/A-Wandler einstellen. In jedem Fall ist der Einstellungsschritt fein genug, dass die Ergebnisse in der Interleaved-Betriebsart nahe an jenen im Nicht-Interleaved- Modus sind.

François Bore

studierte Elektrotechnik am California Institute of Technology, wo er 1989 seinen M.Sc. erhielt. Er begann 1990 seine berufliche Karriere bei Thomson CSF Semiconducteurs Spécifiques (jetzt e2v semiconductors), wo er u.a. Hochgeschwindigkeits- Wandler in Bipolar-, SiGe- und BiCMOS-Technologien entwickelt. 2003 führte er den ersten Single-Core-10-bit-A/D-Wandler mit 2,2 GSamples/s und 2008 den ersten Multi-Core-10-bit-5-GSpamples/s-A/D-Wandler ein. Er hält diverse Patente im Bereich der A/D-Wandler.

bdc@e2v.com

- Eine Plattform für die HF- und Messtechnik

- Phasenabgleichfehler und INL-Fehlanpassungen