Kosten für das Packaging senken

Panel Level Packaging: Wann kommt der Durchbruch?

Panel Level Packaging (PLP) verspricht, die Kosten für das Packaging deutlich zu senken. Noch gibt es einige technische Hürden zu nehmen – doch die Chancen stehen gut, dass PLP das Packaging von Halbleitern künftig neu definieren wird.

Bei Panel Level Packaging handelt es sich um eine Advanced Packaging Technik, bei der das Packaging auf rechteckigen Substraten durchgeführt wird. Der Begriff kann allerdings einen weiten Bereich verschiedener Technologien umfassen. Die präzise Definition hängt dann oft vom jeweiligen Kontext ab, in dessen Rahmen per PLP gesprochen wird. Hier soll es vor allem um die Fan-out- und Fan-in-PLP-Prozesse (FO-PLP und FI-PLP) gehen. Dabei wird das Panel als Träger benutzt und es werden Redistribution-Layer (RDL) strukturiert. Zunächst müssen die Substrate gefertigt werden. Sie können aus organischen und keramischen Materialien sowie aus Glas bestehen.

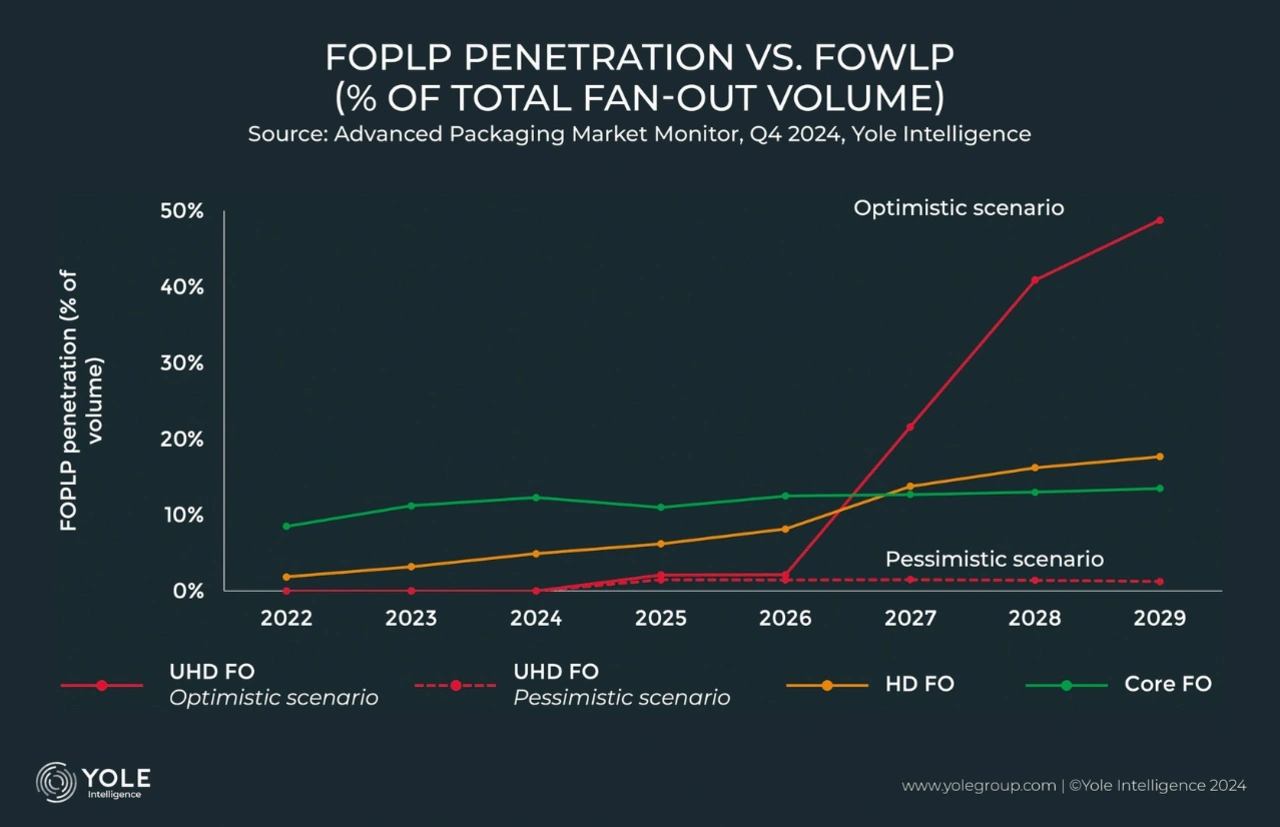

An den PLP-Techniken wird weltweit schon länger gearbeitet. Der Durchbruch lässt allerdings noch auf sich warten. Yole schätzt, dass der PLP-Markt 2023 auf einen Umsatz von 72 Mio. Dollar kam und dass rund 25.000 Panels gefertigt wurden. Das entspricht rund 100.000 Wafern mit einem Durchmesser von 300 mm. Im optimistischsten Scenario nehmen die Analysten der Yole Group an, dass der Umsatz bis 2029 auf über 900 Mio. Dollar steigen wird. Das entspräche 150.000 Panels.

Hauptvorteil PLP vs. WLP

Der Hauptvorteil von PLP gegenüber dem Wafer-Level-Packaging (WLP) besteht darin, dass sich über PLP die Kosten für das Packaging reduzieren lassen. Einfach weil die größere Fläche der Panels zu höherem Durchsatz führt, womit es insbesondere für die Fertigung in hohen Stückzahlen vorteilhaft ist. Außerdem verbessert die Rechteckform die Effizienz der Produktion, speziell für größere Gehäuse. Mit PLP lassen sich auch existierende Maschinen für die Fertigung von IC-Substraten, Leiterplatten und LCD-Equipment nutzen. Das sollte dazu führen, dass sich die erforderlichen Investitionen reduzieren und die Entwicklungskosten verkürzen ließen.

Bisher stehen den zahlreichen Vorteilen, die das PLP bringt, zahlreiche technische und wirtschaftliche Probleme gegenüber, die der Einführung in die reale Fertigung immer noch entgegenstehen. Hohe Investitionen sind erforderlich, um die Linien für die PLP-Produktion zu entwickeln und aufzubauen – die sich nur rechnen, wenn sie in hohen Volumen gefertigt werden kann. Für kleine Packages, die in niedrigen Stückzahlen gefertigt werden, dürfte WLP weiterhin die Produktionstechnik der Wahl bleiben. Das wiederum begrenzt das Potenzial von PLP. Überdies erreicht PLP noch nicht die gleiche Auflösung wie WLP. Während die Fortschritte bei den Lithografiegeräten jetzt Linien und Space-Resolutions von 2 µm zulassen, bleibt die Wiederholbarkeit in hohen Volumen bei akzeptablen Ausbeuten eine Herausforderung.

Eine weitere Hürde besteht darin, dass neue Materialen und Prozesse qualifiziert werden müssen, was viel Zeit in Anspruch nimmt. Zudem gibt es noch weitere technische Schwierigkeiten zu überwinden. Dazu zählen die Verwölbung (Warpage), die Präzision, mit der die Dies platziert werden, die Prozess-Uniformität, die sich auf die Ausbeute und damit auf die Kosteneffizienz auswirkt. Denn ohne ausreichende Ausbeute können die potenziellen Kostenersparnisse trotz der großflächigen Panels nicht realisiert werden.

Jobangebote+ passend zum Thema

Abwägung der Vor- und Nachteile

Unter Abwägung der Vor- und Nachteile kommt Yole zu dem Schluss, dass PLP immer noch sehr interessant ist, um künftig Kosten zu senken – unter der Bedingung, dass Prozesse und Materialien weiterentwickelt werden, eine gute Ausbeute erzielt wird und eine ausreichende Nachfrage besteht, um die PLP-Fertigungslinien zu füllen.

Unternehmen wie Samsung, PTI, Nepes und ASE (sowie Deca als Technologielizenzgeber) haben in den letzten Jahren bereits mithilfe von PLP-Prozessen gefertigt. Während Samsung PLP für mobile und Wearables-Anwendungsprozessoren einsetzt, konzentrieren sich die anderen Unternehmen auf Anwendungen in kleinen Gehäusen wie PMIC-, HF- und Audiocodec-Bausteine, hauptsächlich für den mobilen Bereich.

Inzwischen sind viele neue Akteure in die Fertigung von Chips mithilfe von PLP-Prozessen eingestiegen und treiben die Innovation mit verschiedenen Technologien voran. Einige dieser Unternehmen konzentrieren sich auf niedrige bis mittlere Segmente, wie Leistungs-ICs, Leistungsmodule, MCUs und RF-IC, sowohl für den Einsatz in Geräten für Massen- als auch für Nischenmärkte. Ihr Hauptziel ist es, kosteneffiziente Technologieplattformen für einfache Komponenten zu schaffen, die traditionell auf Mainstream-Gehäusetechnologien wie QFN angewiesen waren. In diesem Bereich hat PEP eine Technologielizenz entwickelt, die auf diesen Gehäusetyp abzielt, mit Innolux, SiPLP und STMicroelectronics als Kunden. In ähnlicher Weise hat Deca die neue Plattform »MD-QFN« gerstartet, die für den gleichen Anwendungsbereich bestimmt ist. Weitere Unternehmen wie AOI Electronics, ECHINT, Amkor, Huatian und andere entwickeln ebenfalls aktiv ihre eigenen PLP-Technologien. Diese starke Zunahme der Aktivitäten erweitert den Anwendungsbereich von PLP und eröffnet neue Möglichkeiten für die gesamte Branche.

Ein weiterer wichtiger Trend ist der Einsatz von PLP für High-End-Anwendungen, wobei HD FO, UHD FO, RDL und Mold- oder Glas-Interposer zum Einsatz kommen. Ziel ist es, große Gehäuse und Systems-in-Package (SiP) kosteneffizienter zu asseblieren. Angesichts der steigenden Nachfrage nach größeren Dies, Chiplets und heterogener Integration gewinnen Lösungen auf Panel-Ebene im Bereich HPC und generativer KI an Bedeutung. Die Silizium-Interposer-Technologie hat ihre Grenze der Reticle-Größe erreicht, was zu einer Verlagerung hin zu organischen Interposern für größere Gehäusegrößen geführt hat. Weil jedoch nur eine begrenzte Anzahl an großen Gehäusen auf einen Wafer passt, wird das Panel-Level-Packaging zunehmend als praktikable Alternative für diese Anwendungen angesehen.

Etablierte PLP-Anbieter wie PTI, Samsung und ASE sowie Newcomer wie Amkor, Innolux, Echint, Rapidus, Silicon Box und TSMC haben diesen Trend aufmerksam verfolgt und mit der Entwicklung von PLP-Technologien für große, hochwertige Fan-out-Gehäuse begonnen. Vor allem die Ankündigung von TSMC, aktiv an der Entwicklung von PLP zu arbeiten, hat die Aufmerksamkeit der Branche auf sich gezogen und die weiteren Entwicklungsbemühungen beschleunigt. Die Analysten der Yole Group gehen davon aus, dass die Technologie von TSMC innerhalb der nächsten drei Jahre entwickelt werden kann. Sollte dies der Fall sein, könnte dies einen Wendepunkt darstellen, der weitere Maschinen-, Material-, Substrat- und sogar Gehäuselieferanten dazu veranlasst, sich auf eine beschleunigte Einführung von PLP zu konzentrieren.

Zusammenfassend lässt sich sagen, dass eine große Welle von PLP-Akteuren im Anmarsch ist. Von einfachen Fan-out-/Fan-in-Technologien bis hin zu hochwertigen 2,5D-Interposern und möglicherweise sogar Glas werden viele neue Technologieplattformen verfügbar sein, die die Lieferkette komplexer machen. Angesichts steigender Investitionen und wachsender Nachfrage ist PLP in der Lage, das Packaging von Halbleitern neu zu definieren.

Wenn die Herausforderungen gemeistert werden können und PLP zu einer wirklich kosteneffizienten Plattform wird, könnte es endlich erfolgreich sein.