Industrielle Kommunikation

Schnell mit RS-485

Fortsetzung des Artikels von Teil 1

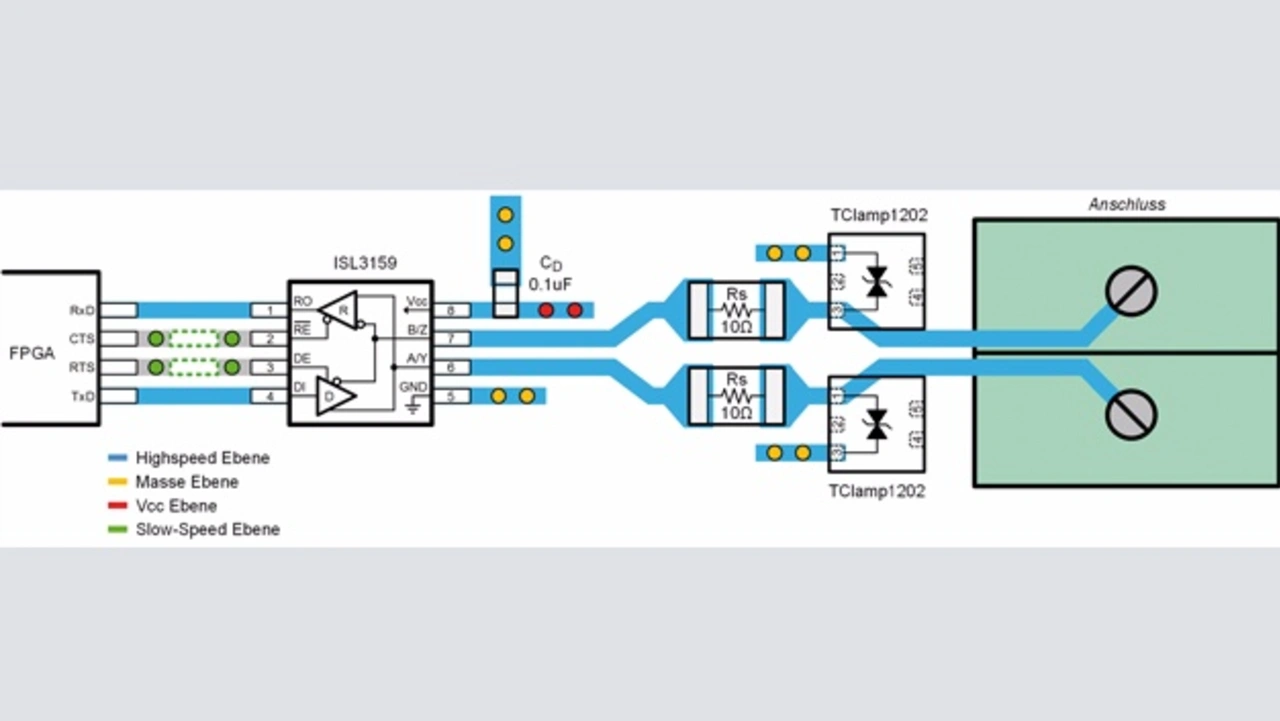

Design eines RS-485-Busknotens

Bild 2 beschreibt einen Busknoten, der aus dem Transceiver, einem FPGA-basierten Controller, überspannungsfesten Widerständen und Überspannungsbegrenzern für Blitzschutz besteht. Die Anschlussbelegung des Transceivers vereinfacht das Design, indem sich die Busanschlüsse (A/Y, B/Z) auf einer Seite des ICs befinden und die Single-Ended-Datenleitungen (DI, RO) sowie die Steuerleitungen (DE, RE) auf der anderen Seite. Um elektromagnetische Störungen (EMI) zu minimieren, kommen Übertragungsleitungen mit kontrollierter Impedanz zum Einsatz. Auf der Bus-Seite muss die differenzielle Impedanz der Busleitungen der charakteristischen Impedanz des Übertragungsmediums entsprechen (100 Ω oder 120 Ω). Auf der Steuerseite wird die Leitungsimpedanz der Single-Ended-Leitungen meist auf 50 Ω eingestellt.

In einem einfachen Busknoten, der aus einem Transceiver und Controller besteht, lassen sich Leitungen mit kontrollierter Impedanz leicht umsetzen, indem der Anwender die Leitungslängen, -breiten, -höhen und den Leitungsabstand sorgfältig festlegt. Hinzu kommt eine enge elektrische Kopplung mit einer Bezugsebene, z. B. Masse oder Versorgung, die eine niedrige Induktivität aufweist.

Die Länge der Leiterbahnen zum Anschluss des Controllers und Transceivers sowie die differenziellen Signalpfade zwischen dem Transceiver und dem Kabelstecker lassen sich nach der Gleichung (1) berechnen.

(1)

Dabei sind LTrace die Leiterbahnlänge, tr die Anstiegszeit des Treibers, v die Signalgeschwindigkeit als Prozentsatz von c und c die Lichtgeschwindigkeit (3 × 108 m/s). Bei jeder Verbindung sollte die elektrische Länge kürzer als 10 Prozent der Anstiegszeit des Treiberausgangs sein.

Bei einer Single-Ended-Leitung dicht über der Masseebene, wie es für den Anschluss des Controllers und Transceivers empfohlen wird, beträgt die relative Signalgeschwindigkeit v 56 %. Mit der Anstiegszeit tr des ISL3159E von 2 ns berechnet sich die maximale Leiterbahnlänge zu 33 mm. Die Leitungslänge vom Transceiver zum Kabelstecker basiert auf der relativen Signalgeschwindigkeit für Leiterbahnen auf einem Standard-FR4-Substrat, die 40 % beträgt. In diesem Fall beträgt die berechnete maximale Leiterbahnlänge 24 mm.

Die Blitzschutz-Komponenten in Bild 2 erschweren das Design. Ein Field-Solver-Softwaretool hilft dabei, den erforderlichen Aufbau der Leiterbahnen zu ermitteln. Damit lassen sich die charakteristische Impedanz, die Signalgeschwindigkeit, das Übersprechen und die differenzielle Impedanz berechnen. Anwender können damit nahezu jeden beliebigen Aufbau evaluieren. Neben den erstrangigen Werten wie Leiterbahnbreite, dielektrische Dicke und Dielektrizitätskonstante müssen auch nachrangige Werte wie Leiterbahndicke, Lötmaske und Leiterbahn-Rückätze berücksichtigt werden.

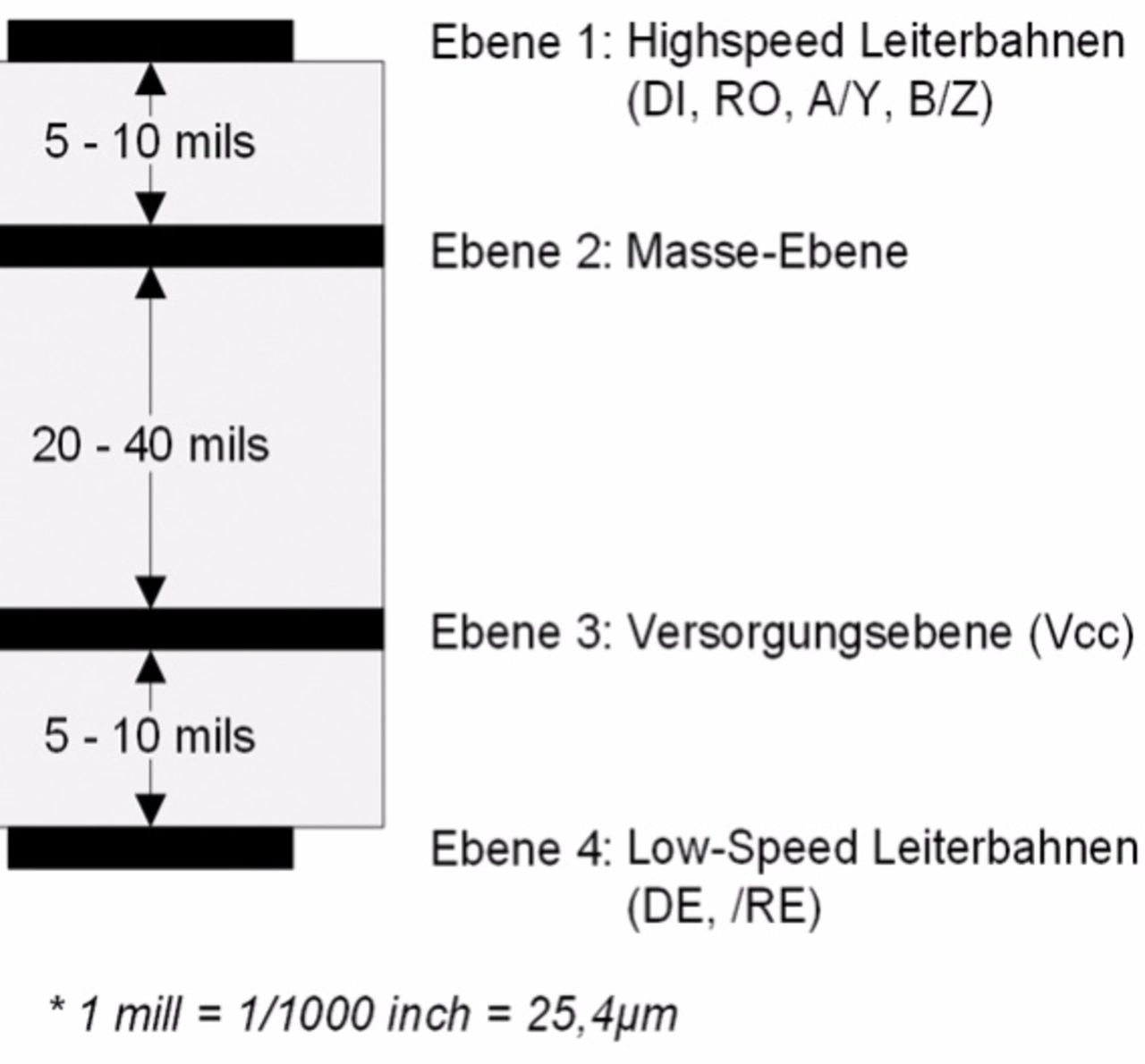

Bezüglich des Leiterplattendesigns sind mindestens vier Ebenen erforderlich, um die Störaussendung zu minimieren. Die Ebenen sollten übereinander angeordnet sein (Bild 3). Die Highspeed-Signalebene befindet sich oben, die Masse- und Versorgungsebene darunter, und die Steuersignalebene auf der Unterseite. Das Routing der Highspeed-Leiterbahnen auf der obersten Ebene verringert die zusätzliche Komplexität und Induktivität, die beim Hinzufügen von Vias (Durchkontaktierungen) auftritt. Damit sind saubere Verbindungen vom Busstecker zu den Transceiver-Busanschlüssen und von den Highspeed Single-Ended-Datenleitungen des Transceivers zum Knoten-Controller garantiert. Eine Masse-Ebene unterhalb der Highspeed-Signalebene sorgt für kontrollierte Impedanzen auf internen Übertragungsleitungen und bietet für den Rückstrom einen niederinduktiven Pfad. Wird die Versorgungsebene unterhalb der Masse-Ebene platziert, entsteht eine zusätzliche HF-Bypass-Kapazität. Das Routing der langsameren Steuersignale (Enable) in der untersten Ebene erhöht die Flexibilität. Diese Signalverbindungen bieten einen Spielraum, um Diskontinuitäten wie Vias zu tolerieren. Die Trennung eliminiert nahezu das Übersprechen von den Highspeed-Datenleitungen.

- Schnell mit RS-485

- Design eines RS-485-Busknotens

- Designrichtlinien für den RS-485-Knoten