Leistungselektronik

Systemdesign für SiC-JFET-Halbbrücken-Module

Fortsetzung des Artikels von Teil 1

Einflussfaktoren auf das parasitäre Einschalten

Ein Vergleich der Stromspitze beim Einschalten des unteren JFET bei Vorstrom in der Last und bei verschiedenen Gate-Widerständen im Ansteuerkreis des unteren Schalters zeigt Bild 6. Der Gate-Widerstand des oberen Schalters ist dabei fest auf 0 Ω gelegt. Mit Erhöhen des Gate-Widerstandes reduziert sich das dUDS/dt der Drain-Source-Spannung von 8 kV/µs bei RG = 0 Ω auf 2 kV/µs bei RG = 5,6 Ω. Die Stromspitze und damit das parasitäre Einschalten sinken mit fallendem dUDS/dt. Die Schaltverluste (Eon + Eoff + Erec) steigen dabei von 62 mJ auf 115 mJ an. Ein Ausbremsen des SiC-JFETs ist damit nicht der beste Weg, um die Wirkung des parasitären Einschaltens zu reduzieren.

In Bild 7 ist der Stromverlauf am unteren Schalter bei Vorstrom in der Last dargestellt, jedoch unter Variation der Impedanz im Gate-Kreis des oberen JFET. Im ersten Experiment wurde der Standard-Gate-Widerstand von 0 Ω durch Widerstände höheren Wertes ersetzt. Im zweiten Experiment wurde die Streuinduktivität im Gate-Kreis künstlich durch Einbau eines 10 cm bzw. 20 cm langen Kabels erhöht. Beide Experimente zeigen, dass die Zunahme der Impedanz im Gate-Kreis den Effekt des parasitären Einschaltens verstärkt.

Die Wirkung der negativen Vorspannung im Aus-Zustand auf das parasitäre Einschalten zeigt Bild 8. Hier wurde die Gate-Source-Spannung des oberen Schalters von –22 V schrittweise bis auf –17 V erhöht und so der Abstand zur Abschnürspannung (–14 V) variiert. Das dUDS/dt des unteren Schalters bleibt konstant. Mit Erhöhen der Spannung nimmt das parasitäre Einschalten zu. Daher kann als eine Maßnahme zur Reduzierung der Wirkung des parasitären Einschaltens die Wahl einer möglichst geringen Spannung im Auszustand gelten. Beim SiC-JFET ist dieses aber durch den Punch-Through der Gate-Source-Diode auf ca. –22 V limitiert.

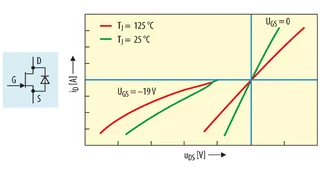

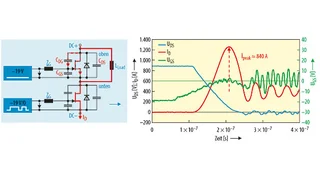

Systemdesign für SiC-JFET-Module

Bei kleinem bzw. keinem Vorstrom schaltet der JFET am schnellsten ein, d.h., die Spannungssteilheit dUDS/dt ist am höchsten. Die hohe Steilheit sollte die größte Rückwirkung auf das Gate im oberen Schalter ergeben. Bei kleinem Vorstrom ist daher der stärkste parasitäre Einschalteffekt zu erwarten. Bild 9 zeigt eine Gegenüberstellung des Einschaltvorganges mit und ohne Vorstrom. Der Vergleich bestätigt die Erwartung hinsichtlich des dU/dt, aber nicht die zum Effekt des parasitären Einschaltens. Denn die Stromspitze und damit das parasitäre Einschalten sind deutlich höher beim Einschalten mit Vorstrom. Eine Analyse der Spannungsverläufe an beiden Schaltern der Halbbrücke beim Einschalten mit Vorstrom zeigt einen deutlichen Unterschied auf (Bild 10). Die Änderungsgeschwindigkeit der Drain-Source-Spannung am oberen Schalter ist mit 26 kV/µs um den Faktor drei größer als am unteren. Dies ist der Grund für das verstärkte parasitäre Einschalten beim Einschalten mit Vorstrom.

Die Ursache für das unterschiedliche dUDS/dt ist in der Wirkung der Streuinduktivität im Leistungskreis begründet. Beim Einschalten mit Vorstrom steigt der Strom ID mit einem hohen dID/dt an. Aufgrund der Streuinduktivität im Zwischenkreis bewirkt das hohe dID/dt einen Einbruch der Spannung über dem Modul. Die Spannungsdifferenz am Drain des unteren JFET zur Zwischenkreisspannung ergibt den Spannungsverlauf am oberen JFET. So wird der Spannungsverlauf am oberen JFET von dID/dt und der Streuinduktivität im Zwischenkreis mitbestimmt. Bezüglich des parasitären Einschaltens zeigt sich die Wirkung der Streuinduktivität aber erst, wenn sich das dID/dt verringert. Der Spannungsabfall über der Streuinduktivität geht zurück und das wirksame dUDS/dt am oberen Schalter setzt sich aus dem des unteren Schalters und der Änderung des induktiven Spannungsabfalls zusammen. Der Zusammenhang wird durch die Formeln (Kasten) beschrieben. Es zeigt sich, dass die Streuinduktivität im Leistungskreis den Effekt des parasitären Einschaltens verstärkt. Zur Verdeutlichung des Effektes ist in Bild 11 eine Gegenüberstellung einer Variation der Streuinduktivität im Leistungskreis dargestellt. Die Streuinduktivität wurde durch Abtrennen von Zwischenkreiskondensatoren erhöht – das dID/dt wurde konstant gehalten. Ausgehend vom Standard-Aufbau mit 25 nH hin zu 43 nH zeigt sich eine Zunahme des parasitären Einschaltens. Zur Minimierung des Effektes des parasitären Einschaltens muss neben der Induktivität im Gate-Kreis auch die Streuinduktivität im Leistungskreis extrem klein sein.

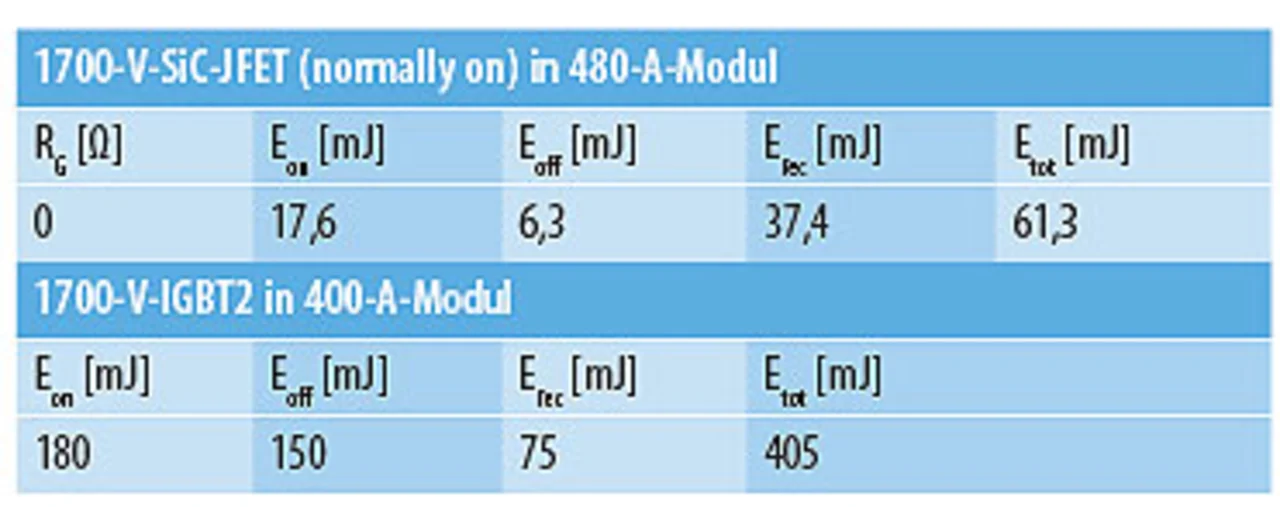

Die Tabelle zeigt einen Vergleich der dynamischen Verluste des 1700-V-SiC-JFET-Demonstrator-Moduls zu einem 1700-V-/400-A-Si-Modul mit schnellem IGBT- und Dioden-Chipsatz. Die Verluste sind um den Faktor sieben kleiner als beim vergleichbaren IGBT-Modul. Der SiC-JFET zeigt somit hervorragende Ergebnisse in Bezug auf die dynamischen Verluste und das, obwohl parasitäres Einschalten auftritt.

Die vorgestellten Ergebnisse verdeutlichen die Wirkung der verschiedenen Einflussfaktoren auf das parasitäre Einschalten. Es wurde gezeigt, dass parasitäres Einschalten nicht nur von den Bauelementeigenschaften, sondern auch von der Wirkung parasitärer Elemente im Leistungs- und Ansteuerungskreis abhängig ist. Um SiC-Bauelemente optimal in schnell schaltenden Anwendungen zu betreiben, ist daher ein allumfassend niederinduktives Design notwendig. Dies bedeutet, dass das Modul selbst, der Leistungskreis und der Ansteuerkreis dahingehend optimiert werden müssen. Das vorgestellte Modulkonzept weist bereits eine sehr geringe Streuinduktivität auf, weitere Optimierungen sind im Ansteuerkreis sowie im modulexternen Leistungskreis zu finden.

Literatur

[1] Rupp, R. et. al.: Strategic Considerations for Unipolar SiC Switch Options: JFET vs. MOSFET. IAS 2007, New Orleans, USA.

[2] Heer, D. et. al.: SiC-JFET in half-bridge configuration – parasitic turn-on at current commutation. PCIM 2014, Nürnberg.

[3] Bayerer, R.; Domes, D.: Power Circuit design for clean switching. CIPS 2010, Nürnberg

Die Autoren

| Dipl.-Ing. Daniel Heer |

|---|

| studierte Elektrotechnik an der Universität Paderborn. Thema seiner Diplomarbeit war die detaillierte Charakterisierung von unterschiedlichen 3,3-kV-IGBT-Varianten. Seit April 2011 ist er in der Vorentwicklung Leistungsmodule bei Infineon Technologies AG in Warstein beschäftigt. Sein Aufgabengebiet umfasst neben der Charakterisierung von Silizium- und Siliziumcarbid-Leistungshalbleiterbauelementen auch die Entwicklung von Leistungshalbleitermodulen. |

| Dr. rer. nat. Reinhold Bayerer |

|---|

| studierte an der Technischen Hochschule Darmstadt (THD) Physik und beendete es 1979 mit dem Abschluss als Dipl.-Ing. (Physik). 1985 promovierte er dort zum Dr. rer. nat. Seit dieser Zeit arbeitet er in der Halbleiterindustrie auf dem Gebiet der IGBT-Module. Er entwickelte zu Beginn eines der ersten IGBT-Module, das er mit einem Vortrag auf der PCI-Konferenz in München 1987 vorstellte. Während der langjährigen Tätigkeit hat er zu Modulkonzepten, Aufbau- und Verbindungstechniken, Treiberkonzepten, Prüftechnik und Applikation beigetragen. Mehrere Publikationen und Patente dokumentieren die Ergebnisse. |

| Dr.-Ing. Daniel Domes |

|---|

| schloss sein Studium der Elektrotechnik in 2003 ab. Während seiner Tätigkeit als wissenschaftlicher Mitarbeiter an der Technischen Universität Chemnitz befasste er sich mit Umrichtersteuerverfahren und dem Einsatz von SiC-Leistungsbauelementen in verschiedenen Umrichtertopologien. 2009 erfolgte die Promotion. Seit 2008 arbeitet er bei der Infineon Technologies AG mit Fokus auf innovative Konzepte rund um die Applikation von Leistungshalbleiterchips. |

- Systemdesign für SiC-JFET-Halbbrücken-Module

- Einflussfaktoren auf das parasitäre Einschalten