Boundary-Scans ohne JTAG-Schnittstelle

Testabdeckung Erhöhen

Nicht alle Halbleiterchips unterstützen Boundary-Scans. Über Emulation lassen sich trotzdem statische Verbindungstests durchführen. Die Testabdeckung erhöht sich damit deutlich.

Effizienter, kleiner, leistungsfähiger. Nirgendwo ist dieser Anspruch stärker ausgeprägt als bei der Umsetzung neuer Elektronikdesigns. Hauptakteure bei den notwendigen Entwicklungsprozessen sind immer leistungsfähigere Prozessoren, Mikrocontroller und FPGAs. Gepaart mit schrumpfenden Packagings bieten sich dem Entwickler enorme Möglichkeiten, um die Funktionsdichte auf der Leiterplatte kontinuierlich zu steigern.

Durch die damit einhergehende Reduktion des physikalischen Zugriffs ergeben sich allerdings auch immer größere Schwierigkeiten: zum einen der Nachweis über die geforderte Fehlerfreiheit beim Test, zum anderen das Gewinnen von verwertbaren Diagnoseinformationen im Fehlerfall. Testsysteme, die während der Fertigung zur Prüfung der bestückten Baugruppen eingesetzt werden, stehen somit vor neuen Herausforderungen. Dazu kommen viele Highspeed-Schnittstellen, die ebenfalls während dieses Prozesses ausreichend und sicher geprüft werden müssen.

Jobangebote+ passend zum Thema

| Typ | Beschreibung |

|---|---|

| »Hardware« IP | Fest im IC integriertes Instrument, gesteuert durch einen standardisierten (z.B. IEEE1149.x, IEEE1687), oder einen proprietären Zugriffsmechanismus. |

| Software IP für FPGA | Per Download in den FPGA (Soft-Macro) instanziertes Test Instrument, welches typischerweise per JTAG-Port gesteuert wird. |

| Software IP für µP | Per Download in den µP aktiviertes Test Instrument (Softwareagent), welcher typischerweise über den Debug-Port gesteuert wird. |

Tabelle 1. Übersicht über die verschiedenen Testinstrument-IP-Typen.

Oft kann nicht mehr auf die bekannten Testressourcen zurückgegriffen werden, wie beispielsweise den statischen Boundary-Scan-Test. Entweder fehlen die dafür notwendigen Strukturen in den ICs oder auch schlichtweg der Zugriff über die JTAG-Signale. Viele Mikrocontroller und Mikroprozessoren nutzen mittlerweile andere Debug-Schnittstellen wie z.B. SWD oder DAP, da diese weniger Pins als das bisherige JTAG-Interface benötigen. Als effizienter Ausweg haben sich Embedded Instruments als Software-IP (Intellectual Property) durchgesetzt. Sie sind sowohl für Prozessorsysteme, als auch für FPGAs verfügbar und bilden das Gegenstück zu fest integrierter Instrumente-IP (Tabelle 1).

Baugruppentest über Software-IP

Soft- und Hardware, die den softwarebasierten IP-Ansatz aus einer Hand unterstützen, sind schon länger etabliert. Durch vorgefertigte und für den Baustein oder das Board konfigurierbare Embedded Instruments wird eine Vielzahl von Testproblemen effizient adressiert. Im Kern stellen diese Embedded-IP-Instrumente funktional arbeitende generische Softwarestrukturen dar, die nur für die jeweilige Testumgebung oder das Board-Design passend konfiguriert werden müssen. Damit lassen sie sich auf fast alle Plattformen und Board-Designs anwenden. Testabläufe für Funktionstests können gezielt optimiert werden oder entfallen ganz, was enorme Entwicklungskosten und Ressourceneinsparungen ermöglicht. Göpel bietet Software-IP für Mikroprozessoren (μP), Mikrocontroller (MCU) und FPGAs an.

Baugruppentest über den FPGA

Moderne FPGAs sind oft SoC-Bausteine (System on Chip), bei denen sowohl der Prozessorteil als auch die Logik des FPGA-Teils eine Rolle spielen. Für solche Systeme ist die »ChipVORX«-Technologie der Softwareplattform »System Cascon« ausgelegt. Über sie lassen sich vorgefertigte funktionale IP-Instrumente in den FPGA laden und passend konfigurieren. Anschließend kann der komplette Test überwacht und ausgewertet werden. Dabei steht die Pin- oder Netzgenaue Fehlerdiagnose für eine einfache Fehlersuche und Behebung im Fokus.

Baugruppentest über μP und MCU

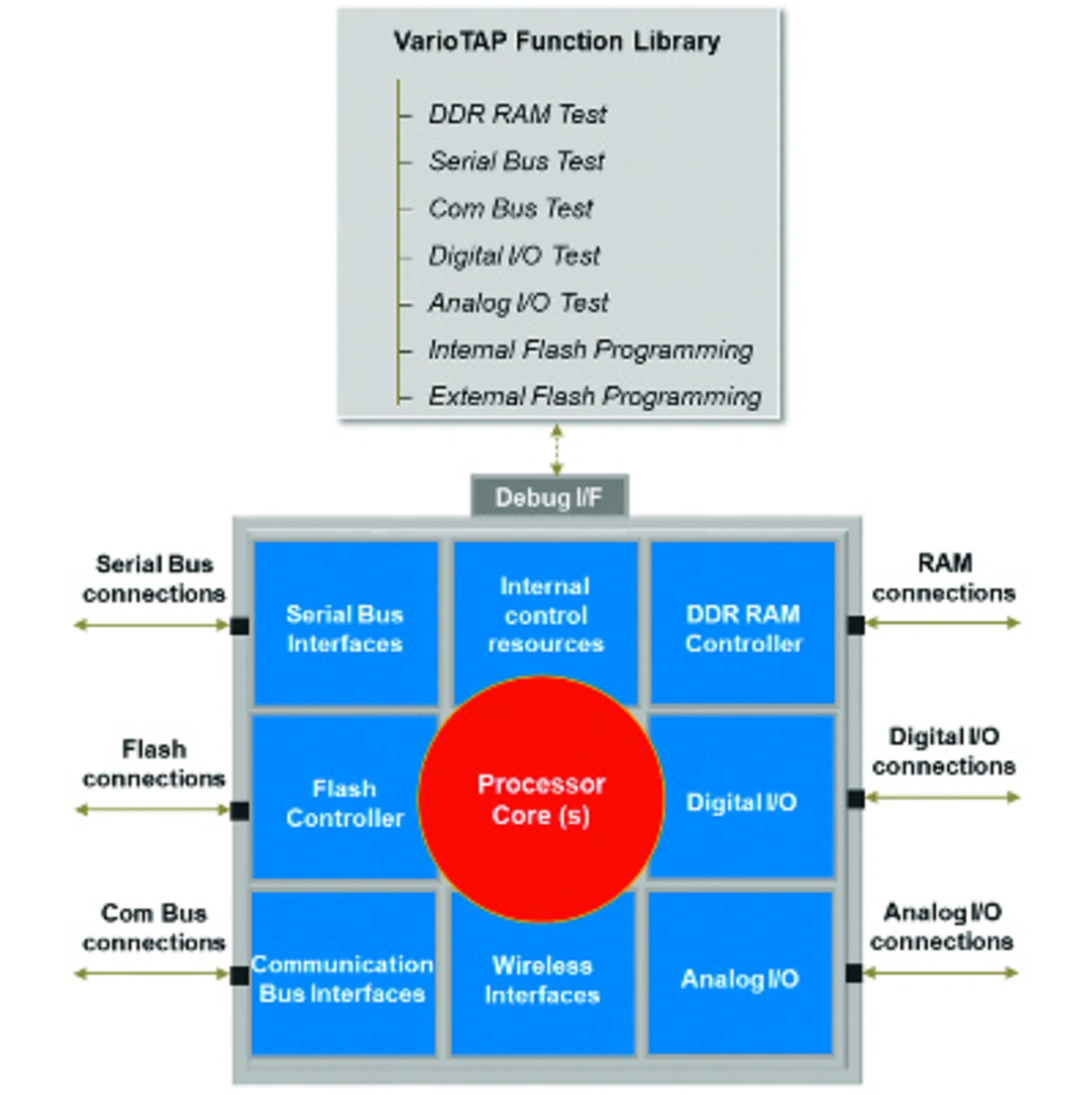

Mikrocontroller und Mikroprozessoren können über eine Technik namens „VarioTAP“ auf Basis von Embedded-IP-Instrumenten für den Baugruppentest eingebunden werden. Die Testabdeckung umfasst statische und dynamische Fehler, z.B. beim Test von DDR-DRAM-Bausteinen (Bild 1). Damit eröffnen diese Testwerkzeuge mit ihren Funktionsbibliotheken die Möglichkeit, ein Produkt über den gesamten Lebenszyklus von der Entwicklung und Fertigung bis hin zur Reparatur von Baugruppen zu begleiten.

- Testabdeckung Erhöhen

- Virtuelle Boundary- Scan-Zellen