Prüfarchitekturen

Die Halbleiter-Testkosten senken

Fortsetzung des Artikels von Teil 1

FPGAs bewältigen die Komplexität von Halbleitern

Eine bereits erwähnte Schwierigkeit, mit der sich Entwickler von Halbleitertests konfrontiert sehen, ist die steigende Komplexität der Chips. Neue Komponenten integrieren mehrere intelligente Subsysteme mit Mixed-Signal- und HF-Funktionen in komplexen SoC- und SiP-Designs (System-in-a- Package). Das macht die Validierung der Subsysteme in diesen Designs noch komplizierter, da kein umfassender Zugriff auf alle Ein- und Ausgänge besteht.

In solchen Fällen muss der Chiptest von einer höheren Ebene – aus der Perspektive des Systemfunktionstests – betrachtet werden, denn Prüfstrategien auf Komponentenebene sind nicht möglich. Infolgedessen müssen Prüfsysteme neben der Möglichkeit, die verschiedenen Signale simultan zu emulieren, noch weitere Funktionen bieten, darunter Mixed-Signal-Messungen sowie die Erfassung und Erzeugung von HF-Signalen. Traditionelle Teststrategien können hier oft nicht mehr mithalten – die Folge: Entwicklungszeit und -kosten für die Erstellung eines funktionierenden Prüfsystems steigen.

Ein typisches Beispiel für die Probleme, die mit dieser erhöhten Komplexität einhergehen, ist die hohe Anzahl von Kommunikationsprotokollen, die moderne Chips beherrschen. Aufgrund der Integration von immer mehr Funktionen müssen auch Methoden für jedes der einzelnen Subsysteme zur Verfügung stehen, die eine Kommunikation mit den entsprechenden Peripherieschnittstellen ermöglichen.

So sind mehr als fünf unterschiedliche Kommunikationsprotokolle auf einem Chip heute nicht mehr ungewöhnlich. Ein neuer Mikrocontroller beherrscht neben universellen I/O-Funktionen auch z.B. Protokolle wie SPI, I2C, CAN sowie UART und bedient Speicherschnittstellen. Standardmäßige vektorbasierte digitale Prüfgeräte (wie bei einem konventionellen ATE-System) reichen oft nicht aus, um alle diese Protokolle zu prüfen, da unter Umständen jede Schnittstelle einen unabhängigen Takt bzw. asynchrone Datenübertragung erfordert.

Jobangebote+ passend zum Thema

Eine leistungsstarke Lösung für den Umgang mit diesen Herausforderungen bieten FPGAs, die auf Datenerfassungskarten mit anwenderdefinierter »Verkabelung« für diese komplexen Testaufgaben eingesetzt werden. FPGAs ermöglichen hier die unabhängige Definition von Kommunikationsparametern und Tests für jedes der Subsysteme mit jeweils der gleichen relativ kostengünstigen Hardware. So kann die Umgebung eines Chips effizient emuliert und damit eine elegantere High-Level-Prüfschnittstelle realisiert werden.

Allerdings können FPGAs auch versteckte Kosten in Form von größerem Zeitaufwand bei der Hardware- und Software-Entwicklung verursachen. Besonders die Integration von FPGAs in Karten mit benutzerdefinierter Verdrahtung setzt für Hochgeschwindigkeitssignale Erfahrung beim Leiterplatten- Layout voraus. Zudem erfordert die Programmierung der FPGAs für diese Tests Fachwissen in einer geeigneten Hardware-Beschreibungssprache.

Aus diesem Grund setzt z.B. Infineon Technologies kommerzielle Standard-FPGA-Hardware und die Software »NI LabVIEW FPGA« ein, um eine Familie von 8-, 16- und 32-bit-Mikrocontrollern zu testen. Da sich LabVIEW FGPA im Vergleich zu traditionellen Hardware-Beschreibungssprachen einen abstrakten grafischen Programmieransatz zunutze macht, konnte Infineon damit bei der Erstellung des Prüfsystems viel Entwicklungszeit einsparen.

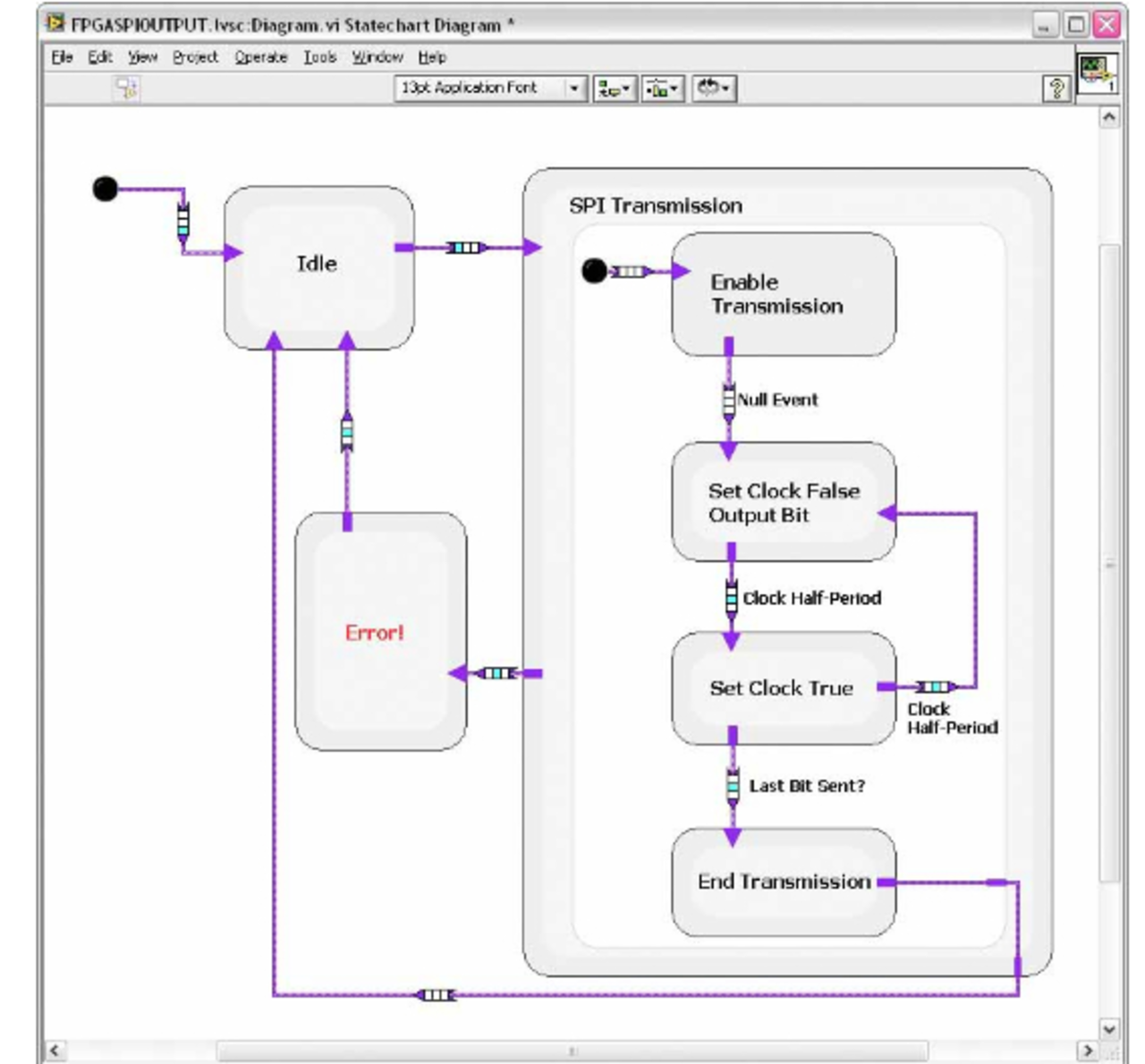

Ein einfaches Beispiel dafür, wie die Software »LabVIEW FPGA« in Kombination mit Standard-Hardware Zeit einspart, ist die Erstellung eines FPGA-basierten SPI-Transceivers (Bild 2).

Bild 3 zeigt ein Zustandsdiagramm, das direkt in LabVIEW FPGA genutzt werden kann, um das SPI-Protokoll zu emulieren. Dieses wird auf verschiedenen PXI-basierten FPGA-Modulen ausgeführt, die I/O-Funktionen bis zu 200 MHz bieten. Deshalb können Entwickler FPGA-basierte Transceiver ohne Leiterplattenentwurf und Fehlerbehebung von Low-Level- HDL-Syntax erstellen und sich stattdessen unmittelbar auf die Erstellung der Tests konzentrieren.

I/O-Vielfalt als Herausforderung für die Ressourcen von Prüfsystemen

Ein letzter Trend, der die Komplexität weiter verschärft, ist die Vielfalt an I/O-Funktionen, die heute implementiert ist. Traditionell erfordern Halbleiter vor allem digitale und DC-Ressourcen für Tests, während auch zusätzliche Mixed-Signal-Tests immer häufiger vorkommen. Technologien wie etwa Micro-Electro-Mechanical- Systems (MEMS) führen diese Entwicklung noch einen Schritt weiter, indem sie die Erzeugung physikalischer Stimuli notwendig machen, z.B. des Schalldrucks bei Mikrofonen, die Ausrichtung von Gyroskopen oder die Bewegung von Beschleunigungsmessern.

Zwar sind spezielle I/O-Optionen auf bestimmten ATE-Plattformen verfügbar, doch sind diese vielfach nur suboptimale Add-ons für bestehende Prüfsysteme, die DC- und digitale Bereiche dieser Geräte überstrapazieren.

Vor kurzem haben Entwickler bei Analog Devices ein neues Produktionsprüfsystem für eine neue Reihe von iMEMS-Geräten erstellt und standen dabei vor ähnlichen Herausforderungen. Da dieses System in einer Produktionsumgebung eingesetzt werden sollte, standen neben der Wahl der passenden Messgeräte für die einzigartigen Messanforderungen auch die Investitionskosten im Vordergrund. Deshalb wurde ein System auf Basis von PXI-Hardware und NI LabVIEW gewählt. So konnten die nötigen Messgeräte genau an die Bedürfnisse des Systems und der Tests angepasst werden.

Zum Einsatz kamen vielfältige PXI-Messgeräte, darunter Hardware zur Erfassung dynamischer Signale mit einem hohen Dynamikbereich für Audiomessungen sowie SMUs für die DC-Charakterisierung. Die Lösung führte zu erheblich niedrigeren Investitionskosten für die Prüfausrüstung (Bild 4) und verringerte zudem die Stromaufnahme.

Das Team von ADI beschrieb den neuen Tester folgendermaßen: »Ein PXI-System ist viel kleiner als ein großer, unhandlicher ATE-Tester, so dass wir nicht so viel teuren Platz in der Produktionsanlage in Anspruch nehmen müssen. Mit PXI können wir genau die Geräte auswählen, die wir brauchen. Das PXI-Rack umfasst nur die notwendigen Messgeräte, ganz im Gegensatz zu großen ATE-Testern, die oftmals viele unnötige Geräte und/oder Kanäle integrieren, welche nur die Kosten in die Höhe treiben.«

Letztlich haben sich kommerzielle Standard-Hardware wie PXI und flexible Software wie NI LabVIEW und LabVIEW FPGA als gut nutzbare Werkzeuge bewährt, mit denen Ingenieure ihre Effizienz wesentlich steigern und dabei Kosten sparen können. Zwar werden neue Halbleiter-Designs auch in Zukunft Herausforderungen darstellen, doch haben Testingenieure mittlerweile bewiesen, dass Prüfsysteme an die individuellen Anforderungen jeder Anwendung angepasst werden können, ohne Kompromisse bei Zeitaufwand oder Budget eingehen zu müssen.

Autor:

| Travis White |

|---|

| ist Produktmanager für modulare Messgeräte bei National Instruments. Sein Verantwortungsbereich liegt hauptsächlich im Management, Marketing und in der strategischen Planung für die Bereiche Schaltmodule, Präzisionsquellen und Präzisionsmessgeräte. Er hat einen Bachelor-Abschluss der Rice University. |

- Die Halbleiter-Testkosten senken

- FPGAs bewältigen die Komplexität von Halbleitern