Programmierbare Logikbausteine

Beschleunigtes Ultraschall

Fortsetzung des Artikels von Teil 2

FPGAs sparen Energie

FPGAs sparen Energie

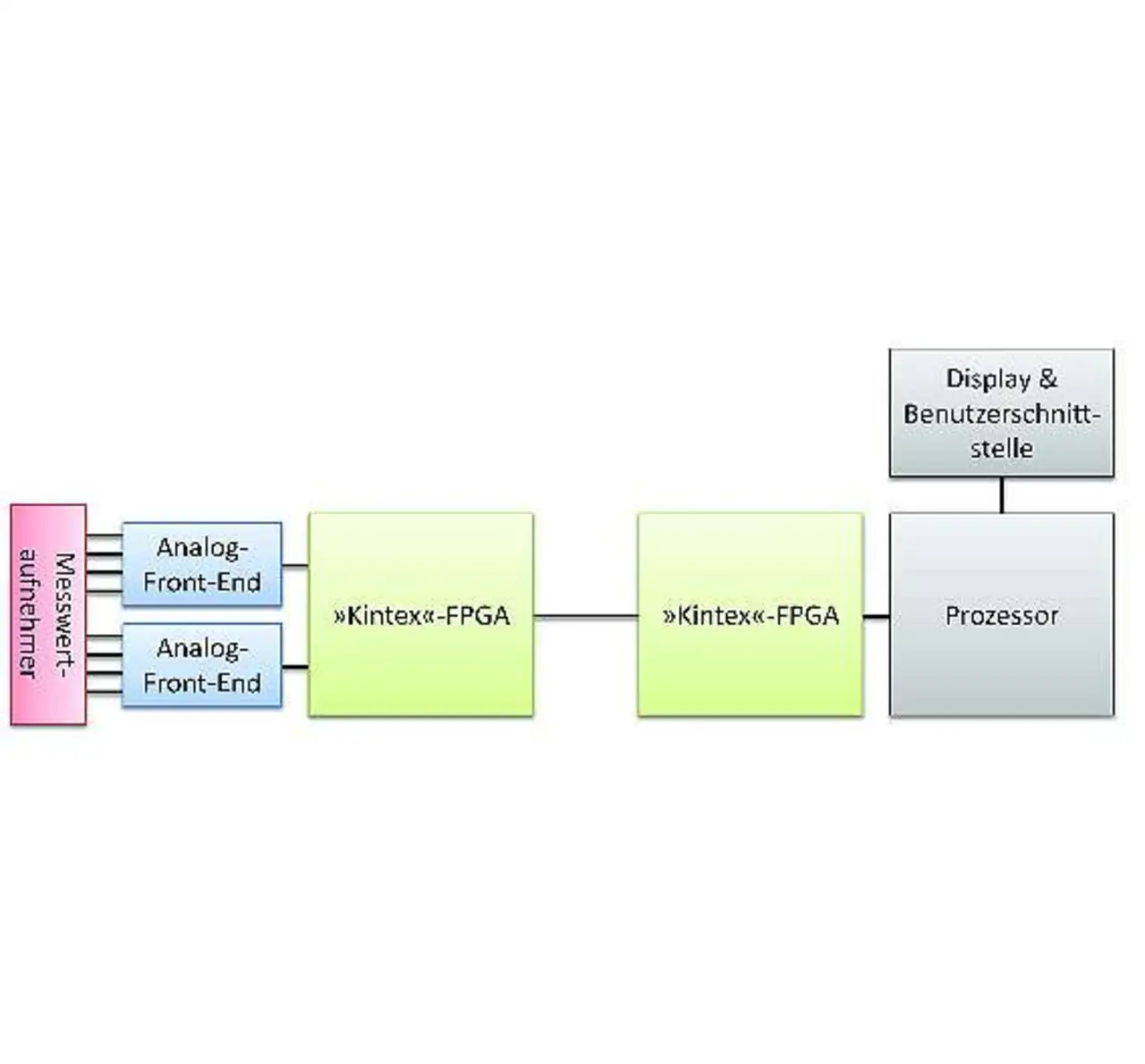

Oft ist der Leistungsverbrauch ein zentrales Thema in der Ultraschall-Bildverarbeitung, besonders bei tragbaren Geräten wegen der eingebauten Batterie. Obwohl der Leistungsverbrauch in einem aus dem Stromnetz versorgten System nicht so entscheidend ist, müssen auch hier thermische Probleme, die mit der Verlustleistung zusammenhängen, und das Management des Power-Zyklus beachtet werden. Ein FPGA, das in 20-nm-Technologie hergestellt ist, wird insgesamt 20 Prozent bis 50 Prozent weniger Leistung verbrauchen (dynamisch, statisch und I/O kombiniert) verglichen mit einem in 28-nm-Technologie. Die Einsparungen in der dynamischen und statischen Power werden sowohl im System-Front-End als auch -Back-End zu einem Vorteil, da die Strahlformung und die Bildrekonstruktion sehr rechenintensive Prozesse sind (Bild 3). Darüber hinaus wird eine Reduzierung der Verlustleistung von Transmittern und I/Os um 30 Prozent ein Vorteil beim Einsatz von FPGAs für die Übertragungsfunktionen in Ultraschallgeräten sein.

Designablauf verkürzt Entwicklungszeit

Die Technik ermöglicht auch verschiedene Power-down-Modi für unterschiedliche Funktionsblöcke, um den Systemwirkungsgrad zu optimieren. Die verringerte Verlustleistung eines 20-nm-FPGAs, kombiniert mit »intelligentem« Power-Management, kann die Systemleistung steigern, die Auflösung verbessern und den Spielraum für Entwickler erweitern, ohne das Gesamt-Power-Budget zu überschreiten.

Der letzte Funktionsblock in der Signalkette (Bild 1) eines Ultraschallsystems rekonstruiert das Bild. Dieser Block wandelt die rohen Daten, die vom Front-End aufgenommen wurden, in ein Bild, das auf einem Monitor dargestellt werden kann. Es gibt viele in C, C++, MATLAB oder OpenCL geschriebene Algorithmen, die bestimmen, wie die erfassten Daten in ein betrachtbares Bild verarbeitet, konvertiert und interpretiert werden. Dieser Schritt enthält komplexe Matrixmultiplikationen mit der rechenintensiven FFT (Fast Fourier Transformation). Häufig bauen Softwareentwickler Modelle der benötigten Algorithmen und Hardwareentwickler übersetzen diese in HDL (Hardware Description Language) für die Implementierung in das FPGA. Diese Aufteilung der Aktivitäten unterbricht den Entwicklungsablauf, was die Entwicklungszeit verlängern kann, insbesondere wenn mehrere Designiterationen nötig werden.

Die Lösung dafür ist ein All-Programmable-Abstrahierungswerkzeug, das C-, C++-, MATLAB- oder OpenCL-Konstrukte automatisch in HDL umwandelt und das Design automatisch in das FPGA platziert und routet. Dies kann, verglichen mit einem konventionellen manuellen Entwicklungsablauf, die Entwicklungsdauer signifikant verkürzen, sodass sich die Entwickler mehr auf ihre Kernkompetenzen des Aufbaus und der Interpretation des Ultraschallbildes konzentrieren können.

Über die Autorin:

Yvonne Lin ist Medical Marketing Manager bei Xilinx.

- Beschleunigtes Ultraschall

- Arbeitsweise eines Ultraschallgeräts

- FPGAs sparen Energie