Sensornetze:

Strom einsparen im Funksensorknoten

Fortsetzung des Artikels von Teil 1

Sehr hohe Störsicherheit

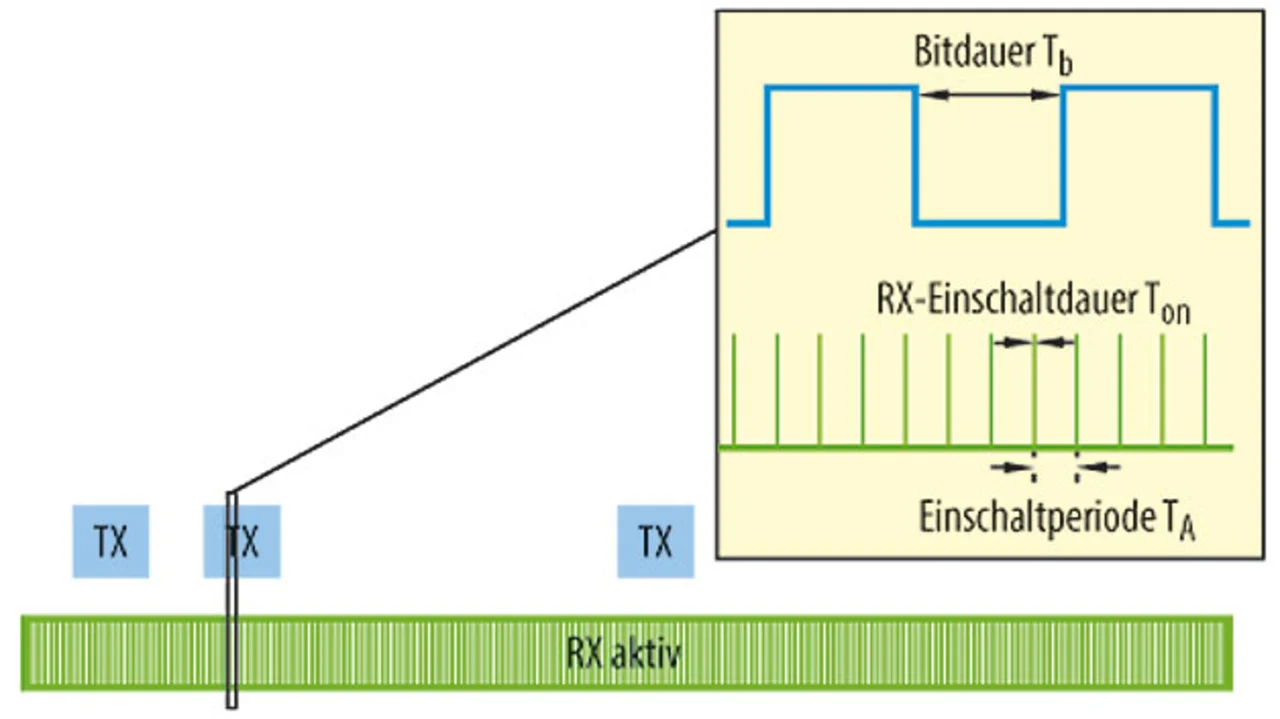

Eine sehr viel elegantere Lösung hat eine Entwicklergruppe am Fraunhofer-Institut für Integrierte Schaltungen (IIS, www.iis.fraunhofer.de, www.rfic.de) in Erlangen gefunden. Die entscheidende Änderung gegenüber den früheren Systemen: Das Ein- und Ausschalten des Empfängers erfolgt hier mit einer sehr viel höheren Frequenz – deutlich über der Bitrate des Senders. Beispielsweise sendet dieser mit 1 kbit/s, dann macht der Empfänger eine Überabtastung mit 4 kHz; er ist jeweils für 250 ns ein- und für 249,75 µs ausgeschaltet (Bild 2).

Jobangebote+ passend zum Thema

Damit ist seine mittlerer Stromaufnahme ebenfalls auf ein Tausendstel gesenkt, aber die Reaktionszeit ist minimal. In der Praxis lassen sich 40 ms oder weniger erreichen. Eine Lithium-Knopfzelle mit z. B. 200 mAh hält auf diese Weise mehrere Jahre durch. Die Wirkung ist aber praktisch dieselbe, als wäre der Empfänger durchgehend eingeschaltet. In den simpelsten Systemen dieser Art wird das Aufwecken ganz einfach durch die Anwesenheit des Trägers ausgelöst. Dies ist aber unzuverlässig, wenn die Umgebung mit starker Störstrahlung verseucht ist – wie im Industriebereich nicht selten. Ungewolltes Aufwecken lässt sich vermeiden, indem man das Sendesignal mit einem bestimmten Code moduliert, auf den der Empfänger reagiert. Am Fraunhofer IIS befand man eine Sequenz von 31 bit als sinnvollen Kompromiss zwischen Sicherheit und Fehlertoleranz. Dabei dürfen bis zu fünf Bits falsch sein, das Signal wird dann immer noch als „echt“ interpretiert. Die Übertragungsrate dafür ist 1024 bit/s, somit dauert dieser Vorgang 30,3 ms.

Nicht immer sollen alle Empfänger aufgeweckt werden. In vielen Fällen ist es sinnvoller, nur Untergruppen oder überhaupt nur einzelne anzusprechen. Sonst gibt es bei den Antworten ein Durcheinander. Dazu sendet man nach der Aktivierungssequenz noch einen Identifikationscode, z.B. 16 bit. Damit an dieser Stelle unter allen Umständen Fehler vermieden werden, spreizt man diese noch einmal um einen Faktor 31, insgesamt also 496 Bits.

Das erfordert dann natürlich mehr Zeit. Um diese abzukürzen, steigert man hier kurzzeitig die Übertragungsrate, beispielsweise um den Faktor 8 auf 8192 bit/s. Der Empfänger-Takt muss dafür entsprechend erhöht werden, also auf 32 kHz. Die 250 ns Öffnungszeit bleiben. Die mittlere Stromaufnahme des Empfangsteils steigt dann logischerweise ebenfalls auf das Achtfache, von 11 µA also auf 88 µA – aber nur für kurze Zeit. In der neuesten Version wurde sogar eine Steigerung um den Faktor 32 erreicht.

Eine logische Null wird also durch eine Sequenz von 31 bit repräsentiert, eine logische Eins durch eine andere solche Sequenz, die von der ersteren sehr weit weg liegen muss. Hierzu haben die Fraunhofer-Entwickler ausgiebige Untersuchungen durchgeführt. Mit den gefundenen Sequenzen sind Nullen und Einsen auch bei starken Störungen sehr sicher unterscheidbar. Das vermeidet Nachfragen, die Strom kosten würden.

- Strom einsparen im Funksensorknoten

- Sehr hohe Störsicherheit

- Vielseitiger Chip