IEDM 2019

TSMC enthüllt 5-nm-CMOS-Technologie-Plattform

Fortsetzung des Artikels von Teil 1

HMC-FinFETs und Backend-Verdrahtung

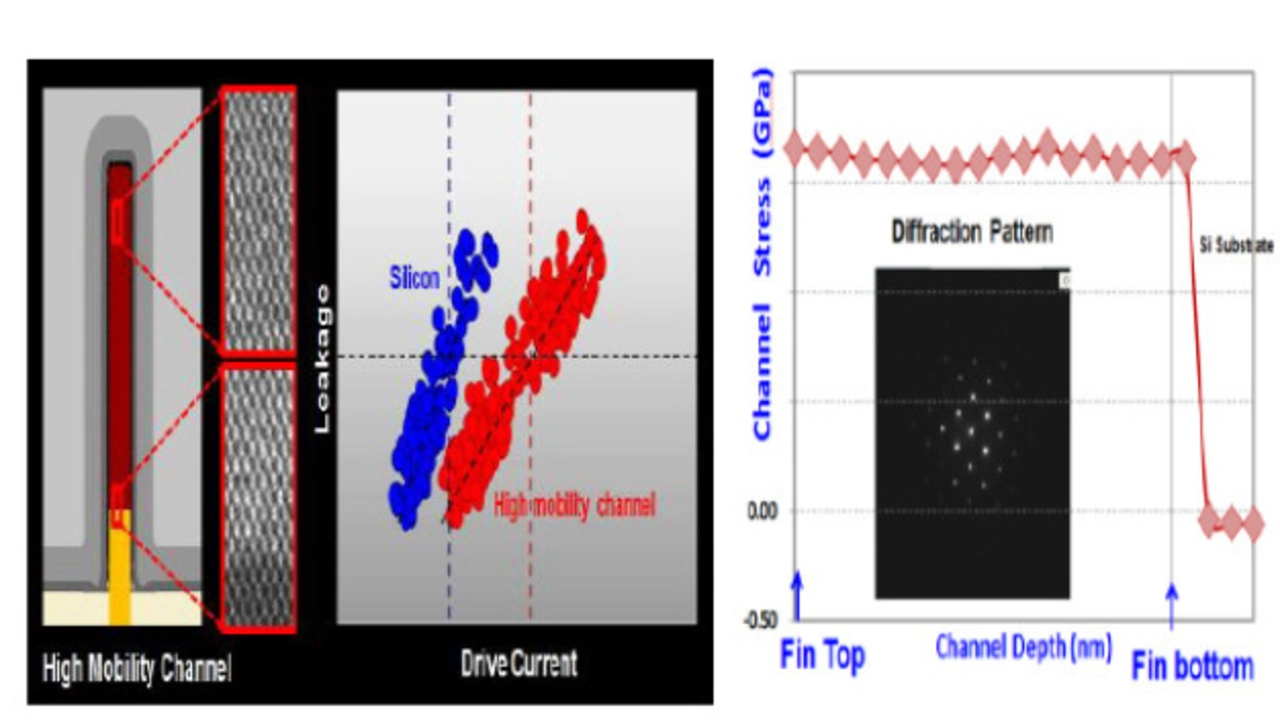

Vier Generationen von Si-FinFETs wurden vom 16-nm Knoten bis zum 7-nm Knoten eingesetzt. Die Leistungsfähigkeit von FinFETs stagnierte, und ein Transistor mit hoher Ladungsträgermobilität im Kanal (HMC) wird genutzt, um die dringend benötigte Verbesserung der Treiberströme zu erreichen. HMC-FinFETs zeigen ausgezeichnete Id-Vg-Eigenschaften. Die Standby-Leistung des Ringoszillators nach dem Figure-of-Merit (FOM) Prinzip korreliert ebenfalls gut mit Transistorleckströmen. Der HMC-FinFET liefert nachweislich einen ca. 18 % höheren Treiberstrom als der Si FinFET. Eine TEM-Analyse zeigt eine vollständig gespannte (strained) HMC-Gitterkonstante, die sich mit der Si-Gitterkonstante verbindet. Das Beugungsmuster bestätigte die HMC-Dehnung. Die Leistungsfähigkeit der Technologie ist auch entscheidend vom Backend-Metall RC und dem Via-Widerstand abhängig. Die engsten Pitch-Mx RC und Vx Rc blieben relativ ähnlich wie beim vorherigen 7-nm-Knoten, wobei EUV-Strukturierung, innovative skalierte Barrieren/Liner, ESL/ELK-Dielektrika und Cu-Reflow genutzt wurden.

Jobangebote+ passend zum Thema

Neuer Rekord: Kleinste SRAM-Zelle

Da der SRAM-Bedarf in der HPC-KI zunimmt und der L3/Systemspeicher im mobilen SoC, werden die SRAM-Dichte und Performance/Leckströme immer wichtiger. Daher gibt es zwei grundlegende SRAM-Zellen optimiert für Hochstrom (HC) mit einer Fläche von 0,025µm2 und hohe Dichte mit 0,021µm2 (HD). Derzeit dürfte das 0,021µm2 HD-SRAM in diesem echten 5-nm-Technologie die höchste Dichte aufweisen, die bis dato berichtet wurde. Zwei Instanzen von 256-Mbit HD und HC SRAM wurden zusammen mit einem großen 5-nm-Logik-Testchip qualifiziert. Diese 5-nm-Implementierung hat durchweg eine sehr hohe Ausbeute für das 256-Mbit-SRAM und den Logik-Testchip erzielt: >90 % Spitzenausbeute und ca. 80% Durchschnittsausbeute (ohne Reparatur) bei 256 Mbit HC und HD SRAM.

Sowohl das 256-Mbit HD/HC SRAM als auch der Logik-Testchip haben die 1000 Stunden HTOL-Qualifikation bestanden. HD/HC SRAM Vmin weist bei 168 Stunden eine vernachlässigbare Spannungsdrift auf und passierte 1000 Stunden HTOL mit ca. 51 mV Marge. Stress-Daten zeigen dass der 5-nm-FoM-Ringoszillator mit HMC-Transistoren nicht so schnell altert, wie die FinFETs bei 7 nm.

Zusätzliche HPC-Funktionen wie Super High Density (SHD) MiMs, die eine vierfach höhere Kapazitätsdichte als typische HD-MiMs aufweisen, sorgen durch eine Minimierung der transienten Ableitspannung für eine Steigerung der Fmax um 4,2 % und erreichen eine Vmin-Reduzierung um ca. 20 mV in einem CPU-Testchip.

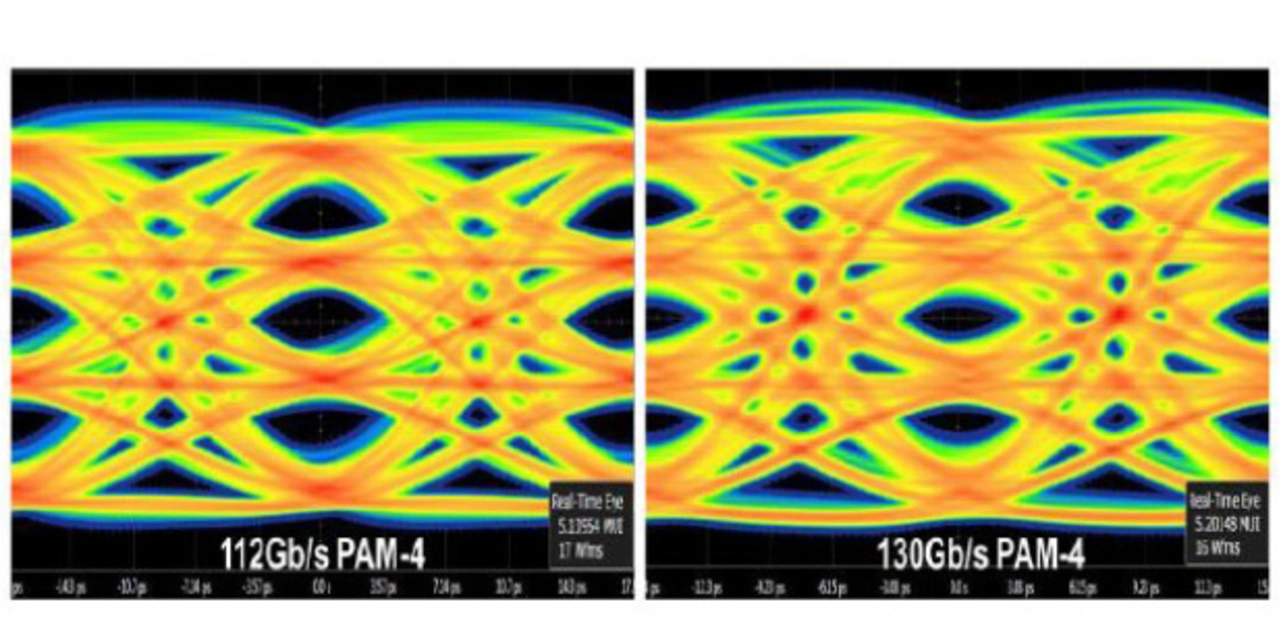

Eine weitere kritische HPC-IP wie Hochgeschwindigkeits-SERDES wurde erfolgreich entwickelt, indem die FinFET-Treiberkraft und das Kapazitäts-/Widerstands-Verhalten durch den Einsatz von speziellen Hochgeschwindigkeitsschaltungen optimiert wurden. So konnte ein PAM 4-Sender mit einer Maximalgeschwindigkeit von 130 Gbit/s bei einer Übertragungsenergie von 0,96 pJ/bit und nominal 112 Gbit/s bei 0,78 pJ/bit demonstriert werden.

- TSMC enthüllt 5-nm-CMOS-Technologie-Plattform

- HMC-FinFETs und Backend-Verdrahtung