Neue High-End-CPU

Arm Cortex-A77 – Schneller auch ohne Moore‘s Law

Fortsetzung des Artikels von Teil 1

Weiterentwicklung der NPU

Anfang 2018 kündigte Arm sein »Projekt Trillium« an, eine Prozessor-IP für maschinelles Lernen auf der Basis neuronaler Netzwerke oder auch NPU genannt (Neuronal Networks Processing Unit). Die NPU soll CPUs und GPUs bei neuronalen Netzwerkoperationen ergänzen, auch hier gibt es ein Update.

Im Gegensatz zu rechenzentrumsbasierten Ansätzen will Arm maschinelles Lernen »on the edge« möglich machen, das heißt direkt im Endgerät. Dies hat auf den ersten Blick zahlreiche Vorteile, wie etwa geringere Latenzzeiten, da der Datentransfer vom und zum Rechenzentrum entfällt, und Kostenreduktion zum Beispiel durch den Entfall des (drahtlosen) Datentransfers. Ein weiterer Aspekt ist die Datensicherheit, da die Daten das Endgerät nicht mehr verlassen und damit nicht mehr im Rechenzentrum selbst oder auf dem Weg dahin von Hackern abgefangen werden können.

Das Problem beim Edge-Computing besteht jedoch darin, dass die für neuronale Netzwerke wichtigen rechenintensiven Operationen wie Matrizen-Multiplikationen auf herkömmlichen CPU- und GPU-Architekturen nicht oder nur mit enormem Hardware-Einsatz realisierbar sind, da weder CPU- noch GPU-Mikroarchitekturen für diese Art von Workloads (zum Beispiel eben zweidimensionale MAC-Operationen im Fall von Matrizen) designt wurden. Als Antwort auf diese Herausforderungen wurden spezielle NN-Prozessoren entwickelt.

Der maschinelle Lernprozessor von Arm basiert auf einer neuen Architektur speziell für neuronale Netze. Sie ist vom Mobiltelefon bis hin zum Einsatz in Rechenzentren skalierbar und soll drei wesentliche Aspekte abdecken, die bei dieser Art von Workloads relevant sind: Effizienz bei der Berechnung von Faltungen, effiziente Datenverschiebung und hinreichend einfache Programmierbarkeit. Dazu kommen 16 »Compute Engine« genannte Einheiten für die reine Datenberechnung, ein Speichersubsystem und ein programmierbarer Block für die Ablaufsteuerung, der aus einem Mikrocontroller und einer DMA-Engine besteht. Die Faltungsberechnungen konzentrieren sich normalerweise auf 8-bit-Datentypen, die sich als Standard in maschinellen Lernanwendungen etabliert haben, wobei interne Operationen mit unterschiedlichen Präzisionen ausgeführt werden. Der Datendurchsatz beträgt laut Arm bei Implementierung in TSMCs 7-nm-Prozess und Verwendung von int 8-Daten 4 TOP/s, bei int 16 immerhin noch 2 TOP/s. Typische Muster mit 16 bit Aktivierung, 8 bit Gewichtung und 16x16 Operationen reduzieren den Durchsatz auf 1 TOP/s.

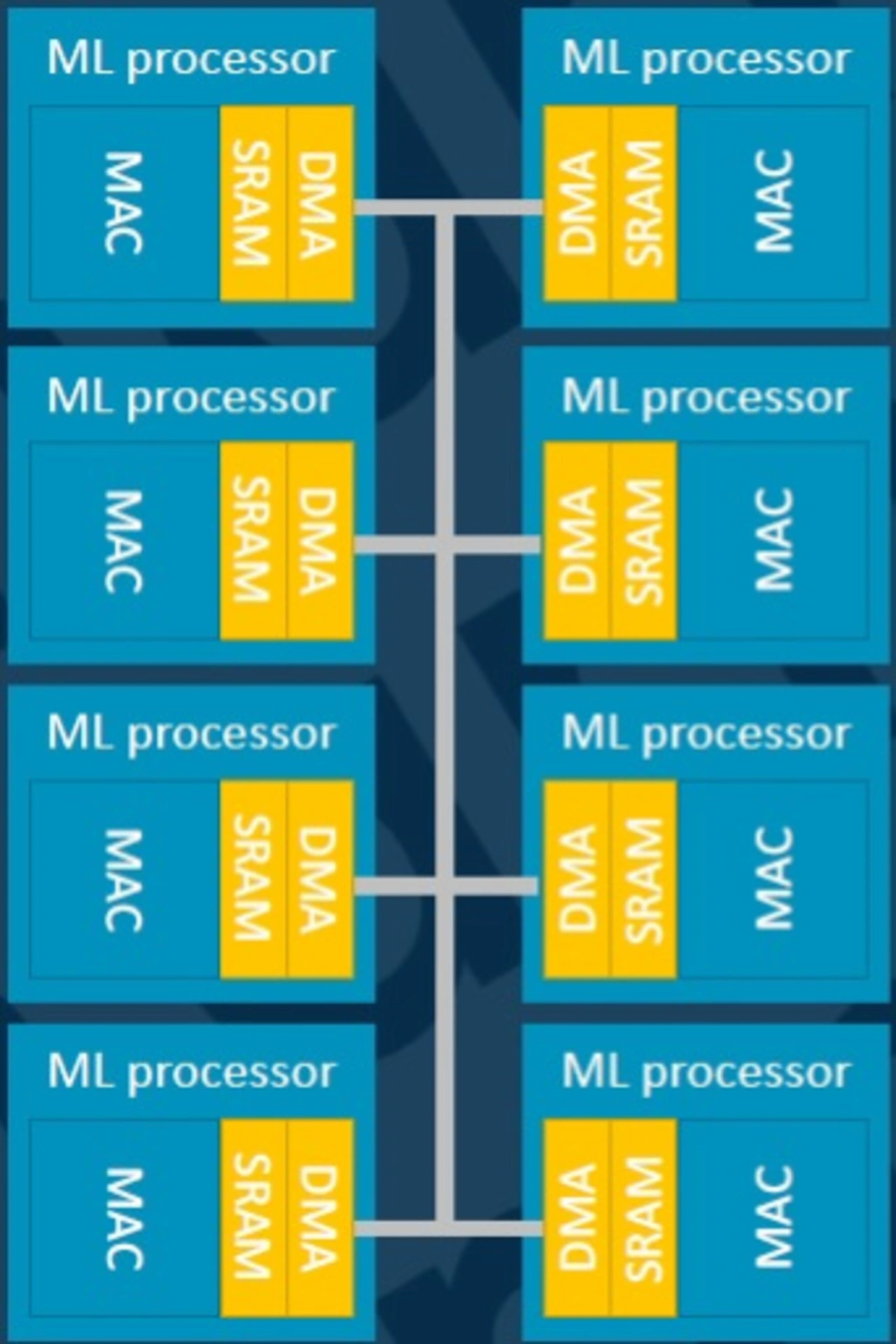

Bei der Vorstellung der NPU im Jahr 2018 ging Arm von einer Leistungsaufnahme von 3 TOP/W aus, mittlerweile wurde die IP so weiterentwickelt, das man seinen Kunden 5 TOP/W zusagt. Bemerkenswert ist die Auslastung der MAC-Engines von bis zu 93 % (Inception v3 - ein bekanntes Bildklassifizierungs-CNN - mit Winograd-Technologien), desweiteren können bis zu 8 NPUs in einer Multicore-Konfiguration bis zu 8 NPUs in einem eng angebundenen Cluster verbunden werden, um auf einen Spitzendurchsatz von 32 TOP/s zu kommen (Bild 4). Die NPUs können dabei nichtkohärent verschaltet werden, um z. B. mehrere Inferenz-Typen parallel laufen zu lassen, wobei dann auch mehrere Adressräume unterstützt werden. Man kann aber auch ein neuronales Netzwerk auf allen Cores im kohärenten Betrieb ausführen, um den Durchsatz z. B. für die Analyse von hochauflösenden 4K-Bildern zu maximieren.

Das SRAM ist ein gemeinsamer Block mit einer Größe von 1 MB, der als lokaler Puffer für die Berechnungen der Compute-Engines dient. Deren Funktionsblöcke arbeiten auf den verschiedenen Ebenen des neuronalen Netzwerkmodells, zum Beispiel Faltungsberechnungen, Gewichte-Dekoder usw. Die Faltungsberechnungen werden in einer 128 bit breiten MAC-Einheit ausgeführt.

Jede Compute-Engine hat ihren eigenen lokalen Speicher, der von den Modulen zur Verarbeitung von DNN-Modellen verwendet wird (DNN-Deep Neuronal Network). Der Ablauf ist typisch für DNN-Implementierungen, beginnend mit der Gewichtung der eingehenden Daten, der Verarbeitung über die MAC-Faltungsengine und der Verarbeitung der Ergebnisse durch die programmierbare Layer-Engine (PLE).

Entwicklung für zukünftige NN

Die sogenannte Programmable-Layer-Engine (PLE) soll die Architektur bezüglich fortlaufender Entwicklung des maschinellen Lernens flexibel halten. Ob die derzeitigen Modelle auch noch in Jahren verwendet werden, ist nämlich alles andere als sicher, wenn man erstmal hinreichende Erfahrungen mit den heutigen Modellen gemacht hat. Die PLE ermöglicht es dem ML-Prozessor, über Vektor- und NN-spezifische Befehle neue Operatoren einzubinden und verarbeitet die Ergebnisse der MAC-Engines, bevor die Daten wieder in das SRAM geschrieben werden.

Eine weitere Herausforderung beim Edge-Computing sind der limitierte Datendurchsatz vom und zum Chip und das verfügbare Energiebudget, insbesondere kann externes DRAM eine ähnlich hohe Leistungsaufnahme generieren wie der ML-Prozessor selbst. Die Architektur von Arm nutzt daher gängige Verfahren, um Feature-Maps verlustfrei zu komprimieren, indem das häufige Auftreten von sich wiederholenden Nullen in einem gegebenen 8×8-Block verborgen wird. SRAM, in dem Zwischenergebnisse und Daten gespeichert werden, beansprucht ebenfalls ein hohes Energiebudget, so dass jede Möglichkeit zur Reduzierung der benötigten SRAM-Kapazität genutzt wird. Für 16 Compute-Engines sieht Arm einen Bedarf von 1 MB SRAM.

Um den Speicherbedarf weiter zu reduzieren, werden auch die Gewichte komprimiert und reduziert. Analog zu einer biologischen Synapse im Gehirn repräsentieren die Gewichte das Wissen in einem neuronalen Netz. Die Reduktion von Neuronen, die keinen signifikanten Einfluss auf das Endergebnis haben würden, erlaubt es der Hardware, bestimmte Berechnungen zu überspringen und reduziert so die Anzahl der DRAM-Aufrufe. Arm behauptet, dass Kompressionsverhältnisse von bis zu 3 möglich sind.

Um die Anzahl der Berechnungen zu reduzieren, können Winograd-Technologien (Terry Allen Winograd, ein US-Informatiker, bekannt für Forschungen zur Künstlichen Intelligenz) eingesetzt werden, welche bei Netzwerken wie Inception v1-v4, Resnet-v1/v2, VGG16 und YOLOv2 Fläche und Energiebedarf um bis zu 50 % reduzieren können.

Jobangebote+ passend zum Thema

Es soll aber auch Implementierungen in 16 nm geben. Neben der Maximal-Konfiguration mit 16 Compute-Engines und 1 MB SRAM soll es später auch kleinere Varianten geben, sogar eine Minimalkonfiguration mit nur einer Compute-Engine steht zur Disposition. An Siliziumfläche soll die NPU mit 16 Engines etwas mehr als ein Cortex-A55 belegen. Im Vergleich zu dem brandneuen Cortex-A77-Anwendungsprozessor erzielt der ML-Prozessor eine um Faktor 64 höhere Rechenleistung gemessen in MAC-Operationen pro Core und Taktzyklus.

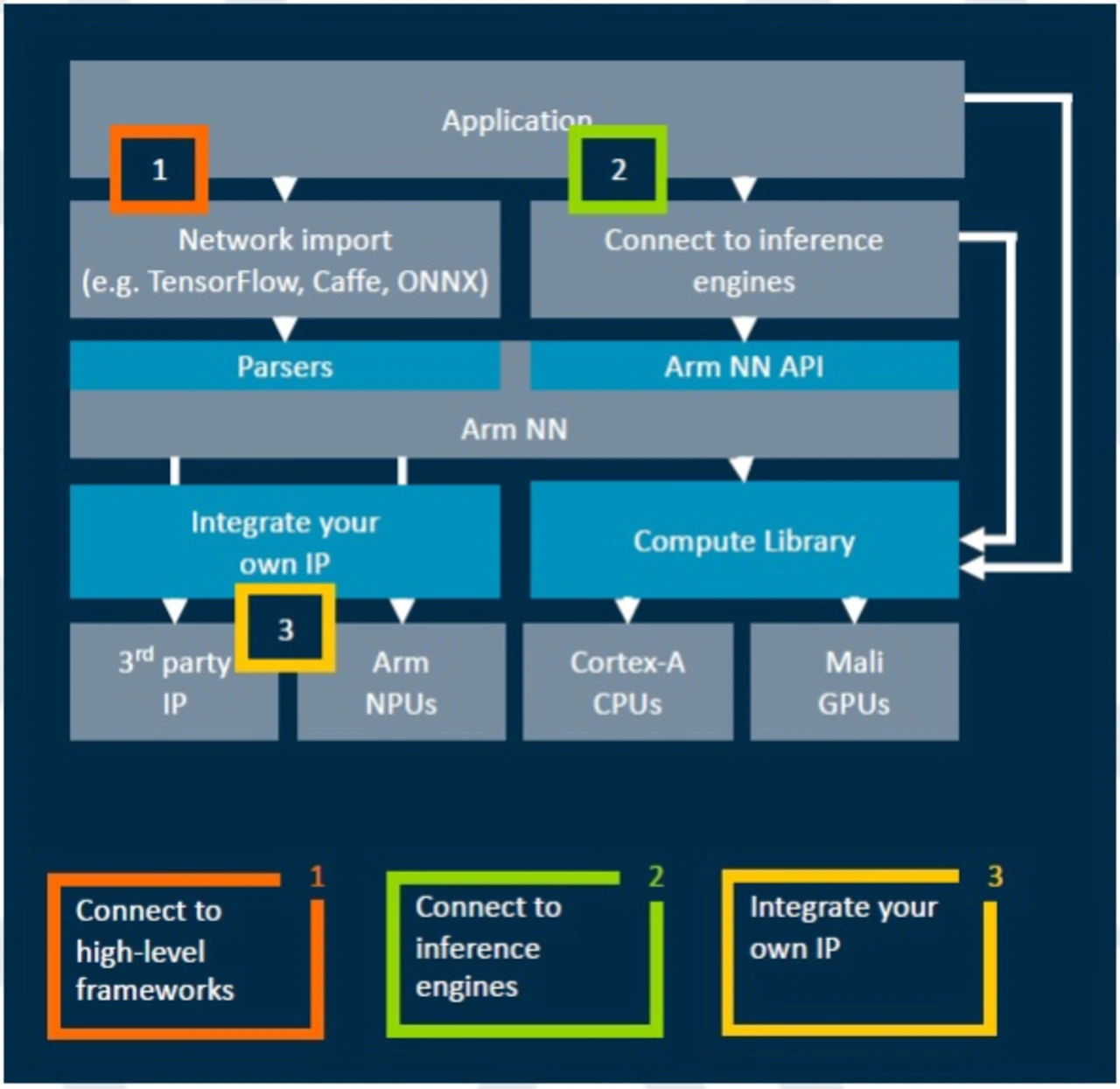

Arm will Workloads für NPU, CPUs und GPUs mit einer gemeinsamen Software-Bibliothek bedienen. Der Kern davon ist »Arm NN«, eine Art Brücke zwischen den gängigen neuronalen Netzwerkframeworks von Drittanbietern wie TensorFlow, Caffe und Android NNAPI sowie den verschiedenen Arm-CPUs und -GPUs (Bild 5). Code kann generisch geschrieben und auf jeder verfügbaren Verarbeitungseinheit ausgeführt werden. Beispielsweise kann ein budgetorientiertes Gerät mit herkömmlichem CPU- und GPU-Setup denselben NN-Code ausführen wie ein High-End-Gerät mit einem diskreten ML-Prozessor – nur langsamer. Arm bietet auch Unterstützung für IP von Drittanbietern, die bei Bedarf in den Stack integriert werden können. Arms NN beinhaltet bis heute ca. 445.000 Lines of Code, der Entwicklungsaufwand beläuft sich bislang auf 120 Personenjahre. Arm schätzt, dass es bislang schon in über 250 Millionen Android-Geräten eingesetzt wird. Durch optimierte Implementierungen von Arms Partnern soll Arms NN im Vergleich zu anderen NN-Frameworks deutlich schneller sein: Betrachtet man z. B. einen Cortex-A-Prozessor ist Arm NN 1,5x schneller als resNet-50 und sogar 3,2x schneller als Inception v3.

In gewisser Weise verfolgt Arm mit ArmNN den gleichen Ansatz, den Nvidia mit seiner Cuda-Plattform verfolgt, die auf eine Reihe von GPUs abzielt. Diese GPUs sind ähnlich, haben aber jeweils kleine Unterschiede, die durch die Cuda-Unterstützung verdeckt sind. Ein eigenes Framework macht es für Entwickler schwer, auf verschiedene Plattformen zu wechseln. Cuda beherrscht mehr als nur künstliche Intelligenz (AI) und ML-Anwendungen. Entwickler, die auf ML-Tools wie TensorFlow abzielen, können normalerweise von Plattform zu Plattform wechseln, einschließlich des ML-Prozessors von Arm.

- Arm Cortex-A77 – Schneller auch ohne Moore‘s Law

- Weiterentwicklung der NPU

- Fazit