Xilinx

Bildverarbeitung in programmierbarer Logik mit C/C++

Die Bildverarbeitung in medizinischen oder industriellen Applikationen, mobil oder nicht, ist so komplex, dass PCs mit GPU-Beschleunigung überfordert sind. Mit Zynq-7000 All Programmable SoCs lassen sich eine Beschleunigung um mehr als eine Größenordnung erreichen.

Xilinx

Unser Beispielsystem erfasst Einzelbilder mit bis zu 3000 x 2000 Pixeln, also keinen Live-Video-Stream, es verarbeitet sie im Batch-Modus in einer schnellen Pipeline durch Umwandlung von RGB in eine Grauskala, fügt (statistisches) Salt-and-Pepper-Rauschen hinzu und filtert das verrauschte Bild dreifach: Dilate, Median und Erode.

Dilatations-, Median- und Erosionsfilter gehören zur Klasse der Rangordnungsfilter, wie sie gegen Impulsstörungen zur Bildverbesserung eingesetzt werden. Obwohl die üblichen Algorithmen nicht besonders komplex sind, bedingen sie bei großen Bildern beträchtliche Verarbeitungszeiten wegen der sequentiellen Natur der Prozessoren, weil zu jedem Zeitpunkt nur ein Pixel verarbeitet wird.

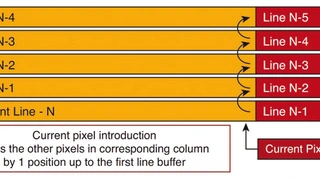

Die Rangordnungsfilter sind nichtlineare Filter, die das Ausgangsbild Pixel für Pixel berechnen. Das geschieht mithilfe der Nachbarpixel im Eingangsbild innerhalb einer vorge-

gebenen Art und Größe der Nachbarschaft, die durch das Strukturierungselement vorgegeben wird, und anschießender Sortierung und Auswahl des Pixels mit dem Rang p. Das Erosionsfilter wählt den minimalen Wert p = 1, das Dilationsfilter den maximalen Wert p = N (mit N als der Zahl der Pixel des strukturierenden Elements). Die Medianfilterung bestimmt den Mittelwert p = N/2. Typischerweise hat das strukturierende Element eine Rechteck-, Rauten- oder Kreuzform.

Unsere Batch-Verarbeitung behandelt die von der SD-Card gelesenen Bilder mit unterschiedlichen Parametern für den Rauschpegel und die als strukturierendes Element verwendete Form. Diese Berechnungen übernehmen die Dual-Cortex-A9-Kerne des mit 667 MHz laufenden Zynq-7000-SoCs.

Software-Implementierung

Zunächst schreiben wir die vollständige Applikation in C++, um die Performance des Cortex-A9 abzuschätzen. Sie enthält Funktionen zum Lesen und Schreiben von BMP-Bilddateien auf der SD-Card, zur Berechnung der Luminanz, um Rauschen hinzuzufügen und verschiedene Filterungen durchzuführen. Die SDDebug-Konfiguration im SDSoC-Entwicklungssystem ermöglicht die schnelle Linux-Implementierung auf der Xilinx ZC702 Evaluierungsplattform.

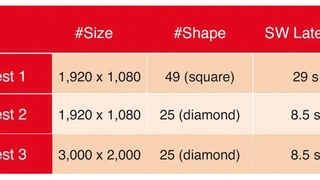

Um ein wirklich lauffähiges Programm zu erzeugen, wählen wir die Option -O3 zur Aktivierung aller Compiler-Optimierungen. Als strukturierendes Element können wir jede, in eine Bounding-Box mit 7 x 7-Pixeln passende Form verwenden. Die Latenz der Pipeline (Bild 1) wird von der Bildgröße (#Size) und Zahl der aktiven Pixel im strukturierenden Element (#Shape) beeinflusst. Minimieren dieser Latenzen verbessert die Performance. FPGAs eignen sich hervorragend zur Signalverarbeitung mit zahlreichen Additionen und Multiplikationen. Unser Beispiel zeigt, dass sich die programmierbare Logik nicht nur zur Berechnung, sondern auch für reguläre Datenverarbeitungsaufgaben gut eignet.

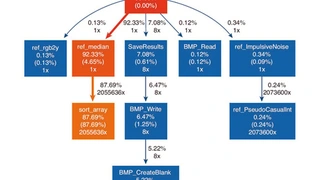

Die Übersicht in Bild 2 verdeutlicht, dass die Berechnung der Luminanz aus RGB-Daten (0,13%) und das Hinzufügen des Rauschens (0,34%) in Software recht schnell verlaufen. Den größten Zeitanteil hat das Medianfilter (92,33%). Andere Funktionen mit etwas mehr Zeitaufwand sind das Lesen und Speichern der Dateien.

Jobangebote+ passend zum Thema

- Bildverarbeitung in programmierbarer Logik mit C/C++

- Verlagern einer Funktion in die Hardware

- SDSoC-Compiler