Timing-Bausteine

Präzise Dreierkombination

So gut wie jede Operation in einem elektronischen System erfolgt synchron zu einem Taktsignal. Mikroprozessoren zum Beispiel verarbeiten ihre Befehle Schritt für Schritt nach dem Systemtakt. Ob wir telefonieren, eine E-Mail abschicken, den Sportkanal im Fernsehen anschauen oder Geld am Automaten abheben stets sind wir darauf angewiesen, dass präzise Takt-Bauelemente sämtliche Abläufe steuern und synchronisieren. Ein neues Timing-IC synthetisiert den Takt, eliminiert Jitter und verteilt das Taktsignal gleichzeitig.

Dass komplexe elektronische Systeme hohe Anforderungen an die Taktung stellen, dürfte nicht überraschen. Ein typisches System, das auf einer Leiterplatte Datenwandler, FPGAs und HF-Bauelemente enthält, benötigt gleich mehrere verschiedene Taktfrequenzen, die darüber hinaus in den meisten Fällen auf irgendeine Weise miteinander zu synchronisieren sind. Die Eigenschaften, die der Systemtakt in Bezug auf den Jitter, das Phasenrauschen und Störfrequenzen aufweisen muss, diktieren die anspruchsvollsten Bauelemente. Dies sind im allgemeinen HF-Bausteine wie etwa Mischer und Demodulatoren sowie A/D-Wandler (ADCs). Die Entwicklung einer komplexen Taktungslösung stellt somit eine immense Herausforderung für die Systemdesigner dar.

ADCs mit hoher Abtastrate benötigen Taktsignale mit einem RMS-Jitter von unter 1 ps, um die optimalen Rauscheigenschaften einzuhalten. Das Synchronisieren von Taktsig-nalen ist besonders bei zunehmenden Signalfrequenzen äußerst anspruchsvoll. Die Verteilung der Synchronisationssignale wird außerdem dadurch erschwert, dass Bauelemente nicht selten auf verschiedenen Seiten einer Leiterplatte oder sogar auf verschiedenen Boards platziert sind. Hinzu kommt, dass komplexe Leiterplatten unter Umständen mehrere verschiedene Taktfrequenzen und Logik-Signalpegel erfordern (z.B. LVPECL, LVCMOS, LVDS usw.).

Anhand des neuen »ADC12D800RF«, eines 12-Bit-A/D-Wandlers von Texas Instruments mit einer Abtastrate von 800 MSample/s beziehungsweise 1,6 GSample/s und einer analogen Eingangsbandbreite von 2,7 GHz, möchten wir nun untersuchen, welche Anforderungen an den Taktjitter gestellt werden, um die Angaben im Datenblatt zu erreichen. Der Baustein gehört zu einer Familie, die für das Direct-RF-Sampling, also die direkte Abtastung des Hochfrequenzsignals ohne zwischengeschaltete ZF-Stufe vorgesehen ist.

Der ADC12D800RF kommt auf einen Signal/Rausch-Abstand (SNR) von 56,4 dB, gemessen im gesamten Nyquist-Band bei der Quantisierung eines Signals mit einer Frequenz von 1498 MHz. Da die gewünschte Signalbandbreite häufig deutlich kleiner ist als die Nyquist-Bandbreite, lässt sich die digitale Filterung einsetzen, um das Eigenrauschen dieses ADCs von -152,2 dBm/Hz auszunutzen. Der IMD3-Wert (Intermodulationsverzerrung der dritten Harmonischen) beträgt -87 dBFS bei einer Eingangsfrequenz fin von 2670 MHz ± 2,5 MHz und -16 dBFS.

Es besteht ein direkter Zusammenhang zwischen der Genauigkeit des Abtasttakts und der Dynamik eines A/D-Wandlers. Jegliche Timing-Unsicherheit (Jitter) wirkt sich auf die SNR aus. Etwaige Oberschwingungen des Abtasttakts vermischen sich außerdem mit dem analogen Eingangssignal und beeinträchtigen den IMD-Wert (Inter Modulation Distortion) und das NPR (Noise Power Ratio; Rauschleistungsverhältnis). Deshalb ist eine jitterarme Taktquelle mit einwandfreiem Rauschverhalten nötig.

Optimiert man die Eingangsspannung so, dass sie genau dem vollen Eingangsbereich des ADC entspricht, so wird der einzuhaltende Jitter nur noch vom Eigenrauschen des ADCs und der abzutastenden Eingangsfrequenz bestimmt. Welcher Jitter zulässig ist, um eine bestimmte Rausch-Spezifikation zu erfüllen, lässt sich mit der folgenden Formel ausrechnen, wenn man davon ausgeht, dass das gesamte Nyquist-Band genutzt wird:

Diese bekannte Gleichung wurde für sinusförmige Signale am ADC-Eingang aufgestellt. Dennoch liefert sie eine angemessene Näherung des SNR für ein breitbandiges Signal, sofern die Abtastrate deutlich größer als die Signalbandbreite ist. Der jitterbedingte Signal-Rauschabstand ist unabhängig von der Auflösung und Abtastrate des ADCs und nimmt mit steigender Signalfrequenz ab. Bei einer Eingangsfrequenz von 1498 MHz darf der Gesamtjitter nicht größer als 160 fs sein, um ein SNR von 56,4 dB zu erreichen.

Clock-Multiplier und Jitter-Cleaner

Timing-Bausteine werden verwendet, um aus einem vorgegebenen Referenztakt eine oder mehrere Taktfrequenzen zu generieren. Gelegentlich ist der Referenztakt von großer spektraler Reinheit. Dann beschränkt sich die Aufgabe des Taktaufbereitungsbausteins (Clock Conditioner) darauf, diese Frequenz oder ein bestimmtes Vielfaches davon im gesamten System zu verteilen. Dies bezeichnet man als Clock-Multiplier-Applikation (Taktvervielfacher).

Ist der Referenztakt dagegen nur von unzureichender spektraler Reinheit, muss der Taktaufbereitungschip diesen zunächst »säubern«. Hier spricht man von einer Jitter-Cleaner-Applikation. Denkbar ist ferner, dass der Clock-Conditioner beide Aufgaben übernimmt. Was einen Präzisions-Clock-Conditioner auszeichnet, ist sein Rauschverhalten. Da man Taktsignale in der Regel verwendet, um verschiedene Ereignisse in einem System miteinander zu synchronisieren, ist die Fähigkeit, etwaige Skews zu kontrollieren und zu minimieren, ein überaus nützliches Feature. Die »LMK04800«-Familie enthält Clock-Conditioner, deren Jitter-Cleaning- sowie Takterzeugungs- und -verteilungsfunktionen durch Features ergänzt werden, mit denen sich viele komplexe Probleme auf der Systemebene lösen lassen.

Eine neue Familie von Clock-Jitter-Cleanern von Texas Instruments zeichnet sich durch einen Jitter von 111 fs von 12 kHz bis 20 MHz und ein Breitband-Eigenrauschen von -162 dBc/Hz bei einer Ausgangsfrequenz von 184 MHz aus. Mit diesem Phasenrauschen eignet sich der Chip für Systeme, die in drahtlosen oder leitungsgebundenen Kommunikationssystemen, in Prüf- und Messanwendungen, in bildgebender Medizintechnik, in Software-Defined-Radio-Anwendungen (SDR) und in Digital-Broadcast-Applikationen zum Einsatz kommen.

Jobangebote+ passend zum Thema

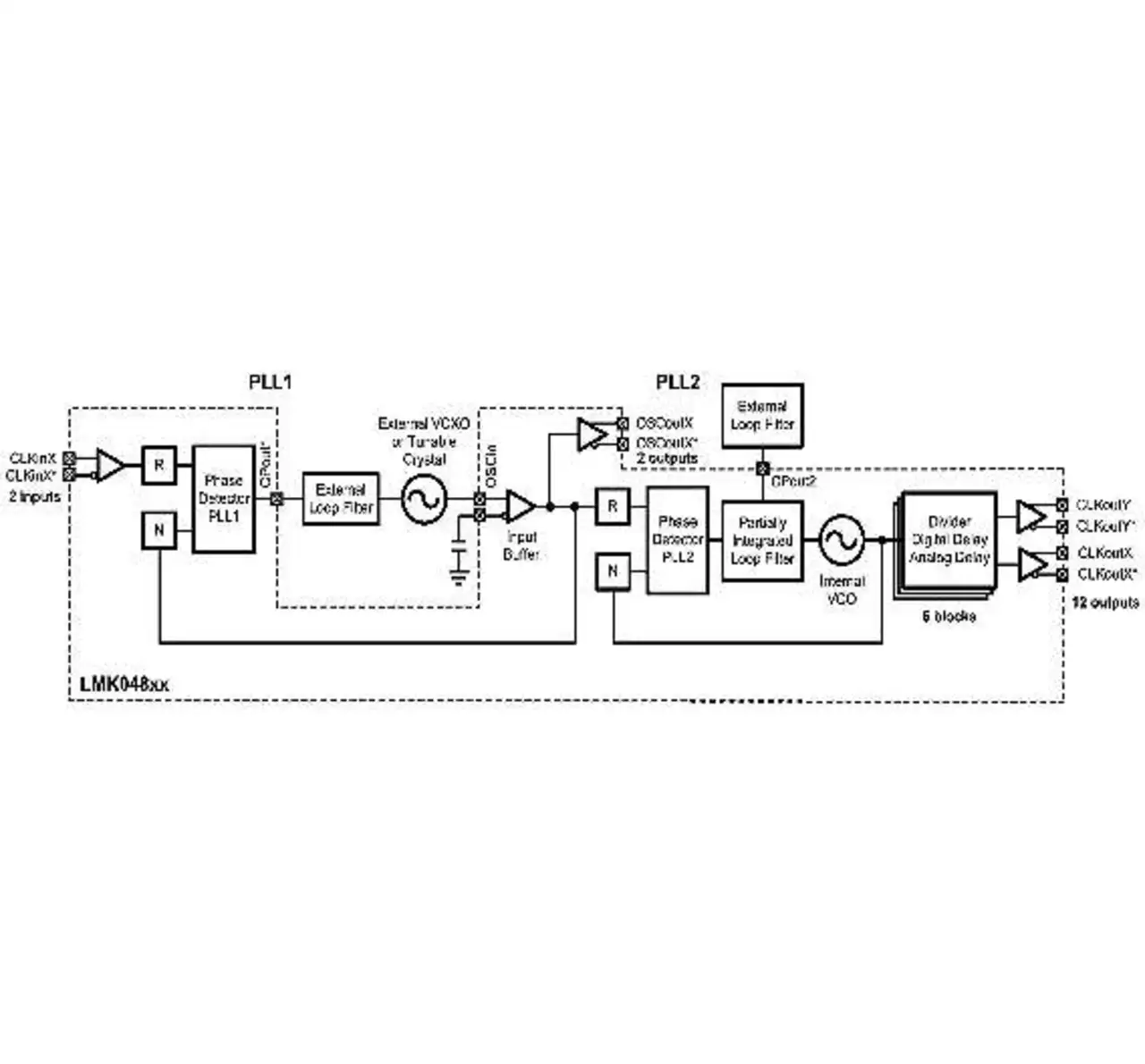

Die »Dual-Loop PLLatinum«-Architektur besteht aus zwei PLL-Stufen (Phase-Locked Loop), einer rauscharmen Quarzoszillator-Schaltung und einem VCO (Voltage Controlled Oscillator). Die erste PLL-Stufe (PLL1) stellt eine rauscharme Jitter-Cleaner-Funktion zur Verfügung, während die zweite PLL-Stufe (PLL2) für die Takterzeugung genutzt wird (Bild 2).

PLL1 lässt sich für den Betrieb mit einem externen VCXO-Modul oder dem integrierten Quarzoszillator (im Verbund mit einem externen abstimmbaren Quarz und einer Varaktordiode) konfigurieren. Mit einer sehr schmalen Schleifenbandbreite betrieben, nutzt PLL1 das gute Close-in-Phasenrauschen (Offsets unter 50 kHz) des VCXO-Moduls beziehungsweise des abstimmbaren Quarzes zum Bereinigen des Eingangstakts.

Der Ausgang von PLL1 dient wiederum als bereinigte Eingangsreferenz für PLL2, zu welcher der integrierte VCO verriegelt wird. Die Schleifenbandbreite von PLL2 lässt sich zum Bereinigen des Far-out-Phasenrauschens (Offsets über 50 kHz) optimieren, wobei der integrierte VCO die Leistungsfähigkeit des für PLL1 verwendeten VCXO-Moduls oder abstimmbaren Quarzes noch übertrifft. Die Familie besitzt zwei redundante Eingänge, 14 differenzielle Taktausgänge und nach dem Einschalten standardmäßig aktive Takte. Der Eingangsblock ist mit einer Holdover-Funktion ausgestattet und unterstützt die automatische oder manuelle Wahl des Referenztakts.

Clock-Design-Tool hilft

Texas Instruments hat ein Clock-Design-Tool entwickelt, das kostenfrei heruntergeladen und falls gewünscht auch offline genutzt werden kann. Dieses Werkzeug hilft bei der Wahl des richtigen Timing-Bausteins und unterstützt den Anwender beim Design eines Schleifenfilters, mit dem sich das optimale Phasenrauschen und Jitter-

Verhalten für die gewählte Lösung einstellt. Im Wizard-Modus kann die Software automatisch die VCO-Frequenz und die Teilerwerte für die PLL-Stufe und die Ausgangsteiler berechnen, um die vom Benutzer eingegebenen Frequenzen zu erhalten. Nach Wahl des »Wizard«-Modus werden vom Benutzer folgende Eingaben verlangt:

- Architekturtyp (eine PLL oder zwei PLLs in Serie),

- Referenz und/oder VCXO1 (optional) und

- Frequenz und Typ des Ausgangssignals.

Sind diese Eingaben gemacht, folgen zwei weitere Arbeitsgänge:

- Lösung wählen: Hier ist die Auswahl unter den Bauelementen zu treffen, die den Anforderungen des Designs entsprechen.

- Konfiguration wählen: Je nach den gestellten Anforderungen kann die gewünschte Konfiguration gewählt werden - unter Umständen auch mehrere.

Sobald der Simulationsbildschirm angezeigt wird, hat der Anwender folgende Möglichkeiten:

- Berechnung der Werte für die Schleifenfilter,

- Aktualisierung der Phasenrausch-Profile beispielsweise für Oszillatoren und VCXOs,

- Darstellung der RMS-Jitter-Messungen der verfügbaren Ausgänge,

- Kopieren der simulierten Phasenrausch-Kurven in die Zwischenablage zur Übernahme in Excel oder andere Programme und

- Abspeichern des Designs.

Das Tool wurde benutzt, um einen geeigneten Baustein zur Erzeugung eines LVDS-Takts mit 800 MHz für den ADC12D800RF auszuwählen. Die Wahl fiel auf den »LMK04806B«. Das Ergebnis der Phasenrausch-Simulation ist in Bild 3 dargestellt. Der von 1 kHz bis 10 MHz integrierte Gesamt-RMS-Jitter beträgt 109,1 fs.

Wie zuvor berechnet, liegt dieser Wert deutlich innerhalb des Bereichs, der zum Erreichen eines SNR von 56,4 dB bei 1498 MHz erforderlich ist.

Über den Autor:

Paul McCormack ist Business Development Manager für High Performance Analog in Europe bei Texas Instruments.