Multi-Gigahertz-Taktbäume

Neun Tipps zum Minimieren von Laufzeitabweichungen

Fortsetzung des Artikels von Teil 2

Laufzeitangepasste Kabel

Nach der Erfahrung des Autors ergeben sich beim Vergleich von gleich langen, aus identischem Material bestehenden Koaxialkabeln desselben Anbieters Laufzeitabweichungen zwischen 5 ps und 30 ps. Kabelanbieter erklären diese Schwankungsbreite mit Variationen, die beim Schneiden der Kabel und der Montage der SMA-Steckverbinder entstünden, sowie mit εr-Schwankungen von einem Los zum anderen.

Viele Koaxialkabelhersteller bieten phasenangepasste Kabel mit vorgegebenen, angepassten Laufzeitfenstern von 1 ps, 2 ps oder 3 ps an. In der Regel sind die Kabel umso teurer, je genauer die Laufzeitanpassung ist. Für die Produktion von Kabeln mit einer auf 3 ps genauen Laufzeit ergänzen die Hersteller ihre Prozesse zur Kabelkonfektionierung oft durch mehrere Laufzeitmessungs- und Kabelkürzungsschritte, was natürlich höhere Produktionskosten und eine geringere Fertigungsausbeute mit sich bringt.

Jobangebote+ passend zum Thema

Laufzeit als Funktion der Kabelbiegung

Das Biegen von Koaxialkabeln verändert ihre Signallaufzeit. Die Datenblätter der Kabelanbieter enthalten häufig eine Angabe des Phasenfehlers für eine 90-°-Biegung mit einem bestimmten Biegeradius und für eine bestimmte Frequenz. Zum Beispiel kann für eine 90-°-Biegung bei 18 GHz eine Phasenänderung um 8 ° angegeben sein, was gemäß Gleichung 5 einer Laufzeit von ungefähr 1,2 ps entspricht.

Laufzeiteinflüsse durch Montage und SMA-Steckverbinder

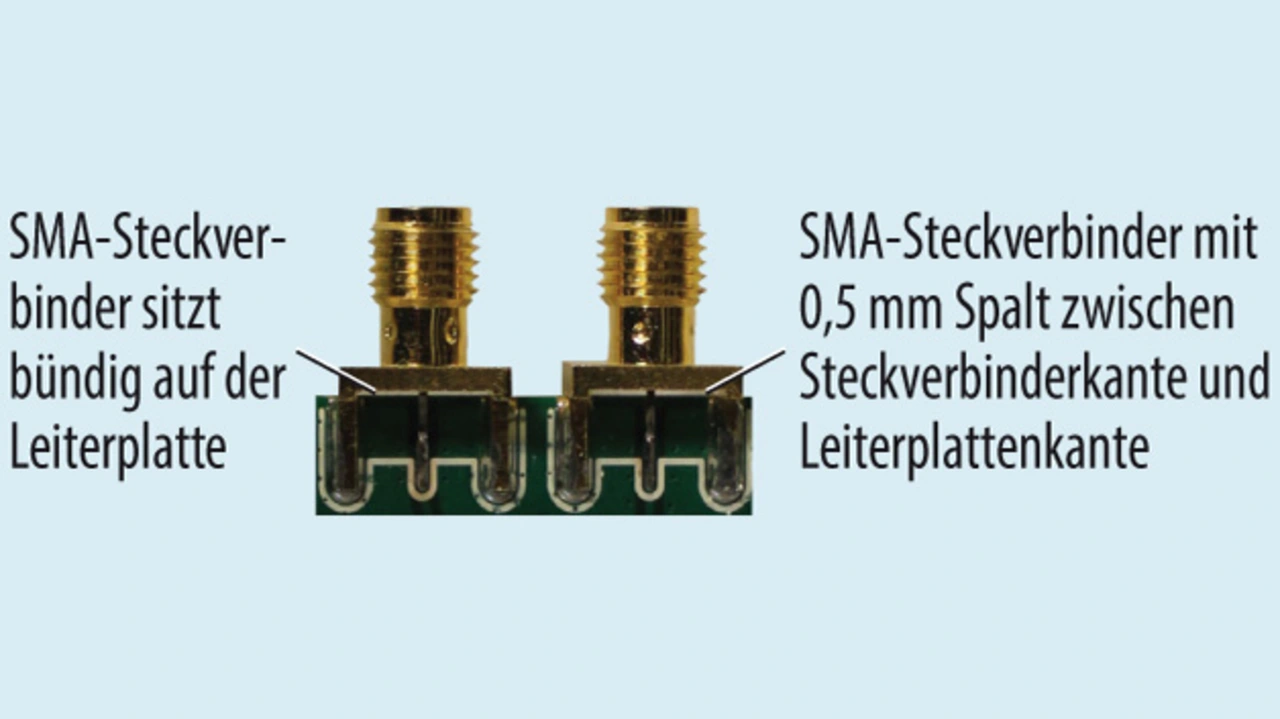

Montagetoleranzen beim Einbau von SMA-Steckverbindern am Leiterplattenrand können größere Laufzeitunterschiede zwischen verschiedenen Taktpfaden verursachen (Bild 4). Fehler dieser Art werden meist nicht gemessen und sind deshalb schwierig zu quantifizieren. Dennoch ist es vernünftig anzunehmen, dass durch diesen Effekt eine zusätzliche Laufzeitabweichung von 1 ps bis 3 ps zwischen den Taktpfaden entstehen kann.

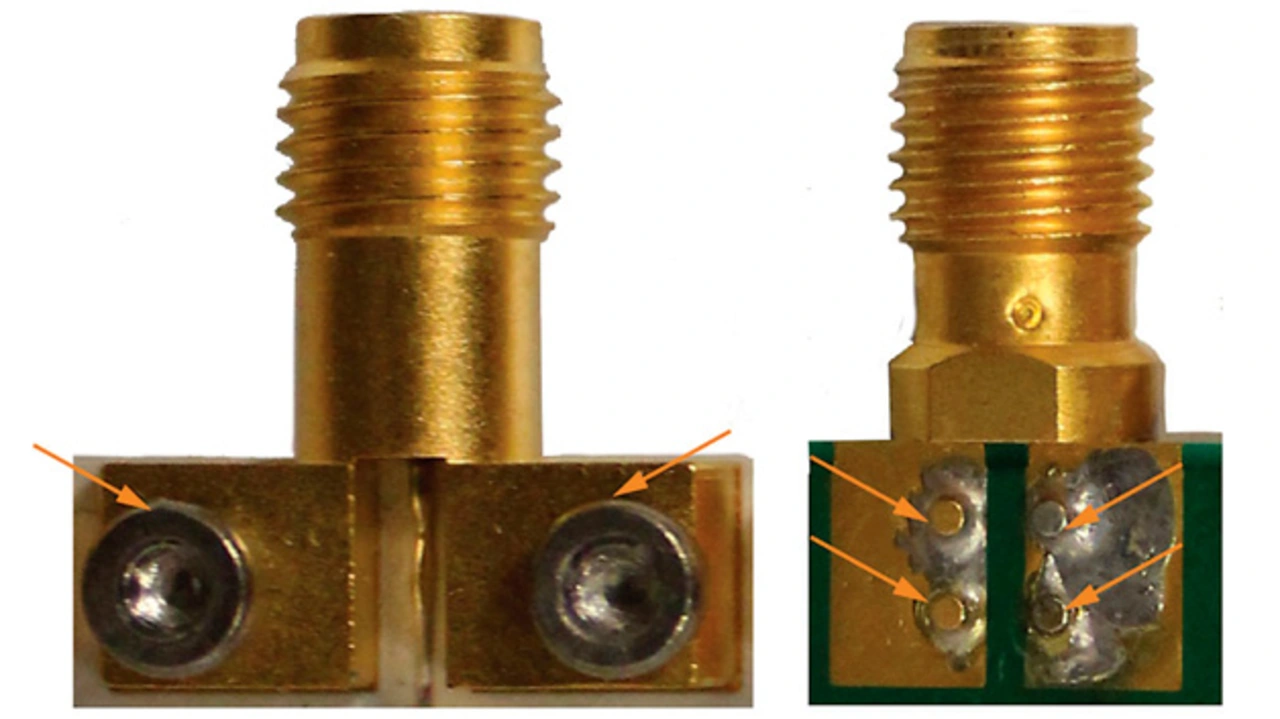

Eine Möglichkeit, die auf Montagetoleranzen von SMA-Steckverbindern zurückzuführenden Laufzeitabweichungen anzugleichen, ist die Wahl von SMA-Steckverbindern mit Einstellmöglichkeiten (Bild 5). Hier sind allerdings Abstriche zu machen, denn SMA-Steckverbinder mit Einstellmöglichkeiten sind in der Regel für höhere Frequenzen spezifiziert und deshalb teurer.

Hersteller von SMA-Steckverbindern empfehlen häufig ein PCB-SMA-Layout für die für höhere Frequenzen ausgelegten SMA-Steckverbinder. Allein diese Layout-Empfehlung kann den Mehrpreis rechtfertigen, da es eine Leiterplatten-Revision einsparen kann, besonders wenn die Taktfrequenz größer als 5 GHz ist.

Leiterplattenübergreifende Laufzeitanpassung

Als fünfte Fehlerquelle, die Laufzeitänderungen herbeiführen kann, kommt die herstellungsprozessbedingte Schwankung von εr über verschiedene Leiterplatten hinzu. Informationen über die fertigungsbedingte Streuung von εr geben die Leiterplattenhersteller.

Zum Beispiel kann der εr-Wert von FR-4 zwischen 4,35 und 4,8 schwanken [6]. Die Extremwerte dieses Toleranzbereichs ergeben eine mögliche Laufzeitdifferenz (ΔtS) von 35 ps für jeweils eine 10 cm lange Streifenleitung auf verschiedenen Leiterplatten. Die Datenblätter weiterer Basismaterialien weisen einen kleineren typischen Bereich für εr aus. Im Datenblatt zu Rogers 4003C etwa ist ein εr-Bereich von 3,38 ±0,05 angegeben. Mit den Extremwerten dieses Toleranzbereichs reduziert sich der mögliche Laufzeitunterschied (ΔtS) bereits auf 9 ps für eine jeweils 10 cm Streifenleitung auf verschiedenen Leiterplatten.

Taktversatz infolge von Takt-ICs

Taktsignale für Umsetzer (ADU, DAU) wurden in der Vergangenheit von mehreren Taktgeneratoren-ICs erzeugt. In den Datenblättern dieser Taktgeneratoren war der jeweilige Taktversatz angegeben, der je nach dem verwendeten IC zwischen 5 ps und 50 ps betrug. Nach dem Kenntnisstand des Autors bot bei Redaktionsschluss keiner der auf dem Markt angebotenen GHz-Taktgenerator-ICs mit mehreren Ausgängen die Möglichkeit, die Signallaufzeit für jeden Ausgang einzeln einzustellen.

Je mehr sich Umsetzer mit Taktfrequenzen von über 6 GHz durchsetzen, umso mehr werden PLLs/VCOs mit einem oder zwei Ausgängen zur bevorzugten Wahl werden. Der Vorteil der PLL/VCO-ICs mit einem Ausgang besteht darin, dass Methoden entwickelt wurden, mit denen die Laufzeit zwischen Referenzeingang und Taktausgang in Schritten von kleiner als 1 ps eingestellt werden kann. Die Möglichkeit, diese Einstellung für jedes Taktsignal einzeln vorzunehmen, gestattet es Entwicklern, ihr System zu kalibrieren, um den Taktversatz zu minimieren – auf unter 1 ps.

Diese Methode der Taktversatzkalibrierung auf Systemebene kann potenziell alle in diesem Aufsatz behandelten Probleme, die zu einem Taktversatz führen, und den Aufwand zum Ausgleich von Leiterplatten-, Kabel- und Steckverbinder-Laufzeitabweichungen entschärfen. Alles in allem kann die elektronische Kalibrierung des Taktversatzes zu niedrigeren Materialkosten für das System führen.

9 Tipps gegen Laufzeitabweichungen

Literatur

[1] Literature, Rogers Corporation, www.rogerscorp.com/acs/literature.aspx

[2] Hartley, R.: Base Materials for High Speed, High Frequency PC Boards. Konferenzband PCB West, März 2002.

[3] Johnson, H.: Skin Effect Calculation. Signal Cosulting, Inc, 1997, www.sigcon.com/Pubs/misc/skineffect-calculations.htm

[4] Johnson, H.: Nickel-Plated Traces. High Speed Digital Design Online Newsletter, 2002, Ausgabe 6, www.sigcon.com/Pubs/news/5_6.htm.

[5] Johnson, H.: Nickel Matters. EDN, 23. Oktober 2012, www.edn.com/electronics-blogs/signal-integrity/4399192/Nickel-matters

[6] FR-4. Microwaves101.com, www.microwaves101.com/encyclopedias/fr-4

Der Autor

Chris Pearson

absolvierte ein Studium an der Purdue University in West Lafayette, Indiana, USA, mit einem Diplom in Elektrotechnik. Zurzeit ist er bei Analog Devices als leitender Applikationsingenieur in der Taktgeneratoren-Gruppe für breite Anwendermärkte tätig und arbeitet hier schwerpunktmäßig an der Taktung von schnellen AD- und DA-Umsetzern.

christopher.pearson@analog.com

- Neun Tipps zum Minimieren von Laufzeitabweichungen

- Laufzeit als Funktion der Frequenz

- Laufzeitangepasste Kabel