Open-Source Hardware

Turbo für RISC-V-Prozessorkern

Fortsetzung des Artikels von Teil 1

Speicher, Debug Controller und Platform Interrupt Controller

Der Prozessorkern SweRV EH1 unterstützt Data Closed Couple Memory (DCCM) und Instruction Closed Couple Memory (ICCM) in der traditionellen Harvard-Architektur sowie einen konfigurierbaren Befehls-Cache (iCache). Der iCache kann in Größen zwischen 32 KB und 256 KB konfiguriert werden. Er ist ein vierfach assoziativer Cache mit vier Bänken von Cache-Daten, mit einer Zeilengröße von 64 Bytes. Die Cache-Zugriffe erfolgen über eine Pipeline und können in jedem Taktzyklus erfolgen. Die Debug-Logik und der Debug-Port sind nach den RISC-V-Debug-Spezifikationen [8] implementiert.

Jobangebote+ passend zum Thema

Vorhersage von Sprunganweisungen

Für die Vorhersage von Sprüngen unterstützt der Prozessorkern SweRV EH1 die Sprungvorhersagetechnik gshare. Sie bietet einen guten Kompromiss zwischen Komplexität und Genauigkeit der Vorhersage bei Anwendungen für eingebettete Systeme [9]. Die Größen des Branch Target Buffer (BTB) und der Branch Prediktor Table (BPT) sind unabhängig voneinander mit bis zu 512 bzw. 2048 Registern konfigurierbar. Sprünge, die im BTB getroffen werden, führen zu einer Verzögerung von einem Zyklus, wogegen Sprünge, die in der primären (EX1) oder sekundären (EX4) ALU falsch vorhergesagt werden, zu einer Verzögerung von vier bzw. sieben Zyklen führen.

Leistungs-Benchmark

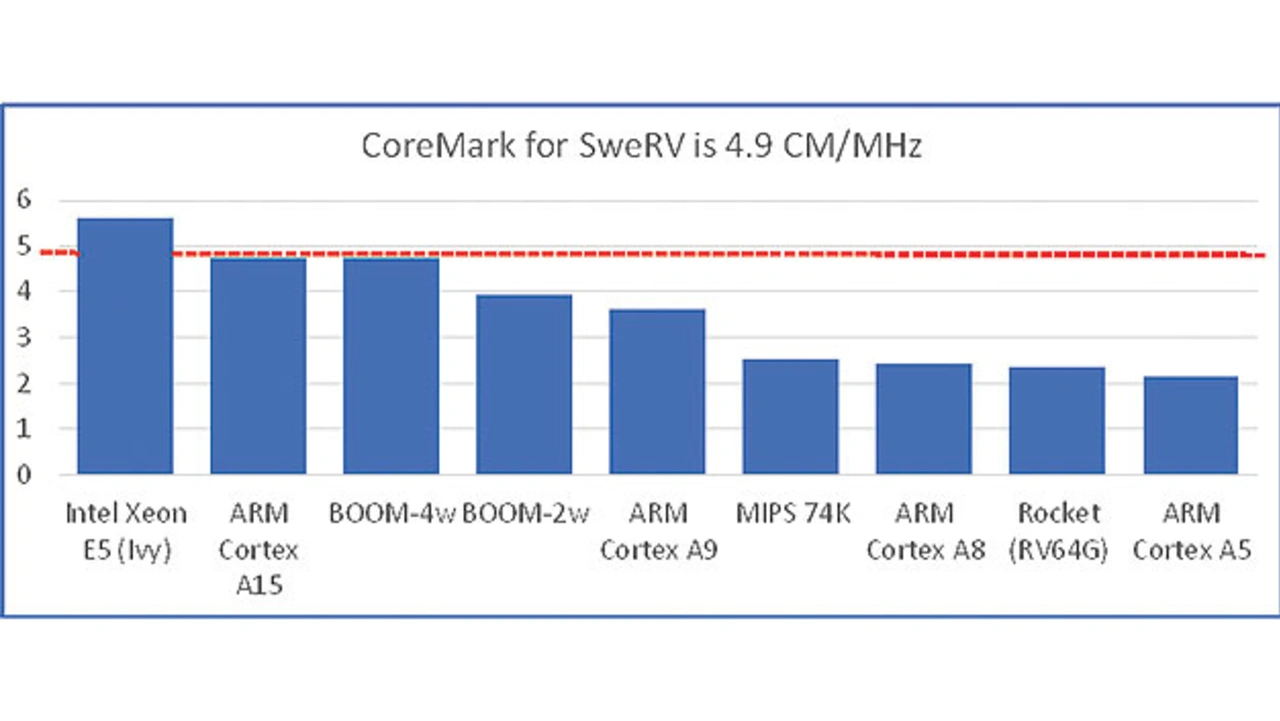

Es ist schwierig, einen Benchmark zu wählen, der eine Vielzahl von Anwendungsfällen und Anwendungen realistisch abbildet. Denn die Spannweite heutiger Applikationen reicht von kleinen IoT-Anwendungen bis hin zu neuronalen Netzwerken für Industrie- und Automobilanwendungen. Western Digital hat sich für den CoreMark-Benchmark [10] entschieden, der häufig für eingebettete CPU-Kerne verwendet wird, um die Leistungsfähigkeit des Prozessorkerns SweRV EH1 zu bewerten.

Das Ergebnis des Benchmarks ist in Bild 3 dargestellt. Der Prozessorkern SweRV EH1 erreicht einen Wert von 4,9 Coremark pro MHz, womit er die Leistung vieler kommerzieller Prozessorkerne für eingebettete Systeme sowie vieler anderer RISC-V-Prozessorkerne übertrifft [11]. Die höhere Rechenleistung ist eine Folge der Dual-Issue-Architektur und der Verfügbarkeit von vier ALUs.

Ein weiterer Benchmark, der häufig für eingebettete Systeme verwendet wird, ist Dhrystone [12]. Durch eine optimierte String-Kopierfunktion konnte Western Digital mit dem SweRV EH1 bei diesem Benchmark einen Wert von 2,9 Dhrystone MIPS/MHz erreichen.

SSD-Controller Anwendungen

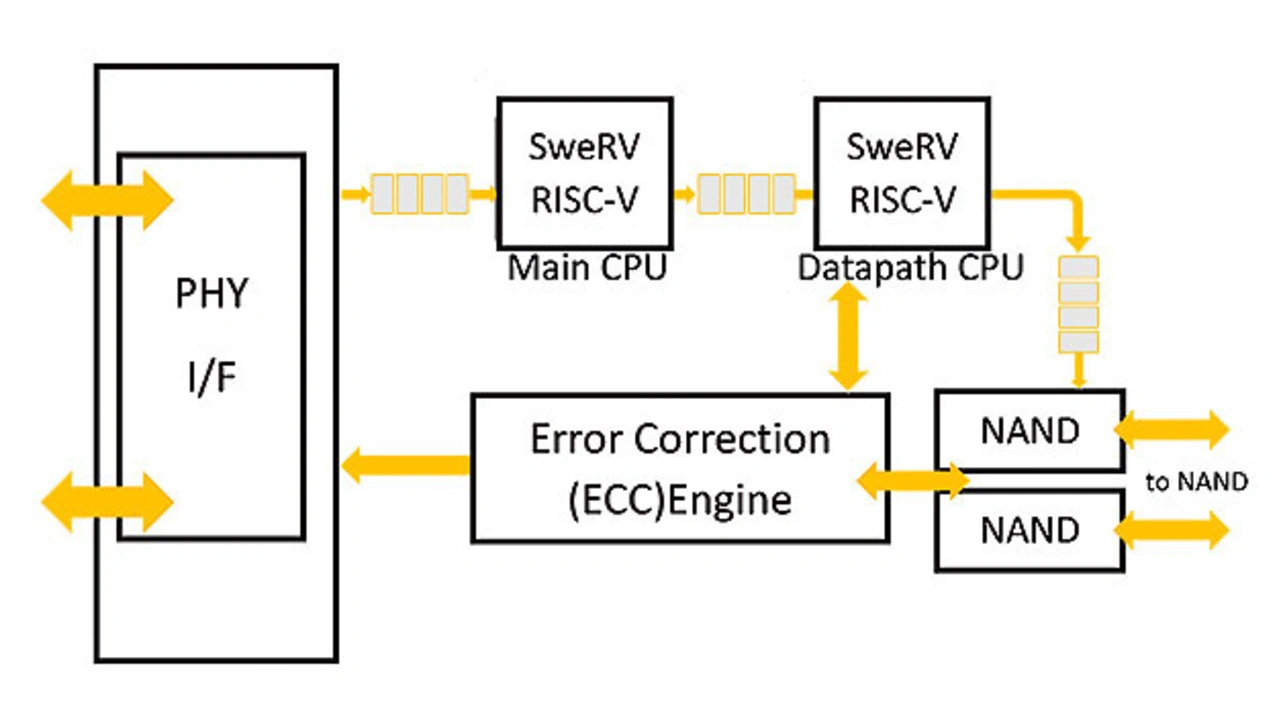

Typischerweise enthalten SSD-Laufwerke (SSD, Solid State Disk) einen Flash-Controller als System on Chip (SoC), der das NAND-Flash-Array auf dem Modul verwaltet und dem Host-Computer eine E/A-Schnittstelle zu fehlerfreien Blöcken bietet. Eine typische Schaltung für einen Flash-Controller-SoC zeigt Bild 4. Der Haupt-CPU-Kern verwaltet die Host-Controller-Schnittstelle und stellt dem Host-Computer fehlerfreie Blöcke zur Verfügung. Die Datenpfad-CPU koordiniert die Aktionen der NAND-Flash-Module, die von den eigentlichen NAND-Flash-ICs lesen und schreiben, und stellt sicher, dass die Daten beim Schreiben in das NAND-Flash-IC mit einem Fehlerkorrekturcode (ECC) codiert werden. Sie vergleicht nach dem Lesen der Daten die gespeicherten ECC-Werte mit den aus dem NAND-Flash-IC gelesenen Werten, um sicherzustellen, dass die Daten fehlerfrei sind. Western Digital hat SweRV-EH1-Prozessorkerne für die Datenpfad-CPUs eingesetzt.

Weiterentwicklung der SweRV-Prozessorkerne

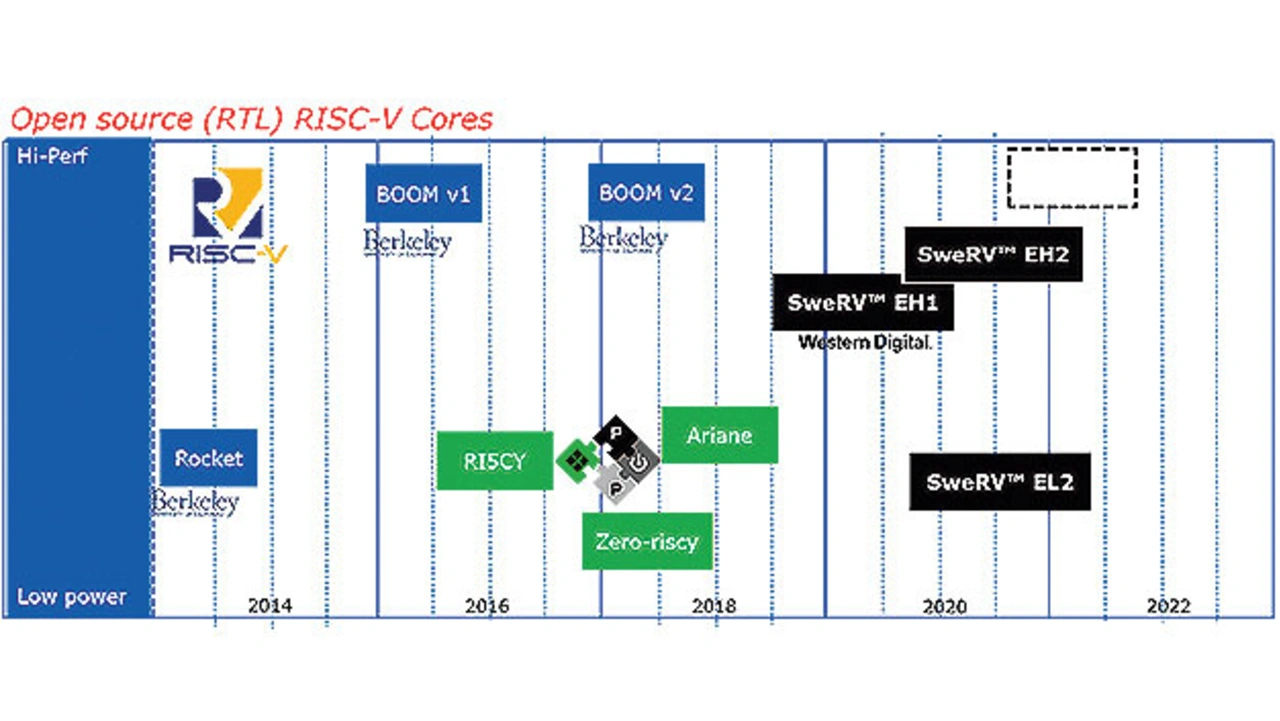

Die Roadmap für SweRV-Prozessorkerne in Bild 5 zeigt die zweite Generation SweRV EH2 und EL2, die im Dezember 2019 vorgestellt wurden. SweRV EH2 behält den Pipeline-Aufbau des SweRV EH1 bei, führt aber Multi-Threading ein.

Dies ermöglicht es, zwei RISC-V-Prozessorkerne dem Host zur Verfügung zu stellen, wobei die Si-Fläche und die Leistungsaufnahme nahezu gleich bleiben. Für viele sehr E/A-intensive Anwendungen kann sich diese Art der Konfiguration als sehr effektiv in Bezug auf Rechenleistung zu Leistungsaufnahme und Rechenleistung zu Fläche erweisen.

Zusätzlich zur Steigerung der Rechenleistung der ersten SweRV-Generation hat Western Digital mit SweRV EL2 eine Low-Power-Version entwickelt – ein kleiner SweRV EH1 mit vierstufiger Pipeline. SweRV EL2 ist ein voll funktionsfähiger RISC-V-Prozessorkern, der für SoC-Subsysteme wie Sequenzer oder Zustandsmaschinen (Finite State Machine, FSM) optimiert ist, bei denen geringe Größe und hohe Betriebsfrequenz unerlässlich sind. Der Source-Code und die Dokumentation sind auf den GitHub-Servern im Bereich der CHIPS Alliance [4] erhältlich.

Literatur

[1] Patterson, D. A.; Hennessy, J. L.: Computer Organization and Design – RISC-V Edition: The Hardware Software Interface. Morgan Kaufmann, 2017, ISBN: 9780128122754.

[2] Internetsite der Fa. SiFive, Inc., www.sifive.com.

[3] Krewell, K.: Western Digital Gives A Billion Unit Boost To Open Source RISC-V CPU. Forbes, 6.12.2017, www.forbes.com/sites/tiriasresearch/2017/12/06/western-digital-gives-a-billion-unit-boost-to-open-source-risc-v-cpu/#a7c8ecf2266e.

[4] SweRV EH1 core. chipsalliance / Cores-SweRV, https://github.com/chipsalliance/Cores-SweRV.

[5] Rocket Chip Generator. chipsalliance / rocket-chip, https://github.com/chipsalliance/rocket-chip.

[6] pulp-platform. https://github.com/pulp-platform.

[7] Johnson, M.: Superscalar microprocessor design. Englewood Cliffs, N.J. : Prentice Hall, 1991, Kapitel 3.

[8] Working Draft of the RISC-V Debug Specification Standard. riscv / riscv-debug-spec, https://github.com/riscv/riscv-debug-spec.

[9] McFarling, S.: Combining Branch Predictors. Western Research Laboratory, Juni 1993, www.hpl.hp.com/techreports/Compaq-DEC/WRL-TN-36.pdf.

[10] CoreMark an EEMBC Benchmark. Embedded Microprocessor Benchmark Consortium, www.eembc.org/coremark.

[11] Celio, C.; Patterson, D. A.; Asanovic, K.: The Berkeley Out-of-Order Machine (BOOM): An Industry-Competitive, Synthesizable, Parameterized RISC-V Processor. University of California at Berkeley, Technical Report No. UCB/EECS-2015-167, 13. Juni 2015, https://www2.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-167.pdf.

[12] Dhrystone Benchmark. EEMBC Certification Laboratories, Whitepaper, www.eembc.org/techlit/datasheets/ECLDhrystoneWhitePaper2.pdf.

Der Autor

Zvonimir Z. Bandić

ist Mitglied im Forschungsteam und Senior Director der Abteilung für Plattformtechniken der nächsten Generation bei Western Digital Corporation in San Jose, USA.

Er erhielt seinen Bachelor in Elektrotechnik 1994 von der Universität Belgrad, Jugoslawien, und seinen Master (1995) und PhD (1999) in angewandter Physik vom California Institute of Technology (Caltech), Pasadena, USA, auf dem Gebiet neuartiger elektronischer Schaltungen auf der Basis von Halbleitern mit breitem Bandabstand.

Derzeit konzentriert Bandić sich auf neue nichtflüchtige Speichertechniken – PCM (Phase-Change Memory), ReRAM (Resistive Random Access Memory), MRAM (Magnetoresistive Random Access Memory) – für verteilte Speicheranwendungen in Rechenzentren, einschließlich RISC-V-basierter CPU-Techniken, In-Memory Computing (IMC), den direkten Speicherzugriff über Netzwerke (RDMA, Remote Direct Memory Access) und Hardwarebeschleuniger für maschinelles Lernen.

Bandić hält über 50 Patente in den Bereichen Halbleiterelektronik, Solid State Disk Controller, Sicherheitsarchitektur und Speichersysteme und hat über 50 Arbeiten veröffentlicht. Er ist Vorsitzender der CHIPS Alliance, Vorsitzender des OpenCAPI Consortium und Vorstandsmitglied der RISC-V-Standardisierungsorganisation.

zvonimir.bandic@wdc.com

- Turbo für RISC-V-Prozessorkern

- Speicher, Debug Controller und Platform Interrupt Controller