Cypress Semiconductor

Sicherheit in IoT-Geräten

Fortsetzung des Artikels von Teil 1

Erforderliche Kernfunktionen für die Sicherheit

Zu jeder der sechs STRIDE-Bedrohungskategorien gibt es entsprechende Typen von Sicherheitsanforderungen (siehe Abbildung 1). Darüber hinaus hängt die Sicherheit eines IoT-Geräts von drei Elementen ab:

- Sicherheitsrichtlinien – sie definieren, welche Sicherheitsanforderungen gelten, um den System-, den Netzwerk- bzw. den Datenzugang herzustellen.

- Kryptografie – arithmetische Algorithmen zur Implementierung verschiedener Typen von Sicherheitsanforderungen.

- Beständigkeit gegen Datenmanipulation – die Fähigkeit eines Systems, Kryptografie auszuführen und seine Politiken durchzusetzen, ohne empfindliche Informationen preiszugeben oder verändert zu werden.

Gewöhnlich wird zuerst über die Sicherheitsrichtlinien eines IoT-Geräts und seiner Anwender entschieden. Als nächstes müssen die Systementwickler festlegen, ob die Systemanforderungen, die für die Kryptografie und Beständigkeit gegen Datenmanipulation erforderlich sind, sich mit dem Mikrocontroller des IoT-Geräts adäquat implementieren lassen. Das führt zu den folgenden Fragen:

- Können meine kryptografischen Schlüssel sicher gespeichert werden?

- Ist eine Hardwarebeschleunigung für kryptografische Standardalgorithmen, wie RSA, ECC, AES und SHA, verfügbar?

- Ist ein echter Zufallszahlengenerator (TRNG) vorhanden? Ist er zertifiziert?

- Kann physikalische Sabotage am IoT-Gerät erkannt werden?

Bis heute ist die Verfügbarkeit dieser Funktionen auf diskrete Spezial-ICs beschränkt geblieben. Die rasche Verbreitung von IoT-Geräten führt jedoch zu einer Nachfrage nach MCUs, die diese und andere Funktionen enthalten, um die besonderen Anforderungen des IoT zu erfüllen.

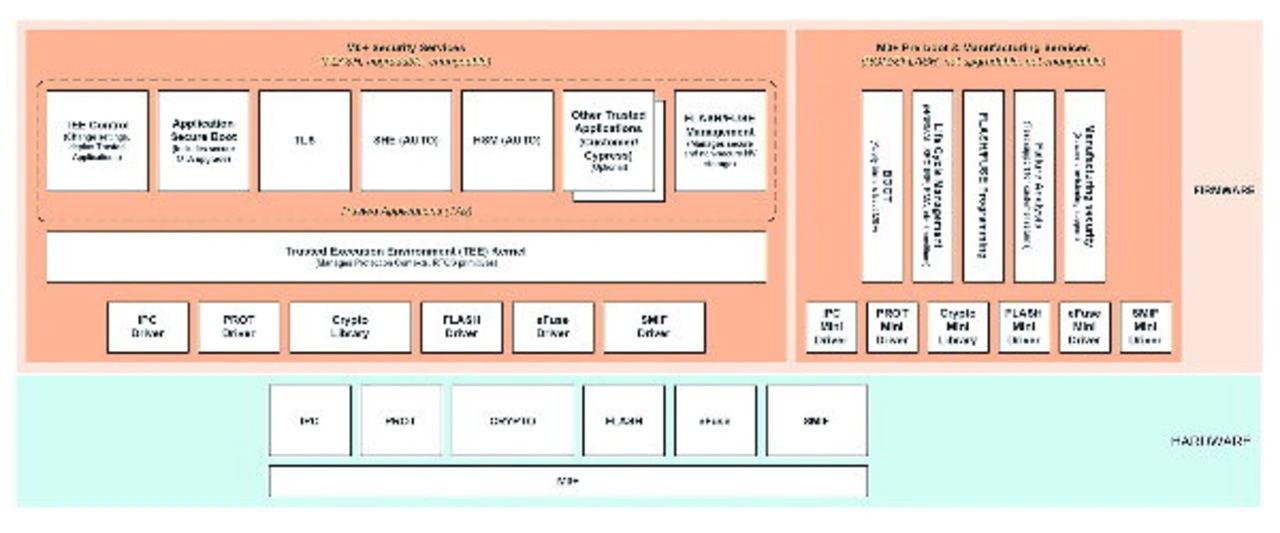

Genau auf diese Anforderungen zielt Cypress Semiconductor mit seiner neuen MCU-Familie PSoC 6. In diesen Komponenten ist ein niedriger Energieverbrauch mit der für IoT-Geräte benötigten hohen Prozessorleistung und fortschrittlicher Sicherheit auf mehreren Ebenen für die speziellen Bedrohungen im IoT kombiniert.

Die PSoC-6-MCUs basieren auf einer Dual-Core-Architektur:

- ein leistungsstarker Cortex-M4-Prozessorkern, der rechenintensive Aufgaben schnell ausführen kann und anschließend in einen Abschaltmodus mit sehr geringem Energieverbrauch wechselt;

- ein Cortex-M0+-Prozessorkern mit sehr niedrigem Energieverbrauch, der einfache, immer laufende Funktionen ausführt, z.B. der Betrieb als Sensor-Hub oder zum Management einer BLE-Verbindung, und das bei sehr niedriger Leistungsaufnahme.

Die PSoC-6-MCU-Architektur nutzt die Verfügbarkeit von zwei Kernen, um auf der Hardware-Ebene gesicherten Speicher bereitzustellen.

Eine Single-Core-MCU kann nur mit einem einzigen Adressraum arbeiten. In diesem Bereich werden neben der regulären Firmware auch sichere Daten wie die Schlüssel gespeichert. Eine Echtzeit-Überwachungsfunktion (gewöhnlich Teil eines RTOS) verwaltet dabei die sicheren Adressen im Normalbetrieb so, dass nur autorisierte Programme Zugriff darauf erhalten.

Bei PSoC 6 kann die Zugangskontrolle auf der Architekturebene konfiguriert werden, bevor die MCU in den Normalbetrieb geht. So kann z.B. ein Bereich des gemeinsam genutzten Speichers so konfiguriert werden, dass nur der Cortex-M0+-Kern darauf zugreifen kann. Auf diese Weise können die PSoC-6-MCUs Hardware-basierten, gesicherten Speicher als zusätzliche Schutzebene gegen unbefugten Zugriff bereitstellen (Abbildung 2).

PSoC-6-MCUs bieten außerdem einen eigenen Hardware-Beschleuniger-Block, der die bekannten Kryptografiealgorithmen AES, RSA, ECC und SHA unterstützt und einen TRNG bereitstellt. Wie beim On-Chip-Speicher lässt sich der Zugriff auf diesen Block auf der Architekturebene kontrollieren.

Und schließlich enthalten die PSoC-6-MCUs auch noch Funktionen, mit denen eine Sabotage am Gehäuse des Produkts erkannt werden kann: programmierbare Analogblöcke, die so konfiguriert werden können, dass sie Spannung und Strom sowie den Takt überwachen, während die Cypress-CapSense-Technologie zur kapazitiven Berührungserkennung dazu herangezogen werden kann, unbefugte Versuche zum Öffnen des Gehäuses zu erkennen.

Sicherheit speziell für das IoT

Heutige MCUs für Mainstream-Anwendungen im IoT sind nicht mit den Funktionsblöcken ausgestattet, die einerseits eine Hardware-basierte sichere Speicherung und andererseits eine Hardware-Beschleunigung für Kryptografie ermöglichen und gleichzeitig auch noch mit Funktionen zur Sabotageerkennung aufwarten. Die durch das IoT entstandenen neuen Anforderungen verlangen nach speziell für das IoT konzipierten MCUs, die über die Sicherheitsfunktionen verfügen, die IoT-Geräte benötigen, aber auch den Anforderungen hinsichtlich niedrigen Energieverbrauchs und Prozessorleistung gerecht werden.

Jobangebote+ passend zum Thema

- Sicherheit in IoT-Geräten

- Erforderliche Kernfunktionen für die Sicherheit