Mikroprozessor-IP für Funk-SoCs

Neuer MIPS-Prozessor I7200 für LTE und 5G

50 Prozent mehr Rechenleistung, kurze Reaktionszeiten für Echtzeit-Anwendungen und effizientes Parallelrechnen listet MIPS als Vorteile seines neuen I7200-Prozessor-IPs. Es ist zugleich der erste Prozessor mit der neuen Befehlssatzarchitektur nanoMIPS.

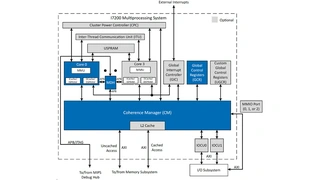

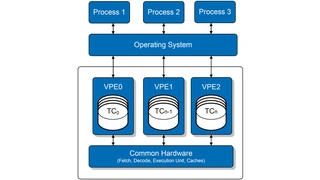

Als Teil der 32-bit I-Prozessorfamilie von MIPS basiert auch der neue I7200 auf der von MIPS entwickelten Multi-Threading-Technik. Sie ermöglicht nicht nur eine hohe Rechenleistung, sondern ist entscheidend um sehr kurze Latenzzeiten für priorisierte Ereignisse in Echtzeit-Anwendungen für Embedded Systems zu erzielen. Für den Einsatz in Embedded Systems, die hohe Rechenleistung und kurze Reaktionszeiten für Echtzeit-Anwendungen fordern, wurden drei Fähigkeiten bei der Entwicklung des I7200 in den Vordergrund gestellt:

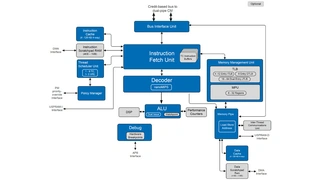

- Simultanes Multi-Theading mit Thread-Priorisierung und Kontextwechsel ohne Umschaltzeit (zero cycle context switching).

- Konfigurierbare Speicherverwaltung – Optionen für eine MMU (Memory Management Unit) mit Übersetzungspuffer (TLB: Translation Lookaside Buffer) oder eine einfachere MPU (Memory Protection Unit) für 32 Speicherbereiche.

- Eng gekoppelte interne Speicher mit schnellem Zugriff – bis zu 1 MB pro Kern – für Befehle, Daten für jeden Kern oder zur gemeinsamen Ausführung.

Mit dem I7200, den MIPS als IP für die Integration in SoCs anbietet, erweitert MIPS seine mittlere Linie von 32-bit-Prozessoren um einen neuen rechenleistungsstarken Mikroprozessor. Kombiniert mit Energieeffizienz zielt MIPS mit dem I7200 auf Anwendungen in SoCs für Breitband-Modems und Smartphones für LTE Advanced Pro und 5G sowie in Kommunikations-SoCs. Für die Steigerung der Rechenleistung um 50 Prozent wird im I7200 nur 20 Prozent mehr Siliziumfläche benötigt.

Jobangebote+ passend zum Thema

Prozessor I7200

Befehlssatzarchitektur nanoMIPS

Mit der neuen Befehlssatzarchitektur nanoMIPS, die erstmals im I7200 eingesetzt wird, ermöglicht MIPS eine besonders kleine Code-Größe. Sie basiert auf variablen Befehlslängen mit 16-bit-, 32-bit- und 48-bit-Befehlen und weiteren Optimierungen. Mit entsprechenden Compilern lässt sich mit nanoMIPS die Code-Größe um bis zu 10 Prozent reduzieren – verglichen mit alternativen Prozessorkernen in vergleichbaren Anwendungen.

Damit lässt sich der Platzbedarf für den Speicher des Systems senken, aber wichtiger für Echtzeit-Anwendungen ist, dass mehr Code in den schnellen internen Speicher des Prozessorkerns passt, um priorisierte Ereignisse und Interrupts mit kurzer Latenz ausführen zu können.

Datenblatt I7200