Siliziumkarbid-MOSFETs

Verbesserte zweite Generation

Seit Anfang 2011 sind MOSFETs aus Siliziumkarbid kommerziell erhältlich. Anfang dieses Jahres ist nun die zweite Generation erschienen. Wo liegen die Unterschiede zu konventionellen Siliziumbausteinen und die Verbesserungen zur Vorgängergeneration?

MOSFETs auf der Basis von Siliziumkarbid (SiC) gibt Leistungselektronikern die Gelegenheit, die Energieeffizienz ihrer Systeme auf ein Niveau zu heben, das mit den existierenden Siliziumbausteinen nicht erreichbar war. Dank dieser Effizienzsteigerung gelang es den Entwicklern, die Verlustleistung zu reduzieren. Damit konnten sie beispielsweise den Energieertrag von Wechselrichtern sowohl für den PV-Bereich (Fotovoltaik) als auch für andere Arten erneuerbarer Energien verbessern und außerdem die Kosten und die Komplexität der Wärmemanagement-Lösungen verringern.

Darüber hinaus sind mit SiC-Leistungshalbleitern höhere Schaltgeschwindigkeiten möglich, was wiederum die Verwendung von kleiner dimensionierten induktiven und kapazitiven passiven Bauelementen gestattet. Unter dem Strich lassen sich dadurch deutlich kleinere, leichtere und kostengünstigere Systeme realisieren. Die Anbieter von Industrienetzteilen, PV-Wechselrichtern und sogar von Hilfsstromversorgungen für Eisenbahnfahrzeuge konnten Volumen- und Gewichtsreduzierungen von 30 Prozent bis 60 Prozent demonstrieren.

Unterschiede zu Siliziumbausteinen

Über diese ersten wegbereitenden Systeme hinaus besteht die Herausforderung nunmehr darin, die allgemeine Akzeptanz der SiC-Leistungsbausteine weiter voranzutreiben. Die Einführung der zweiten Generation von SiC-MOSFETs durch Cree und andere Anbieter stellt einen wichtigen Schritt in Richtung dieses Ziels dar.

Jobangebote+ passend zum Thema

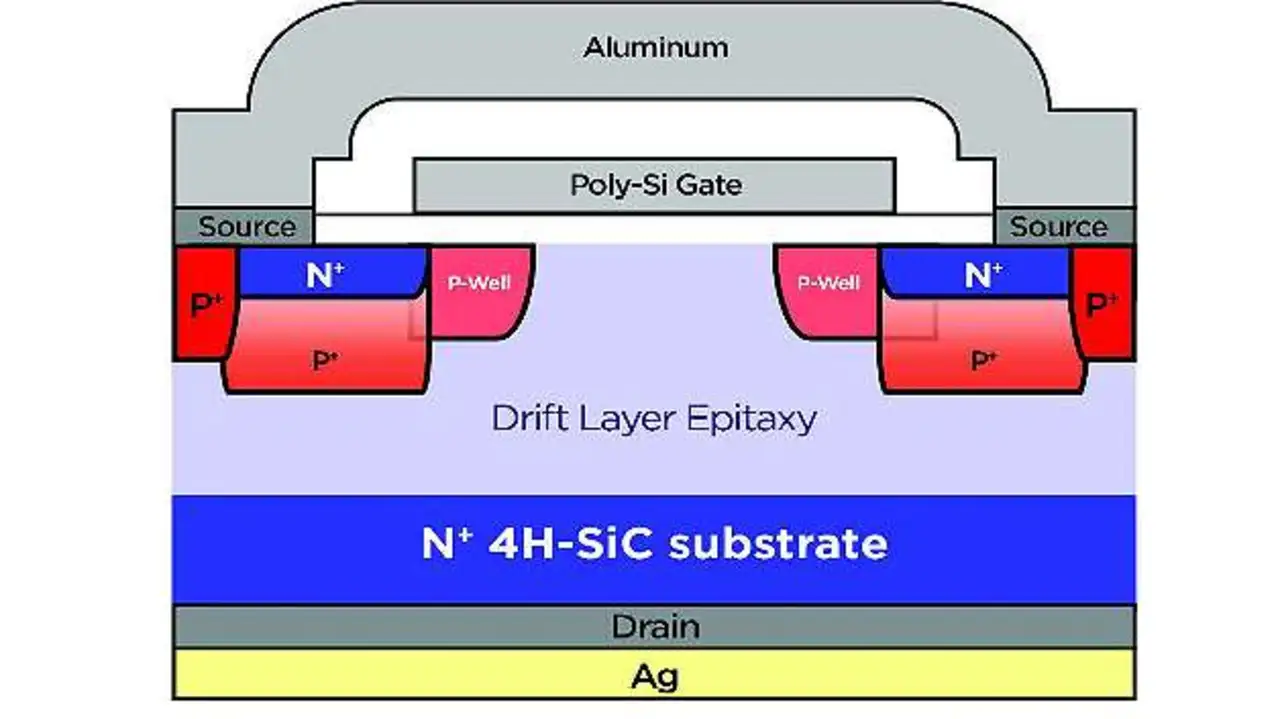

SiC-MOSFETs basieren auf einer planaren DMOS-Topologie (Bild 1), wie sie in ähnlicher Form schon bei den frühen Silizium-MOSFETs verwendet wurde.

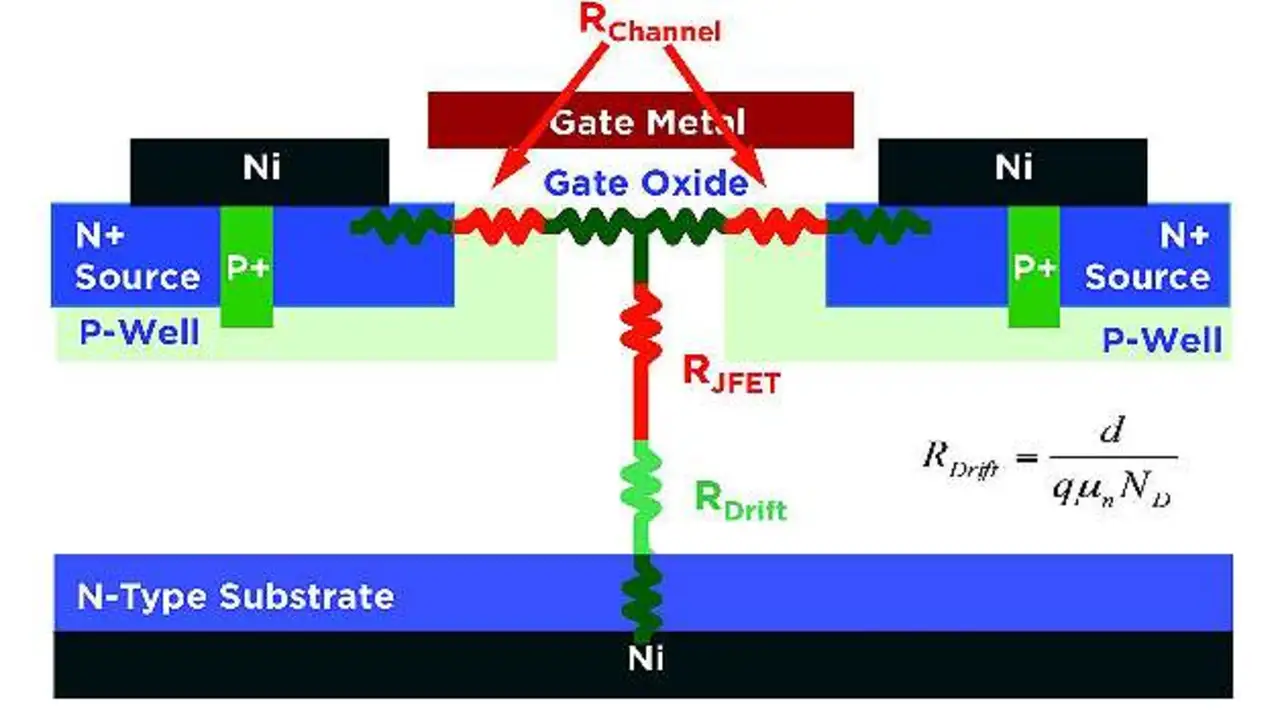

Verständlich werden die von SiC-MOSFETs gebotenen Vorteile, wenn man sich mit den in Bild 2 skizzierten Hauptkenndaten eines solchen Bausteins auseinandersetzt. SiC-MOSFETs sind vom Anreicherungstyp (enhancement mode) und somit selbstsperrend. Wird eine Gate-Spannung angelegt, kann ein Strom von den Source-Anschlüssen durch den Kanal unterhalb des Gates und durch den JFET-Bereich und schließlich durch die Driftregion fließen. Der gesamte Durchlasswiderstand des Bausteins (RDS(on)) entspricht der Summe aus Kanal-, JFET- und Drift-Widerstand. Die Driftregion wird durch die Dicke der abgeschiedenen Epitaxialschicht definiert, deren Dicke sich durch die Sperrspannung des Bausteins im abgeschalteten Zustand bestimmt.

Gegenüber Siliziumbausteinen benötigen SiC-MOSFETs nur ein Zehntel der Driftdicke, um eine bestimmte Sperrspannung zu erreichen. Deshalb dominiert der Driftwiderstand den RDS(on)-Wert von Silizium-MOSFETs, sobald die Sperrspannung mehr als ein paar hundert Volt beträgt. Der höhere Widerstand aber macht es notwendig, die Die-Fläche erheblich zu vergrößern, um einen angemessenen Duchlasswiderstand zu erzielen. Insgesamt führt dies dazu, das Silizium-MOSFETs groß und teuer sind und wegen der hohen kapazitiven Verluste nur für begrenzte Schaltfrequenzen eingesetzt werden können.

Mithilfe der Superjunction-Technologie lässt sich bei Spannungen bis etwa 600 V mit Silizium-MOSFETs eine akzeptable Performance erzielen. Bei höheren Spannungen zieht man jedoch im allgemeinen Silizium-IGBTs vor, um annehmbare Leitungsverluste zu erreichen und das Design bezahlbar zu halten. So erklärt es sich, dass die Mehrzahl der Leistungselektroniksysteme für Spannungen über 600 V inzwischen mit Silizium-IGBTs bestückt wird. IGBTs kombinieren eine hochohmige Gate-Struktur zum Schalten des Bausteins mit einer bipolaren Leitungsregion, um die Verluste pro Flächeneinheit gering zu halten. Diese Kombination ergibt einen Baustein, der sich einfach ansteuern lässt, akzeptable Sperreigenschaften aufweist und geringe Leitungsverluste verursacht.

Ins Hintertreffen geraten Silizium-IGBTs jedoch hinsichtlich der Schaltverluste. Weil die Leistung hauptsächlich über eine bipolare Sperrschicht fließt, muss die in der Sperrschicht gespeicherte Ladung bei jedem Einschalten des Bausteins abgeleitet und »verheizt« werden. Beim Ausschalten müssen die Ladungsträger wieder ausgeräumt werden, was zu erheblichen Tail-Strömen und somit zu hohen Verlusten führt. Die Materialeigenschaften von Siliziumkarbid dagegen erlauben die Verwendung einer unipolaren MOSFET-Struktur für Anwendungen mit hohen Sperrspannungen. Hiermit lassen sich deshalb IGBT-ähnliche Leitungsverluste erzielen, und zwar mit einem kleinen Die mit entsprechend niedriger Kapazität, sodass die soeben beschriebenen, durch Deaktivierungsströme verursachten Verluste hier ausbleiben.

Insgesamt machen die Leitungs- und Schaltverluste bei SiC-MOSFETs nur ungefähr die Hälfte bis ein Fünftel der entsprechenden Verluste bei Si-MOSFETs oder -IGBTs bei 1200 V aus (abhängig vom Systemdesign und der Frequenz). Der Vorsprung ist umso größer, je höher die Sperrspannung ist. SiC-MOSFETs der zweiten Generation für Spannungen von 1200 V und 1700 V befinden sich inzwischen in der Massenfertigung.

Verbesserungen bei der zweiten Generation

Wie bereits erwähnt, ließen sich mit der ersten SiC-MOSFET-Generation deutliche Effizienzsteigerungen erzielen. Zur weiteren Verbesserung der Leistungsfähigkeit wurden die in Bild 2 genannten Widerstände verringert, was die Verluste in den Bauelementen senkte und es möglich machte, kleinere Die-Größen für eine bestimmte Stromstärke zu verwenden. Da der Driftwiderstand durch die geforderte Sperrspannung dominiert wird, sind hier nur schrittweise Verbesserungen möglich.

Die primäre Herausforderung beim SiC-DMOS-Design besteht darin, die Gate-Struktur und die Kanalgeometrien zu verbessern. Ziel ist, die Steilheit (Transkonduktanz) der Gate-Region zu steigern. Dies wurde mithilfe proprietärer Baustein- und Prozessverbesserungen erreicht (siehe Tabelle 1).

| Parameter | CMF20120D (1. Gen.) | C2M0080120D (2. Gen.) |

|---|---|---|

| Chipfläche (relativ) | 100 % | 65 % |

| RDS(on) (typ.) bei Tj = +25 °C | 80 mΩ | 80 mΩ |

| RDS(on) (typ.) bei Tj = +125 °C | 95 mΩ | 123 mΩ |

| Gate-Spannung | -5 V/+25 V | -10 V/+25 V |

| Schaltverlust (Tj = +150 °C, UDS = 800 V) | 0,78 mJ | 0,56 mJ |

| Gate-Ladung | 91 nC | 49 nC |

| Steilheit | 7,4 A/V | 9,8 A/V |

| Eingangskapazität Ciss | 1,915 pF | 950 pF |

| Ausgangskapazität Coss | 120 pF | 80 pF |

| Miller-Kapazität Crss | 13 pF | 6,5 pF |

| Wärmewiderstand | 0,5 K/W | 0,6 K/W |

Tabelle 1: Performance-Vergleich zwischen den zwei SiC-MOSFET-Generationen (RDS(on) jeweils 80 mΩ)

So weisen die neuen Bauelemente eine um über 30% verbesserte Steilheit auf. Zusammen mit weiteren Verfeinerungen an den Halbleiter-Fertigungsprozessen machte es die höhere Steilheit möglich, die Die-Fläche um über 35% zu verringern. Dies wiederum gestattet es, einen vorgegebenen RDS(on) mit weniger Die-Fläche zu erzielen. Somit passen mehr Chips auf einen Wafer, und die Produktionsausbeute wird potenziell höher. Beides wiederum lässt die Bauelementekosten sinken.

Ein kleinerer Baustein trägt außerdem zu einer besseren Energieeffizienz sowie schnelleren Schalteigenschaften bei. Alle an den Bausteinen vorgenommenen Verfeinerungen, welche die Kanalmobilität verbessern, reduzierten auch die Kapazitäts- und Gate-Ladungswerte. Verringerte Kapazitäten und Gate-Ladungen aber führen zu geringeren Schaltverlusten auf Systemebene (siehe Tabelle 1). Beim Schalten von 800 V bei maximaler Betriebstemperatur entstanden bei den SiC-Bausteinen der ersten Generation um fast 40% höhere Verluste. Die Bauelemente der zweiten Generation schalten wesentlich schneller und verlustärmer und ermöglichen dadurch höhere Schaltfrequenzen, während der Wirkungsgrad des Systems unverändert bleibt oder sich sogar verbessert.

Die geringeren Kapazitäten und höheren Schaltgeschwindigkeiten müssen beim Treiberdesign berücksichtigt werden und können die Störabstrahlung (EMI) beeinflussen. Wegen der schnelleren Schaltvorgänge muss man beim Leiterplatten-Layout und bei der Auswahl der Bauelemente sorgfältiger vorgehen. Unter anderem kann ein externer Gate-Widerstand helfen, etwaiges Schwingen und Funkstörprobleme einzudämmen. Als Hilfestellung hierbei wurden von Cree Applikationsschriften und Treiber-Referenzdesigns herausgegeben. Vergleicht man außerdem den temperaturabhängigen Verlauf des RDS(on) der verschiedenen Bauelemente, so muss darauf hingewiesen werden, dass dieser Parameter bei den neueren Bauelementen stärker mit der Temperatur zunimmt als bei den älteren Produkten. Doch auch bei relativ niedrigen Schaltfrequenzen führen die niedrigeren Schaltverluste der zweiten SiC-Generation dazu, dass die insgesamt entstehenden Systemverluste deutlich sinken.

SiC-Bausteine richtig nutzen

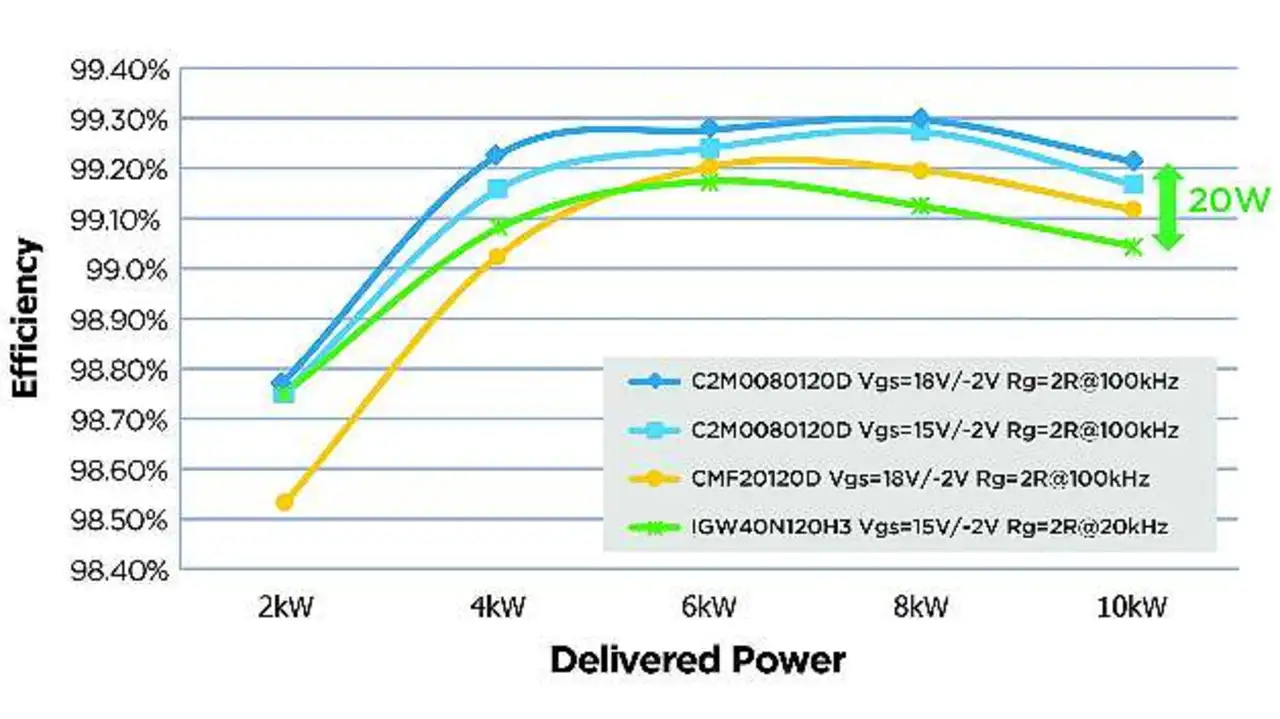

Bild 3 verdeutlicht die relative Performance-Steigerung gegenüber einer IGBT-Lösung in einem Aufwärtswandler mit 10 kW Leistung, den Cree für Kunden im Bereich der PV-Wechselrichter entwickelt hat. Die Grafik gibt Auskunft über den Gesamtwirkungsgrad des Systems über einen weiten Ausgangsleistungsbereich. Man erkennt die starke Effizienzverbesserung mit beiden Generationen von SiC-MOSFETs, und auch die zusätzliche Verbesserung der zweiten Generation gegenüber der ersten ist klar zu sehen. So eindrucksvoll diese Verbesserungen für sich genommen auch sind, ist dennoch hervorzuheben, dass die Silizium-IGBTs mit nur 20 kHz schalten, SiC-Bauteile jedoch mit 100 kHz. Auf der Systemebene sind potenzielle Einsparungen bei den Materialkosten von rund zehn Prozent zu erwarten, wenn die Induktivitäten und Kühlkörper für die höhere Schaltfrequenz und den verbesserten Wirkungsgrad dimensioniert werden.

Als abschließender Aspekt bleibt die Tatsache zu erwähnen, dass die neuen SiC-MOSFETs in größeren Stückzahlen und mit erheblich rationelleren Fertigungsverfahren produziert werden. Die Design- und Prozessverbesserungen bei den neuesten Bauelementen ergeben noch robustere und zuverlässigere kommerzielle Produkte. Deutlich wird dies an den höheren maximalen Sperrschichttemperaturen und erweiterten Spezifikationen für die Gate-Spannungs. Am Vergleich der I/V-Kurven der Datenblätter erkennt man deutlich bessere Performance-Werte bei den unterschiedlichsten Treiberspannungen, sodass sich das Treiberdesign vereinfacht.

Die Hersteller von SiC-Bauelementen sind weiter dabei, Verbesserungen an der Leistungsfähigkeit, dem Portfolio und den Gehäusen vorzunehmen und die Kosten der Bauelemente zu senken. Bei Cree geht man davon aus, dass die weiteren Verbesserungen in Sachen Performance und Preis dazu führen können, dass Siliziumbauelemente in der Leistungselektronik für die unterschiedlichsten Anwendungen noch zügiger von SiC-Produkten verdrängt werden.

Über den Autor:

Paul Kierstead ist Director of Power Marketing bei Cree.

| Siliziumkarbid zum Preis von Silizium |

|---|

|

Bislang haben die hohen Kosten bei der Herstellung von Bauteilen aus SiC ihre breite Einführung verhindert. Daher finden solche Leistungsschalter vorrangig in Nischenmärkten Verwendung, wo Vorteile auf Systemebene die höheren Kosten rechtfertigen. Anvil Semiconductors, ein Spin-out der School of Engineering der Universität Warwick (England), will einen Weg gefunden haben, SiC-Leistungsschalter in hohen Stückzahlen zu produzieren - zu Kosten, die denen von Siliziumbausteinen nahekommen. Das Unternehmen hat einige Technologien für die Produktion von 3C-SiC-Epitaxieschichten auf Siliziumwafern entwickelt. Dadurch umgeht es den Einsatz der sehr teuren SiC-Wafer. |