Rohm: Interview mit SiC-Chef Dr. Ino

Siliziumkarbid weiter auf dem Vormarsch

Fortsetzung des Artikels von Teil 1

Wie hoch ist die FIT-Rate bei Rohm?

Das kann ich Ihnen so leider nicht beantworten, aber ich versichere Ihnen, dass unsere FIT-Rate unter der von Silizium liegt. Wir testen unsere Bauteile in einem beschleunigten Alterungstest. Im Juni 2015 unterzogen wir hunderte unserer SiC-MOSFETs der zweiten Generation aus verschiedenen Fertigungslosen einer ganzen Reihe von verschiedenen beschleunigten Alterungstests. Ein Beispiel dafür ist ein Reverse-Bias-Test mit erhöhter Temperatur für 1000 Stunden mit 780 Bauteilen sowie 3000 Stunden mit 510 Bauteilen. Fakt ist, kein einziger Baustein fiel aus.

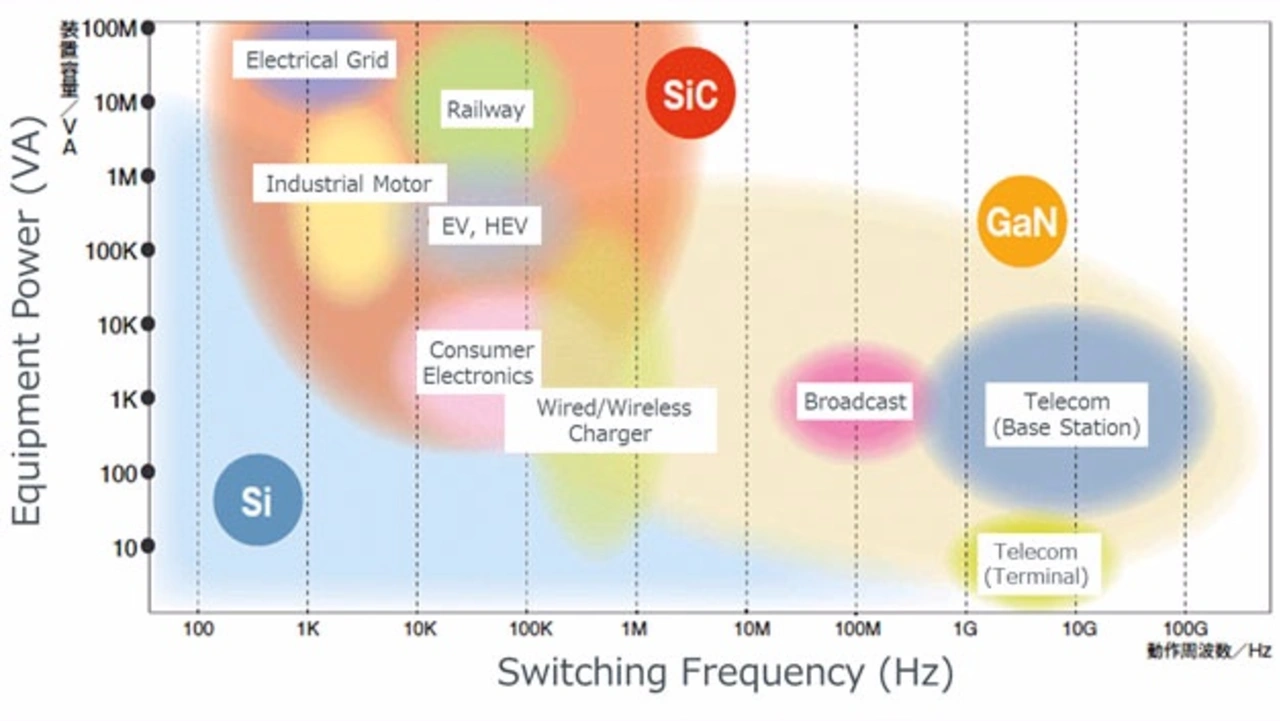

Navitas Semiconductor hat kürzlich einen GaN-Schalter vorgestellt, bei dem die Treiber- und die Schutzschaltung monolithisch in GaN-auf-Silizium integriert ist. Ist so etwas auch bei Siliziumkarbid machbar?

Ja, wir arbeiten in einem Forschungsprojekt daran. Aber ich persönlich glaube nicht, dass das jemals wirtschaftlich zu produzieren ist. Wir bevorzugen daher die Integration zweier Chips in einem Gehäuse – den Treiber klassisch in Silizium, den Schalter in SiC.

Im Juni 2015 begann Rohm mit der Serienfertigung der ersten SiC-Trench-MOSFETs. Was waren die Herausforderungen, so ein Bauteil herzustellen?

Jobangebote+ passend zum Thema

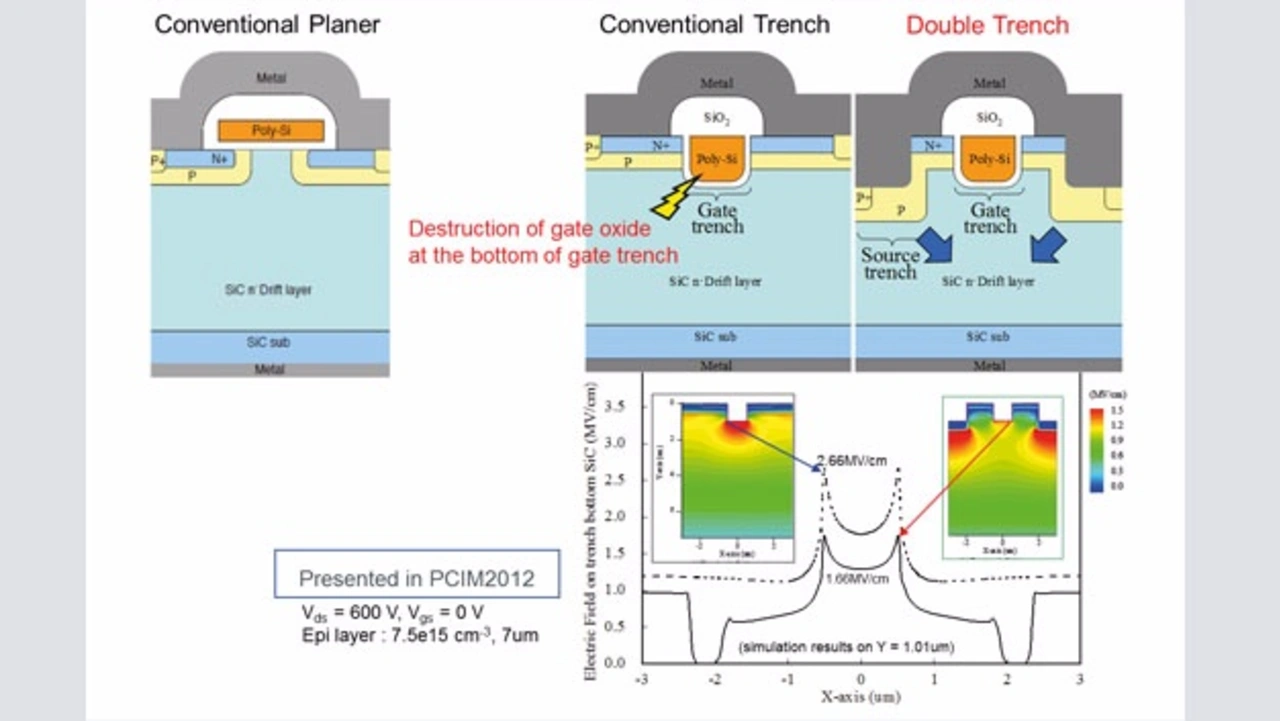

Gegenüber dem Planar-MOSFET der zweiten Generation haben wir den Einschaltwiderstand noch einmal halbieren können. Dies ist nur mit einer wesentlich kleineren Prozessgeometrie möglich, und dann ist es äußerst herausfordernd, die Zuverlässigkeit auf Bauteil- und Prozess¬ebene zu gewährleisten.

Soviel ich weiß, funktioniert die klassische Trench-Technologie, wie sie von Silizium bekannt ist, bei Siliziumkarbid nicht. Können Sie uns das näher erklären?

- Siliziumkarbid weiter auf dem Vormarsch

- Wie hoch ist die FIT-Rate bei Rohm?

- Warum versagt die klassische Trench-Technologie bei SiC?