SiC-Transistoren

Die erste Generation

Auf Grund der überlegenen physikalischen Eigenschaften von SiC kann nun neben Si-Superjunction-Bausteinen und IGBTs eine neue Klasse von Hochspannungs-Transistoren realisiert werden. Geringe statische und dynamische Verluste sowie die monolithische Integration einer Body-Diode sind Vorteile, die sich in Anwendungen wie im Photovoltaikbereich auszeichnen.

Die Auswahl des Bauelementkonzepts ist sowohl für die Zuverlässigkeit als auch für die zu erwartende Leistungsfähigkeit in der Applikation von entscheidender Bedeutung. SiC-MOSFETs oder -JFETs weisen hier zunächst eine vergleichbare Charakteristik auf: Beide Konzepte erlauben schnelle unipolare Schaltvorgänge, wie sie von Si-Superjunction-MOSFETs bekannt sind, in der 1.200-V-Sperrspannungsklasse. Wenn es um den Stand der Technik geht, zeigen MOSFETs und JFETs aber große Unterschiede.

Für Infineon besteht ein wichtiges Entwicklungsziel darin, von der firmeneigenen robusten Dioden-Fertigungslinie zu profitieren, dabei aber Prozesskonzepte zu vermeiden, für die derzeit noch keine Felderfahrungen vorhanden sind. Vor diesem Hintergrund fallen MOSFETs gegenüber den JFETs zurück.

Das liegt vor allem daran, dass der Gate-Oxid-Prozess aufgrund der relativ hohen extrinsischen Defektdichte des SiC-Materialsystems ein hohes Qualitätsrisiko mit sich bringt. Auch wenn intrinsische Zuverlässigkeit und Schwellspannungs-Stabilität vielfach demonstriert wurden, bedarf es einer effektiven und erprobten Screening-Strategie, um eine hohe Auslieferqualität sicherzustellen. Damit scheidet ein MOSFET-Konzept aus, so dass die Frage nach der optimalen JFET-Struktur zu beantworten ist [1].

Vertikaler oder horizontaler Kanal?

Vertikale JFETs haben den Vorteil, dass sie selbstsperrend (normally-off) sind [2]. Allerdings ist eine Ansteuerung mit negativer Spannung zum Ausschalten und einem relativ hohen bipolaren Einschaltstrom erforderlich. Darüber hinaus ist das nutzbare Schwellspannungsfenster zwischen selbstleitender Charakteristik bei null Volt und der Diodenflussspannung von +2,5 V relativ klein.

Es wird zusätzlich durch eine ausgeprägte Barrierendegradation eingeengt, wodurch die Schwellspannung von der anliegenden Sperrspannung abhängig wird. Herstellungsseitig ist es sehr schwierig, die Schwellenspannung in diesem kleinen Prozessfenster zu zentrieren; dies erfordert eine anspruchsvolle Steuerung der kritischen Lithographie- und Strukturierungs-Prozessschritte. Zusätzlich ist es in der vertikalen JFET-Struktur nicht möglich, eine Body-Diode in den Transistor zu integrieren. Ferner tritt eine höhere Koppelung zwischen Gate und Drain auf, was sich deutlich im Verhältnis der Rückwirkungs- zur Ausgangskapazität zeigt [3].

Jobangebote+ passend zum Thema

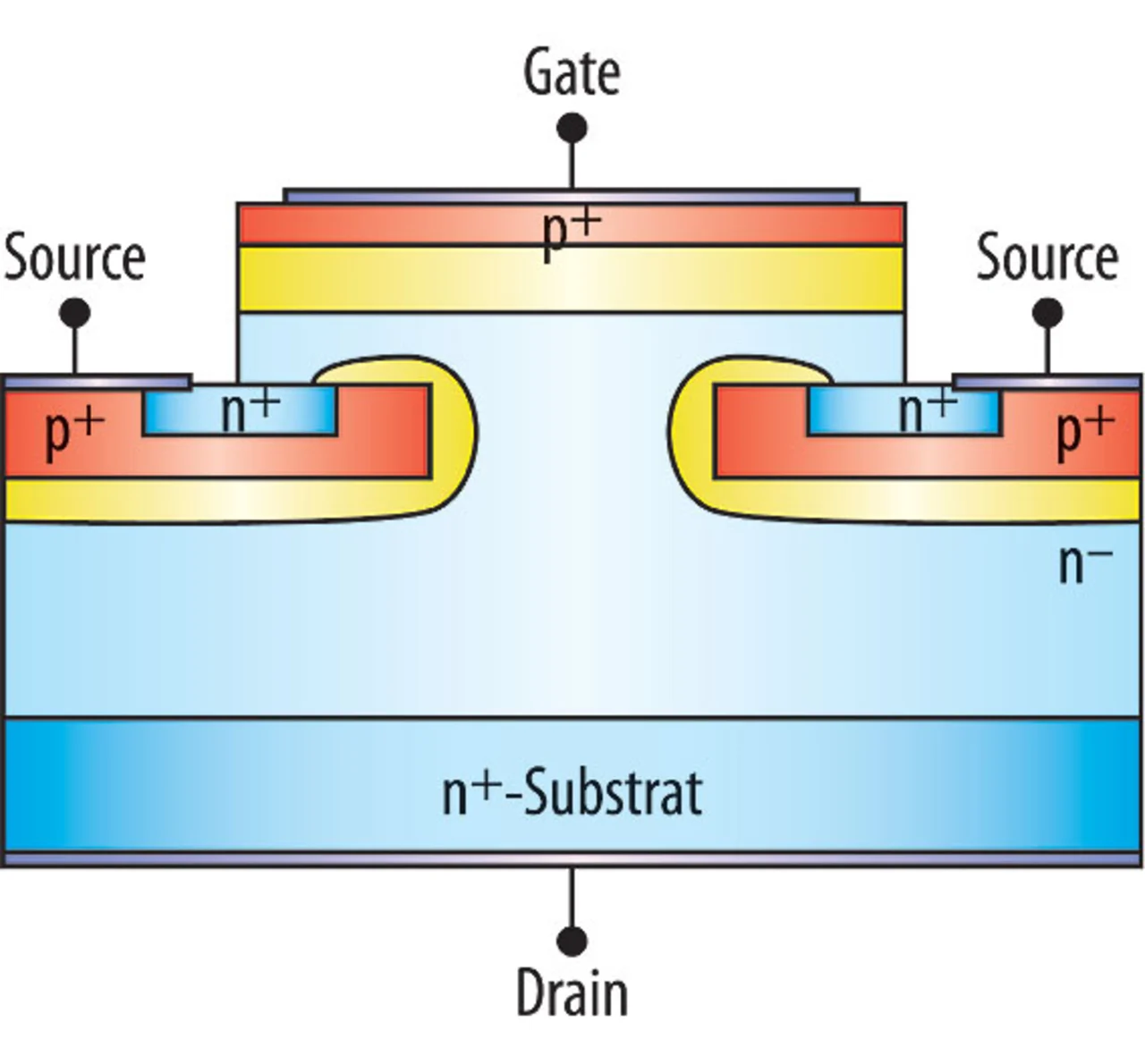

Aufgrund dieser Überlegungen hat Infineon eine JFET-Struktur mit einem horizontalen Kanal (Bild 1) gewählt. Das im Prinzip eindimensionale Kanal-Design ermöglicht eine genaue Kontrolle der Schwellspannung durch Implantation und ergibt einen ausgezeichneten flächenspezifischen Einschaltwiderstand.

Es wurde bewusst eine selbstleitende JFET-Variante gewählt. Damit eröffnet sich ein breites Fenster zum Schalten zwischen Schwellspannung und Durchgreifspannung. Damit konnte eine einfache spannungsbasierte Ansteuerung (z.B. zwischen 0 und –20 V) für ein sicheres Ein- und Ausschalten mit ausreichenden Margen und ohne bipolare Verluste realisiert werden.

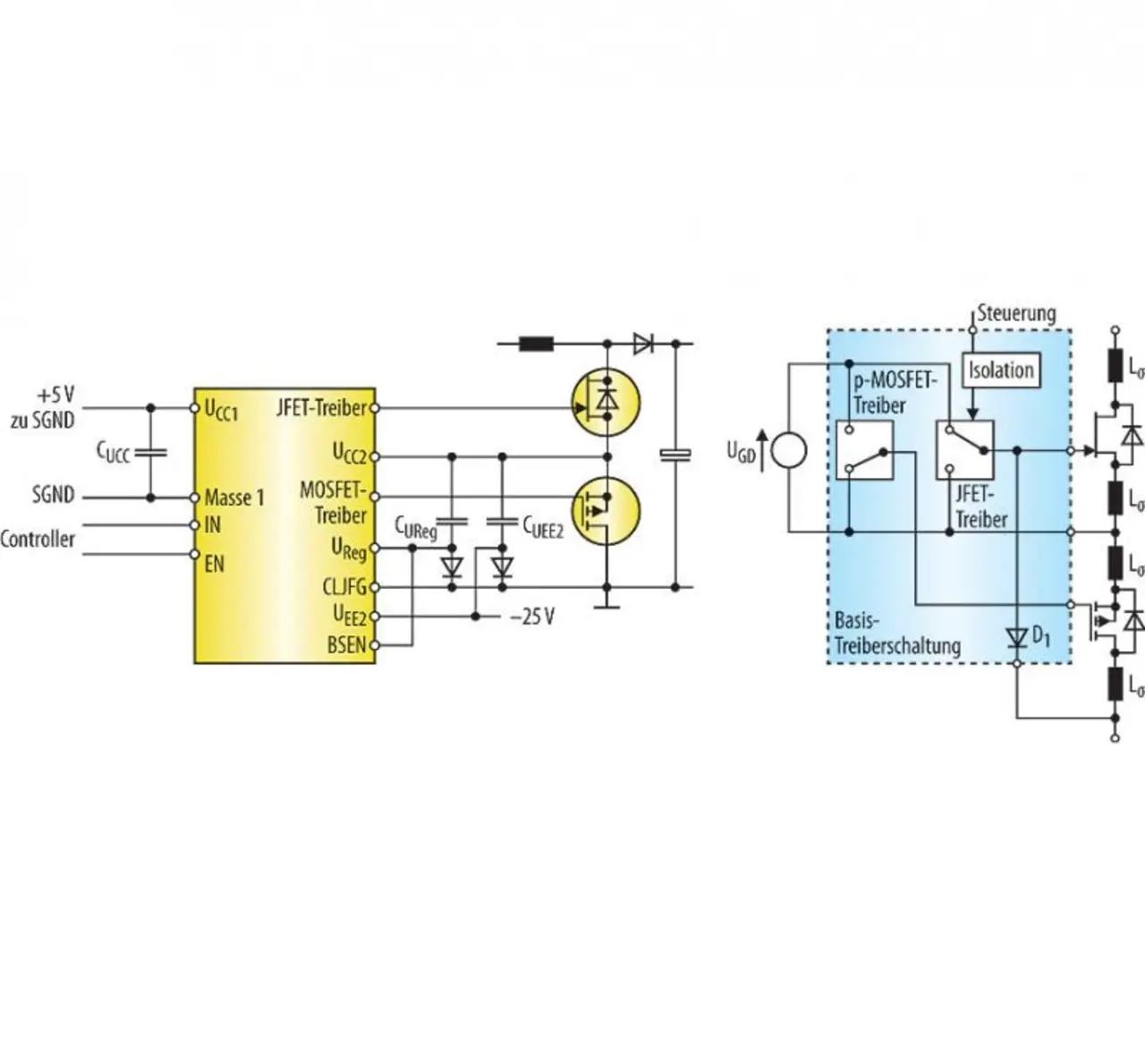

Für Anwendungen, die eine selbstsperrende Charakteristik (normally-off) erfordern, wird eine sogennannte „Direct driven“-Ansteuerung des Bauelements [4] mit einem hierfür entwickelten Ansteuerbaustein empfohlen. Hierbei wird in einer Kaskoden-Topologie ein einfacher selbstsperrender Silizium-MOSFET mit niedriger Sperrspannung – typisch 30 V – in Serie mit dem SiC-JFET geschaltet. Empfohlen wird ein p-Kanal-Transistor, da hier der Gate-Treiber sowohl für den JFET als auch den p-MOSFET auf das gleiche Potenzial referenziert werden kann (Bild 2).

Die Streuinduktivität des p-Kanal-Bauelements liegt damit nicht im Ansteuerkreis. Während des normalen Betriebs leitet der Niederspannungs-MOSFET, ohne dabei nennenswerte Auswirkungen auf den gesamten Durchlasswiderstand zu haben. Beim Anlauf der Schaltung oder im Falle einer Fehlfunktion wird der Niedervolt-MOSFET ausgeschaltet, wobei das JFET-Gate über eine Diode fest mit dem Source-Potenzial des MOSFETs verbunden ist.

Der Vorteil dieses Konzepts ist, dass der JFET dynamisch wie ein Stand-alone-Bauelement arbeitet, im Bedarfsfall aber auf die sicherheitsrelevanten Eigenschaften der klassischen Kaskodenstruktur zurückgegriffen werden kann. Dieses Konzept wurde in einem seriennahen Photovoltaik-Umrichter demonstriert. Es konnte experimentell gezeigt werden, dass dieses Konzept bei einer Reihe möglicher Fehler, wie Ausfall der Versorgungsspannung der Ansteuerung, den Umrichter jeweils in einem sicheren Betriebszustand hält [5].

- Die erste Generation

- Höher Schaltfrequenzen, weniger Verluste