SAR oder ΔΣ?

Welche Datenwandler-Architektur ist die Richtige?

Fortsetzung des Artikels von Teil 1

Unterstützung mehrerer analoger Kanäle

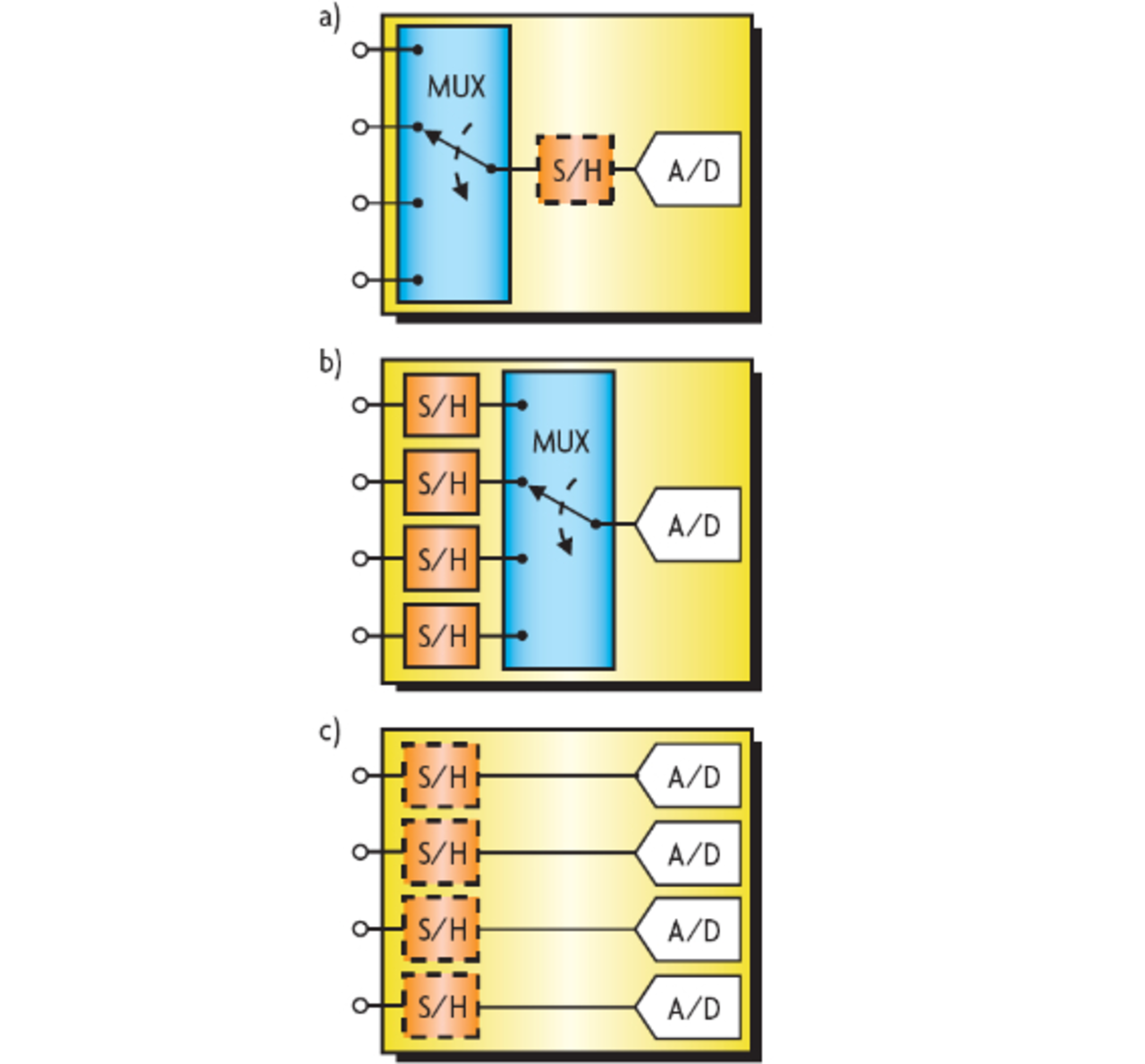

Erfordert die Anwendung das Wandeln mehrerer Signale, kommen auch Wandler mit integriertem Multiplexer zum Einsatz (Bild 2a). Dieser schaltet die verschiedenen analogen Kanäle in gegebener Reihenfolge über eine Sample- and-Hold-Stufe (SAR-Wandler) oder direkt (ΔΣ-Wandler) auf die Eingangsstufe des Wandlers (Beispiel ΔΣ: ADS1258; SAR: ADS7953). Die ursprüngliche fDR des Wandlers muss hier unter den einzelnen Kanälen aufgeteilt werden.

Beim Schalten zu einem anderen Kanal kommt es zu unvermeidbaren Spannungssprüngen. Deswegen muss eine gewisse Zeit eingeräumt werden, damit das neue Signal stabil am Eingang anliegt (dies hat eine weitere Reduktion von fDR zur Folge). Wenn diese Einschwingzeit beim SAR-Wandler vorüber ist, kann eine neue Umsetzung gestartet werden, die sofort ein gültiges Ergebnis liefert. Die Verzögerung, welche die Anzahl von Wandlungszyklen angibt, bis das Eingangssignal am Ausgang des Wandler verfügbar ist, wäre somit Null.

Beim ΔΣ-Wandler ist die Bestimmung der Verzögerung etwas komplexer, da sie von der Art des internen digitalen Filters abhängig ist. Soll die gesamte Signalbandbreite bis ca. fDR/2 gewandelt werden, kommt ein FIR-Filter (Finite Impulse Response) zum Einsatz. Durch die hohe Anforderung des Frequenzverlaufs und die dadurch gegebene Länge des FIR-Filters sind Verzögerungen von 50 und mehr Wandlungszyklen keine Seltenheit.

Jobangebote+ passend zum Thema

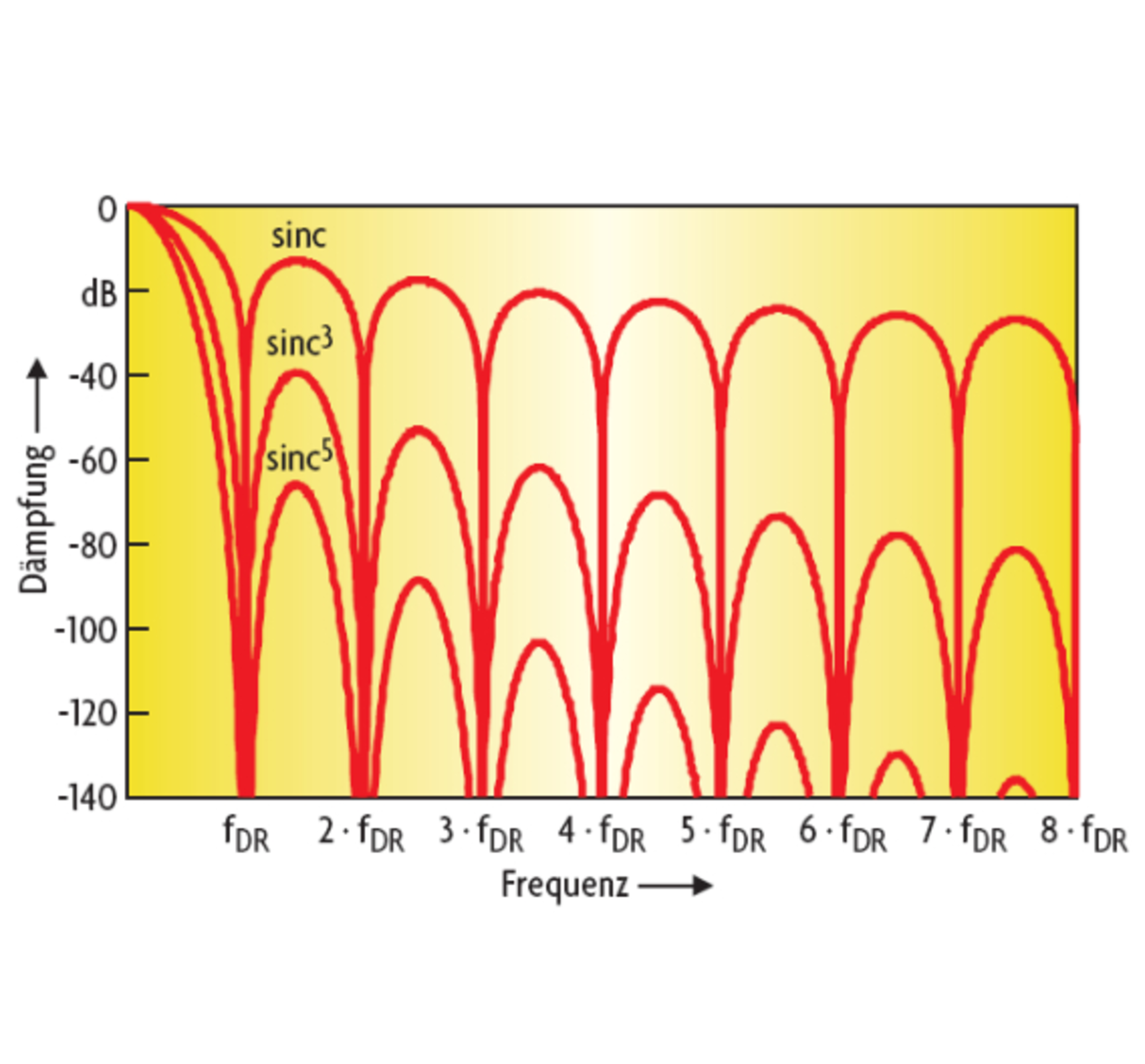

Die Alternative dazu ist das so genannte Sinc-Filter. Dieses sehr einfach zu implementierende Filter ist beliebig kaskadierbar. Die Anzahl der Kaskadierungen gibt hier die Ordnung an. Bild 3 zeigt den Frequenzverlauf für Ordnungen von 1 (sinc), 3 (sinc3) und 5 (sinc5). Die Verzögerung entspricht hier der Ordnung des Sinc-Filters. Der Frequenzverlauf macht deutlich, dass dieser Filtertyp nur bei Gleichspannung (f = 0 Hz) keine Dämpfung hat.

Aus diesem Grund sind Sinc-Filter am besten für sich langsam verändernde Eingangssignale geeignet. Da hier nur der Absolutwert interessiert, ist das Wissen der genauen Datenrate auch nicht zwingend notwendig und der Weg frei für integrierte Taktquellen, wie beim weiter oben vorgestellten ADS1115. Anwendungen finden sich zum Beispiel im der Bereich der Temperaturmessung oder der Überwachung einer Batterie.

Eine Konsequenz ist in diesem Zusammenhang, dass das Rauschen bei „Sinc“-basierten ΔΣ- Wandlern meist absolut und bei denen mit FIR-Filter im Verhältnis zum Signal (SNR) angegeben wird. Aufgrund der geringeren Verzögerung, die bei jedem Kanalwechsel berücksichtigt werden muss, nutzen ΔΣ-Wandler mit integriertem Multiplexer Sinc-Filter – unter Inkaufnahme der limitierten Signalbandbreite. Die Verzögerung von SAR-Wandlern wird allerdings nicht erreicht.

Zurück zum Multiplexer. Ein weiterer Nachteil eines Multiplexers nach Bild 2a kann die fehlende Möglichkeit sein, verschiedene analoge Signale zum gleichen Zeitpunkt abzutasten. Dieses so genannte simultane Wandeln ist bei Motor-Steuerungsoder auch Leistungsmessungs-Anwendungen von Bedeutung. Das lässt sich umgehen, wenn beim SARWandler pro Eingangskanal eine S/HStufe vorgesehen wird und erst danach die Signale multiplext werden (Bild 2b).

Auf Befehl werden die analogen Signalwerte aller Eingangssignale von den S/H-Stufen eingefroren und dann nacheinander umgesetzt. Das simultane Wandeln mehrerer analoger Kanäle mit nur einem Wandler funktioniert aber nur mit SAR-Wandlern – da ΔΣ-Wandler keine S/H-Stufe enthalten.

Die wohl einfachste, wenn auch nicht kostengünstigste Lösung ist die Verwendung von einem Wandler pro analogem Signal. Der Multiplexer wird dadurch überflüssig (Bild 2c). Diese Lösung ist ideal, wenn mehrere breitbandige Signale gewandelt werden sollen.

Texas Instruments bietet Bausteine an, die mehrere Wandler in einem Gehäuse integrieren (ΔΣ: ADS1278, SAR: ADS8556). Hier steht auch jedem analogen Kanal die volle Abtastgeschwindigkeit zur Verfügung. Simultanes Wandeln ist hier natürlich ebenfalls möglich.

In diesem Artikel wurde gezeigt, dass zwischen beiden Architekturen erhebliche Unterschiede bestehen. Während der SAR-Wandler beispielsweise durch die Möglichkeit einer Wandlung zu einem exakten Zeitpunkt Vorteile bietet, zeigt der ΔΣ-Wandler bei der geringen Anforderung des Anti- Aliasing-Filters seine Stärke.

Ein weiterer wichtiger Unterschied besteht im Signal/Rausch-Verhältnis. Durch die Integration bei der ΔΣ-Umsetzung werden kurzzeitige Signalstörungen wegintegriert. Dadurch lassen sich ΔΣ-Wandler mit bis zu 120 dB SNR realisieren, bei SAR-Wandlern ist im Moment bei ca. 100 dB SNR Schluss. Aber gerade diese Differenzen können den Entscheidungsprozess beschleunigen, sodass sich der Entwickler innerhalb kürzester Zeit auf einen Wandlertyp festlegen kann. Ist die Architekturwahl vollzogen, kann das so genannte ADC-Selection-Wheel bei der Wahl eines geeigneten Datenwandlers behilflich sein.

- Welche Datenwandler-Architektur ist die Richtige?

- Unterstützung mehrerer analoger Kanäle