Fortschritt: selten geradlinig

Neue Wandlerarchitekturen und -techniken

Fortsetzung des Artikels von Teil 2

TDC und DTC (Zeit/Digital- und Digital/Zeit-Wandler)

Zeitbereichswandler untersuchen

Die Skalierung von MOS-Bauteilen geht mit einer Skalierung der Versorgungsspannung einher. Schwierige Kompromisse zwischen Signalreserven, Rauschen, Linearität, Bandbreite, Leistungsaufnahme und Geräteanpassung begrenzen die Leistungsfähigkeit von Analogschaltungen einschließlich Wandlern.

In den frühen neunziger Jahren untersuchten Forscher als Reaktion auf das Problem der schrumpfenden Reserven beim Signalhub im Voltage-Mode-Schaltungen im Current Mode. Doch auch wenn eine feste Obergrenze im Strombereich nicht immer sofort ersichtlich ist, sind Ströme und Spannungen durch endliche Knotenimpedanzen aneinander gebunden. Die ursprünglichen Randbedingungen für die Verarbeitung von Signalen im Voltage Mode führten unweigerlich zu ähnlichen Herausforderungen bei Current-Mode-Systemen. Ferner arbeiten viele Signalquellen, Sensoren und Aktuatoren im Voltage-Mode-Betrieb, so dass die Spannungs/Strom- und Strom/Spannungswandler unvermeidbar zu neuen Engpässen werden. Inzwischen hat sich die Geschwindigkeit, mit der die Versorgungsspannungen verringert werden, verlangsamt. Das Problem der Spannungsreserve bleibt dennoch bestehen.

Entwickler von Analogschaltungen haben begonnen, sich mit einer weiteren analogen Variable zu beschäftigen, die man zur Darstellung und Verarbeitung von Informationen verwenden könnte: Zeitintervalle. Bei Schaltungen wie PLLs (Phase Locked Loops) oder DLLs (Delay Locked Loops), die im Zeitbereich arbeiten, handelt es sich um ausgereifte Architekturen. Bahnbrechende Arbeiten bei Time-Domain-Wandlern lassen sich bis zu den Anfängen vor einigen Jahrzehnten zurückverfolgen. Zeit/Digital-Wandler (TDCs) und Digital/Zeit-Wandler (DTCs) sind zu wichtigen Funktionsblöcken für digitale und semidigitale Timing/Taktsysteme geworden.

Zwei der wichtigsten analogen Schaltungsprimitive für die Verarbeitungszeit sind der CMOS-Inverter und das flankengetriggerte D-Flip-Flop (DFF).

Die von TDCs/DTCs verarbeiteten Signale im Spannungs-/Strombereich verlaufen im Allgemeinen annähernd rechteckig oder, insbesondere bei hohen Frequenzen, verzerrt sinusförmig. Allerdings ist nicht die Signalform entscheidend. Entscheidend ist, wann solche Signale vorher festgelegte Schwellwerte überschreiten und damit den Zeitpunkt des Übergangs von 0 auf 1 oder von 1 auf 0 bestimmen. Der Übergang wird als Nulldurchgangszeit bezeichnet.

Schaltungsprimitive TDCs/DTCs

Zwei der wichtigsten analogen Schaltungsprimitive für die Verarbeitungszeit sind der CMOS-Inverter und das flankengetriggerte D-Flip-Flop (DFF).

Die von TDCs/DTCs verarbeiteten Signale im Spannungs-/Strombereich verlaufen im Allgemeinen annähernd rechteckig oder, insbesondere bei hohen Frequenzen, verzerrt sinusförmig. Allerdings ist nicht die Signalform entscheidend. Entscheidend ist, wann solche Signale vorher festgelegte Schwellwerte überschreiten und damit den Zeitpunkt des Übergangs von 0 auf 1 oder von 1 auf 0 bestimmen. Der Übergang wird als Nulldurchgangszeit bezeichnet.

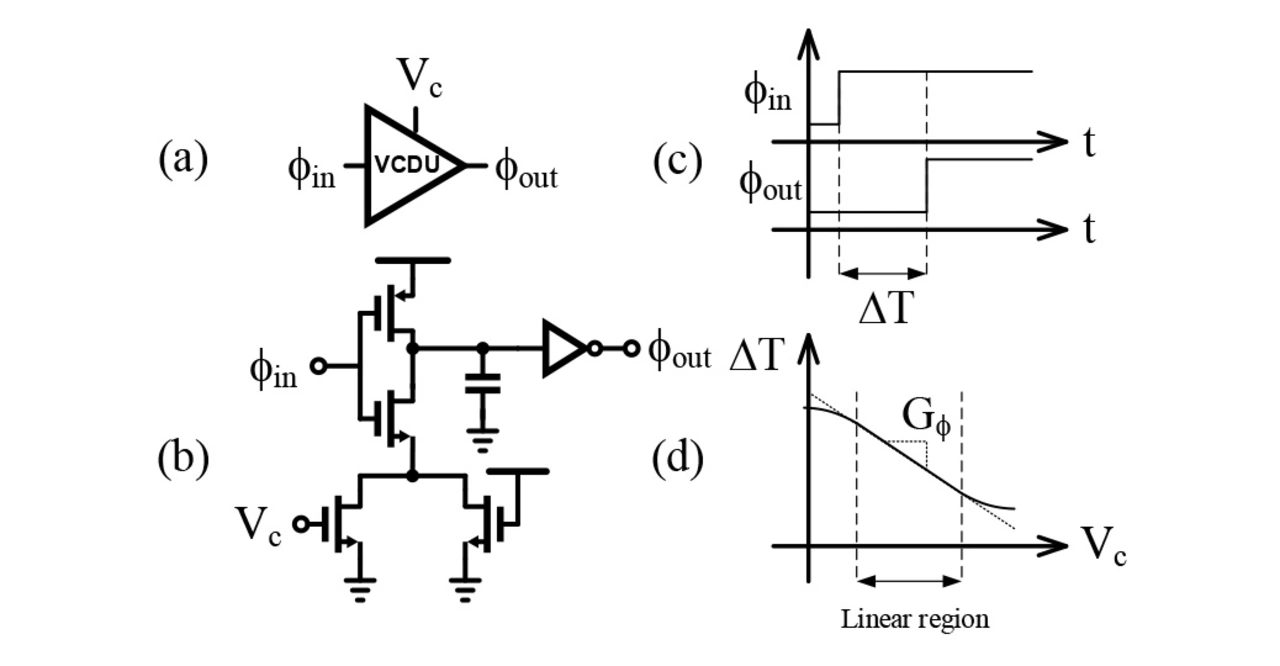

In TDCs/DTCs ist der CMOS-Inverter oft stromlos, damit seine Gate-Verzögerung mit einem Steuerstrom (IC) oder einer Steuerspannung (VC) eingestellt werden kann. Er wird zur Realisierung einer spannungsgesteuerten Verzögerungseinheit (VCDU) verwendet (Bild 2). Am Eingang befindet sich ein Signal Øin, am Ausgang ein Signal Øout. Die Steuervariable in diesem Beispiel ist VC, und sie kann sich auf die Netto-Gate-Verzögerung ΔT auswirken. Die Kleinsignalverstärkung GØ am Ruhepunkt der Spannungs/Zeit-Kennlinie der VCDU bestimmt die Fähigkeit dieses Primitivs, Zeit zu verarbeiten.

Jobangebote+ passend zum Thema

VCDUs wie die in Bild 2 oder andere, insbesondere solche in differentieller Form, sind Funktionsblöcke für Ringoszillator-VCOs und spannungsgesteuerte Verzögerungsleitungen, die dann zur kontinuierlichen Verarbeitung von Zeitsignalen verwendet werden.

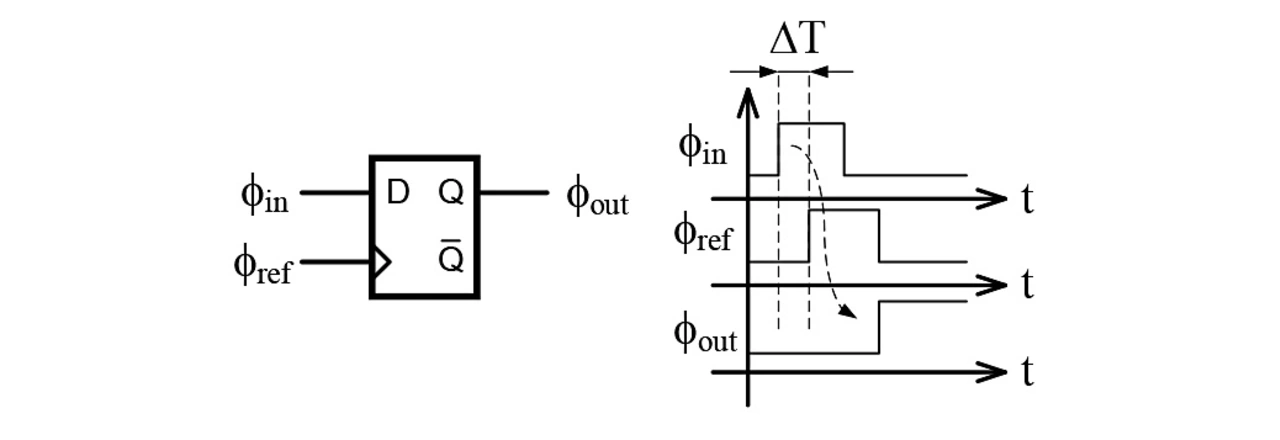

Das andere Zeitbereichs-Primitiv ist das flankengetriggerte D-Flip-Flop (DFF) gemäß Bild 3. Es kann als analoges Primitiv verwendet werden, um eine Komparatorfunktion zu realisieren, da es bei zwei Impulsen, zum Beispiel Øin und Øref, die an seinen D-Eingang beziehungsweise seinen Takteingang angelegt werden (Bild 3), an seinem Q-Ausgang eine logische 1 liefert, wenn Øin vor Øref liegt (Øin < Øref), und andernfalls eine logische 0 (Øin ≥ Øref). Die VCDU und das DFF können dann zum Aufbau von TDCs und DTCs verwendet werden.

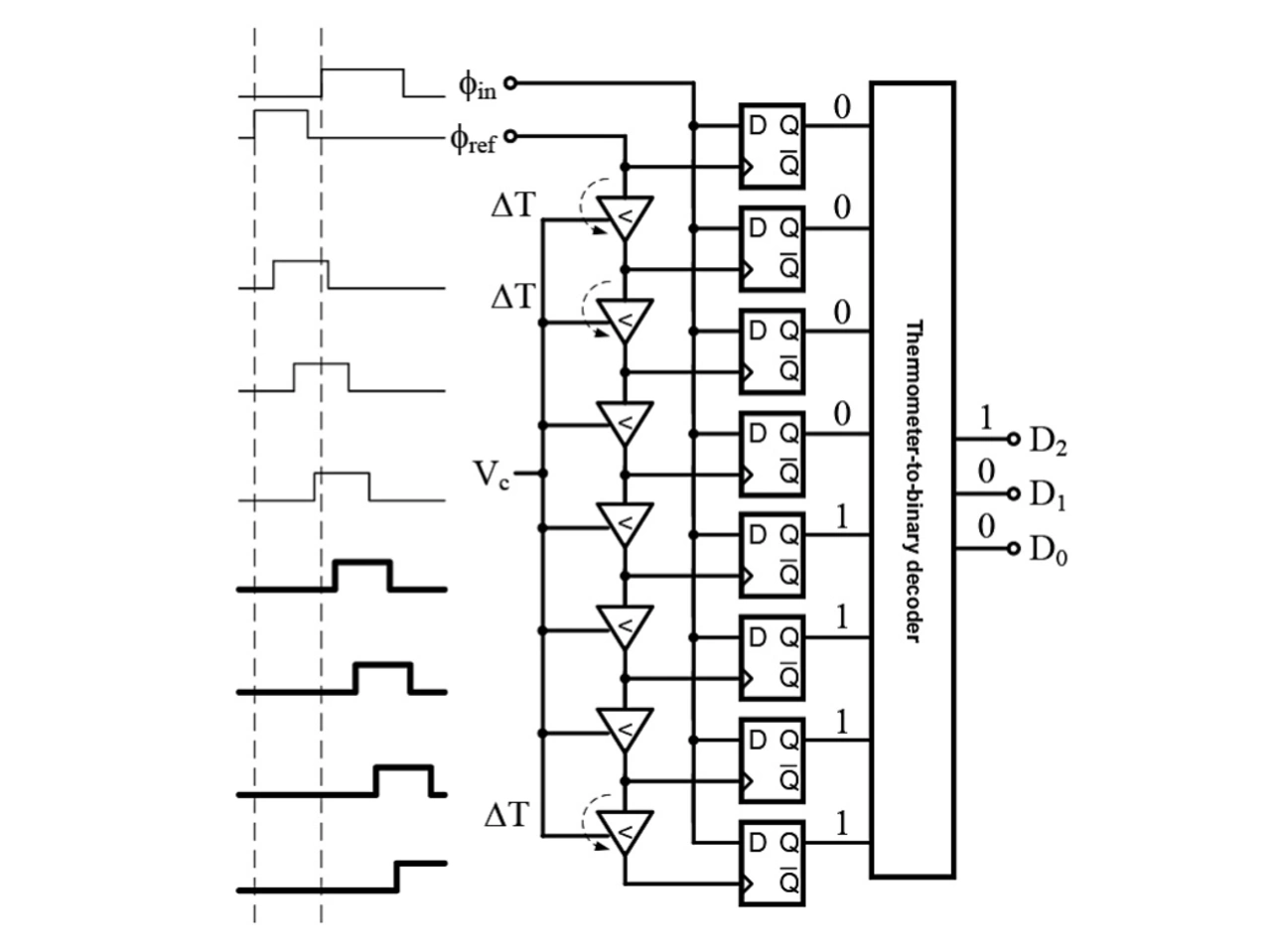

Ein einfaches Beispiel ist der in Bild 4 dargestellte Time-Domain-Flash-A/D-Wandler. Hier wird die Gate-Verzögerung ΔT der VCDU herangezogen, um die Schwellenwerte des Time-Domain-Komparators festzulegen, was somit die Quantengröße und die Nennauflösung des Wandlers bestimmt.

Feinere Quanten können durch Phaseninterpolation zwischen den Ausgängen zweier Verzögerungselemente oder durch Verwendung eines gleitenden »Time Veneers« erzielt werden, welches durch Einführung einer zweiten zeitverschobenen servo- und spannungsgesteuerten Verzögerungsleitung entsteht. Diese Techniken bringen jedoch zusätzliche Komplexität, Flächenbedarf, Leistungsaufnahme, Rauschen und Linearitätsprobleme mit sich, die sorgfältig zu handhaben sind.

Eine andere gängige Möglichkeit zur Entwicklung eines TDCs besteht darin, einen Ringoszillator-VCO mit VCDUs aufzubauen. Das analoge Spannungseingangssignal wird zur Steuerung der VCDUs verwendet, so dass die Oszillatorfrequenz des VCOs vom zu digitalisierenden Eingangssignal abhängt.

Ein Zähler oder ein Array von DFFs, die mit den Ausgangsphasen des Ringoszillators verbunden sind, wird dann verwendet, um die Oszillatorfrequenz auf eine digitale Darstellung des analogen Eingangs abzubilden. Modernere »VCOADC«-Architekturen nutzen solche VCOs als Quantisierer, die in Zeitbereichs- oder klassische Spannungsbereichs-Delta/Sigma-Modulatoren eingebettet sind.

Funktionieren TDCs also?

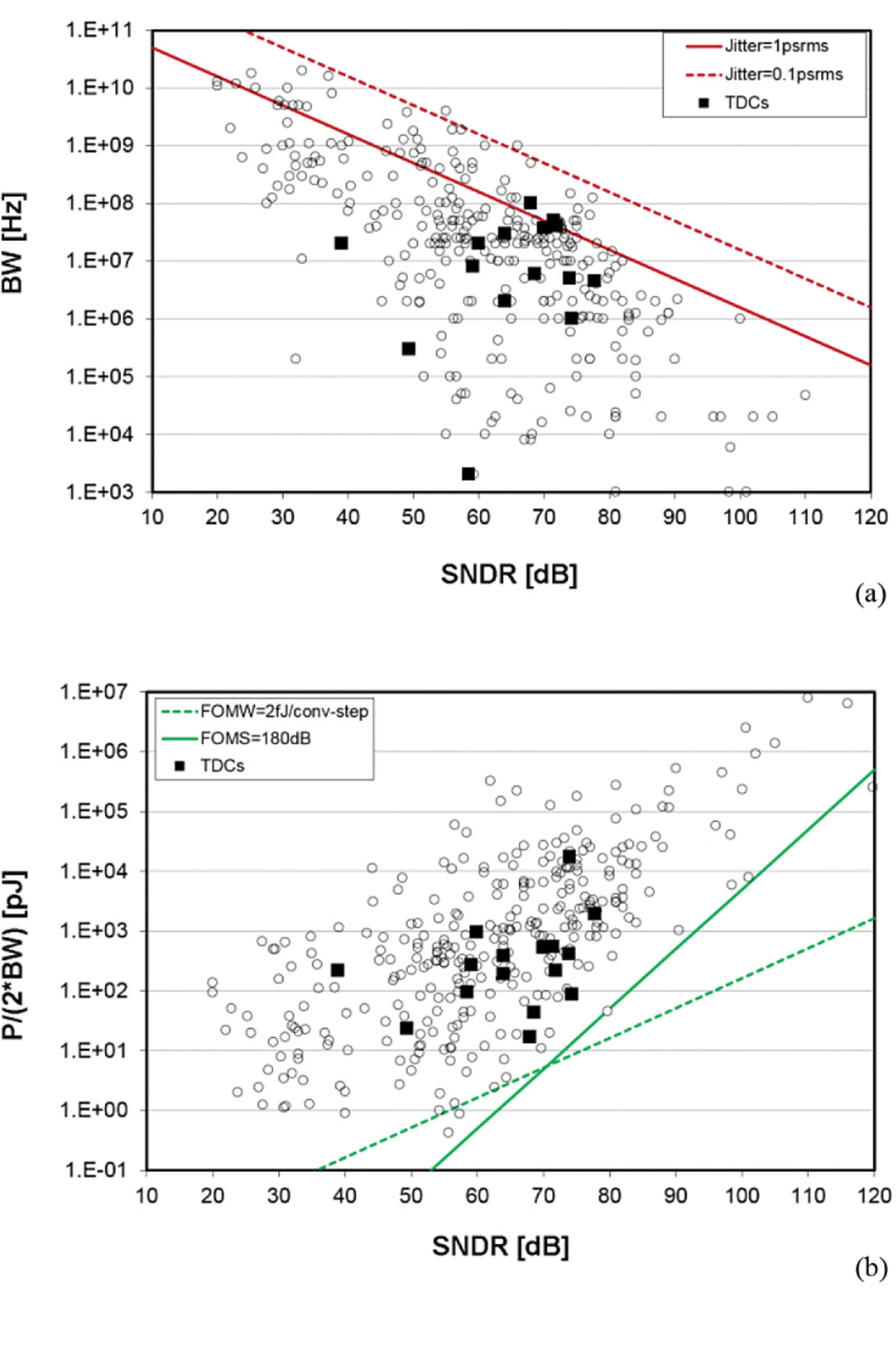

Wie gut sind TDCs im Vergleich zu herkömmlichen ADCs? Die Kurven für den Apertur-Jitter und die Energie für alle A/D-Wandler, traditionell und Time Domain, zeigt Bild 5 für alle auf der ISSCC und dem VLSI-Symposium in den letzten zwanzig Jahren veröffentlichten Beiträge. In beiden Kurven sind die TDCs als schwarze Quadrate eingezeichnet. Auch eingezeichnet sind hybride TDCs. Damit gemeint sind A/D-Wandler-Architekturen, die herkömmliche spannungsgesteuerte Schaltkreise und Time-Domain-Sub-Blöcke enthalten.

Außerdem liegen die neuesten Datenpunkte näher an den Geraden für den Stand der Technik (niedrige Jitter-Werte, oben in der Aperturkurve, beste Leistungswerte, unten in der Energiekurve).

Insgesamt gesehen, liegt die Leistungsfähigkeit der bisher veröffentlichten Architekturen im mittleren SNDR-Bereich und im mittleren Bandbreitenbereich. Die Energieeffizienz ist nicht die wettbewerbsfähigste, obwohl die neuesten Datenpunkte auf eine erhebliche Verbesserung der Wandlungseffizienz hinzuweisen scheinen.

Wie erwähnt, sollte man vorsichtig sein und alleine aus den Diagrammen keine schnellen Schlüsse ziehen. Insbesondere wenn es darum geht, welche Leistungsfähigkeit mit TDCs erreichbar ist. Eine genauere Prüfung der Beiträge, die diesen Datenpunkten zugrunde liegen, ergibt, dass diese, insbesondere bei Veröffentlichungen aus der Industrie, eher auf Signalbandbreiten im zweistelligen MHz-Bereich mit einem SNDR Mitte der 70er Jahre abzielen und derzeit als Embedded A/D-Wandler in SoCs für Mobiltelefone Anwendung finden.

Das einzige Unterscheidungsmerkmal, welches TDCs als vorteilhaft erscheinen lässt, sind deren kompakte Abmessungen. TDCs sind daher sehr wettbewerbsfähig gegenüber Pipeline- und SAR-A/D-Wandler mit gleicher Leistungsfähigkeit und größeren Abmessungen.

Ein weiterer Anwendungsbereich für TDCs sind digitale Temperatursensoren und andere Mess- und Digitalisierungssysteme mit niedriger Frequenz und geringer Leistungsaufnahme, einschließlich solcher für das IoT. Zurückzuführen ist dies auf die Kombination aus kompakter Bauweise, geringer Leistungsaufnahme und niedrigen Kosten.

Wie gut lassen sich TDCs/DTCs skalieren?

Ein Grund für den Einsatz von TDCs und DTCs als alternative Wandlerarchitekturen ist deren Skalierbarkeit mit der CMOS-Prozesstechnologie. Auf dieser Basis und unter Berücksichtigung der Primitive in Bild 2 und Bild 3 sind erste Beobachtungen möglich.

Zunächst skaliert die Fläche dieser Primitive ungefähr mit dem Mooreschen Gesetz. Das ist ein Vorteil gegenüber herkömmlichen A/D- und D/A-Wandlern, da sich beispielsweise Verstärker nicht so einfach skalieren lassen.

Die minimale Gate-Verzögerung ΔTmin einer VCDU ergibt sich aus der Prozesstechnologie. Auf der Basis echter Daten und unter Berücksichtigung des nicht glatten Übergangs vom planaren MOS- zum FinFET-Bauteil bei etwa 22 nm lässt sich schätzen, dass sich ΔTmin von einem CMOS-Knoten zum nächsten mit einer ungefähren geometrischen Progression von Faktor 1,15 bis 1,2 verkürzt. Da jedoch eine Verkürzung von ΔTmin direkt mit der Quantisierungsfähigkeit des TDCs zusammenhängt, ist dies eine relativ kleine Verbesserung.

Die Gate-Schaltenergie hingegen zeigt ein ehrgeizigeres Skalierungsprofil. Ausgehend von aktuellen Trends lässt sich von einer CMOS-Generation zur nächsten eine relative Energieverringerung um das etwa 1,52- bis 1,55-fache abschätzen. Dies wirkt sich erheblich auf die Wandlungseffizienz aus und ist tendenziell höher als bei den meisten herkömmlichen A/D-Wandler-Architekturen für denselben Prozessknotenübergang. Somit profitiert die Wandlungseffizienz von TDCs/DTCs stark von der Skalierung.

Während sich eine Verkürzung des ΔTmin zum Nutzen einer höheren Auflösung der TDCs/DTCs verwenden lässt, würde das Phasenrauschen beim Nulldurchgang den realisierbaren Dynamikbereich weiterhin einschränken. Bis vor einigen Jahren bestand die Befürchtung, dass sich die Transkonduktanz (gm) von MOS-Transistoren schneller verbessert als der Spannungsabfall und dadurch das thermische Rauschen verringert wird. Andererseits steigt jedoch die Frequenz des Flickerrauschens (1/f) erheblich.

Bei Strukturbreiten von über 90 nm kann das 1/f-Rauschen sogar wesentlich zum Phasenrauschen beitragen. Dies erfordert beispielsweise verschiedene Formen der Abschwächung in unterschiedlichen Architekturen mit CMOS-Verzögerungsleitungen und Oszillatoren. Die Abschwächung richtet sich nach den resultierenden Rauschmodulationsmechanismen, die zum Phasenrauschen/Jitter beitragen.

Mit der Einführung von FinFETs haben sich jedoch sowohl das Flicker- als auch das thermische Rauschen der FETs gegenüber planaren High-K-Gate-MOSFETs erheblich verbessert (beispielsweise um etwa 3 dB bei 16-nm-FinFETs gegenüber planaren MOS-Bauteilen mit 28 nm). Dies ist sehr ermutigend.

Es ist zu erwarten, dass bei allen TDC-Architekturen eine größere Verbesserung des Jitters gegenüber dem zuvor erwähnten verringerten ΔT erfolgen wird. Sollte dies tatsächlich der Fall sein, deutet dies auf ein neues Potenzial für die Entwicklung von TDCs mit höherem Dynamikbereich hin.

- Neue Wandlerarchitekturen und -techniken

- Technologischer Durchbruch bei Wandlern als Enabler

- TDC und DTC (Zeit/Digital- und Digital/Zeit-Wandler)

- »Compressive Sampling«-A/D-Wandler