Europäische Prozessortechnik

Fertigung von RISC-V-Testchip startet

Europa möchte sich langfristig bei der HPC-Chipfertigung unabhängig machen. Hierzu wurde die European Processor Initiative ins Leben gerufen. Nun vermeldet sie einen ersten Erfolg.

Die EPI – European Processor Initiative – ist ein Projekt mit 28 Partnern aus 10 europäischen Ländern. Mit dem Projekt will sich die EU bei HPC-Chips und -Infrastruktur unabhängiger von Exporten machen. Aus dem Grund forschen die Mitglieder an Testchips für die Serienreife. Nun wurde ein erster Erfolg vermeldet: Der Testchip »EPAC1.0« ist für die Fertigung freigegeben.

Im Projekt wollen die Partner vollständig in Europa entwickelte Prozessor-IPs auf RISC-V-Basis namens EPAC – European Processor Accelerators – bereitstellen. Mit Verwenden der RISC-V-Architektur ist es möglich, Open-Source-Ressourcen auf Hardware-Architektur- und Software-Ebene zu nutzen. Das soll die Unabhängigkeit von nicht-europäischen Technologien ermöglichen.

Jobangebote+ passend zum Thema

Vier VPUs und ein RISC-V-Kern

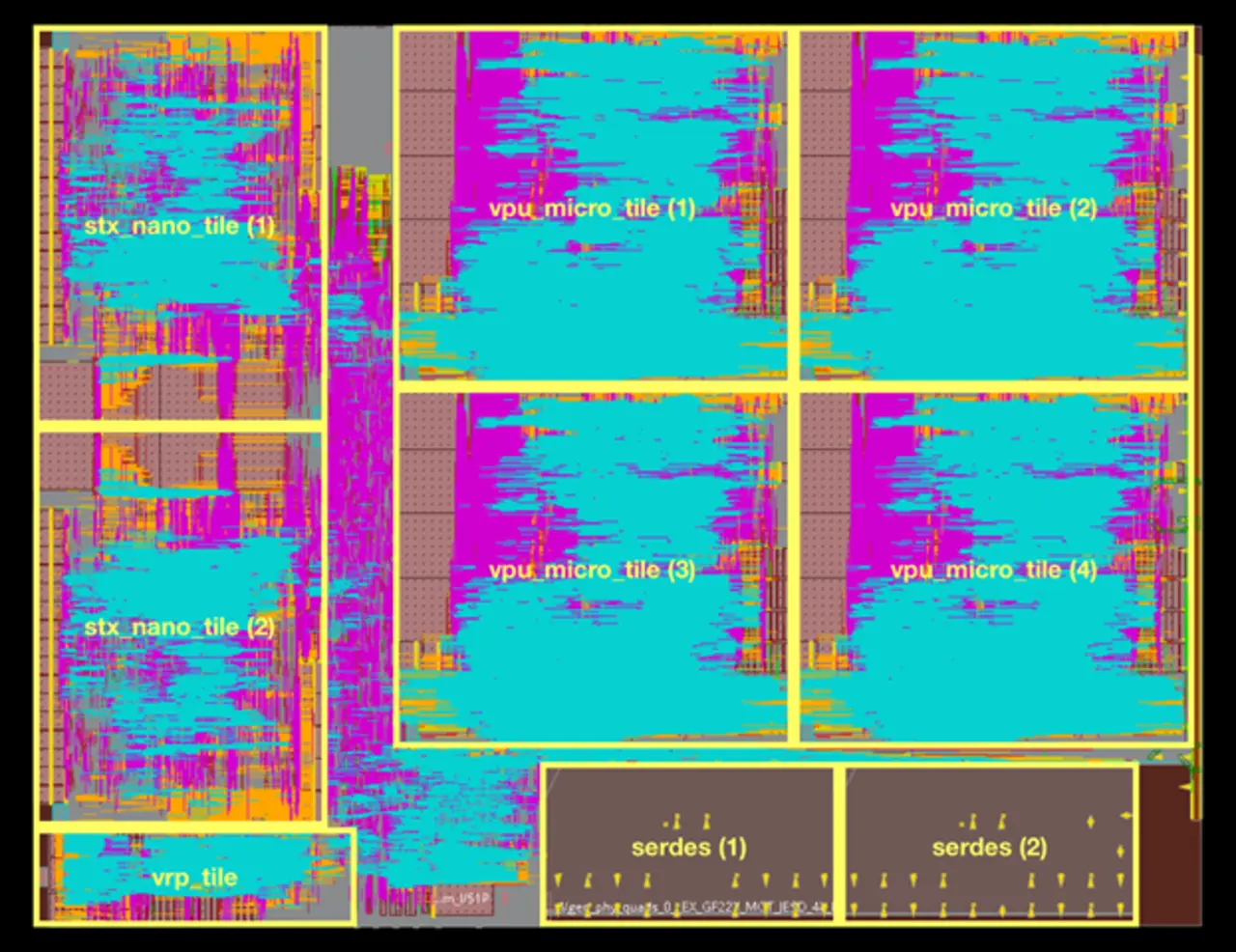

EPAC kombiniert mehrere Beschleuniger, die für verschiedene Anwendungsbereiche spezialisiert sind. Der Testchip, der in Bild 1 dargestellt ist, enthält vier Vector Processing Micro-tiles (VPUs), die aus einem Avispado RISC-V-Kern von SemiDynamics und einer Vektorverarbeitungseinheit des Barcelona Supercomputing Center und der Universität Zagreb bestehen. Jede Kachel enthält außerdem einen Home Node und einen L2-Cache, die von Chalmers beziehungsweise Forth entwickelt wurden und eine kohärente Sicht auf das Speichersubsystem bieten. Der Stencil- und Tensor-Beschleuniger (STX) wurde von Fraunhofer IIS, ITWM und der ETH Zürich entwickelt, der Variable Precision Processor (VRP) von CEA LIST. Sie sind mit einem Network on Chip und der SERDES-Technik von Extoll verbunden.

Gefertigt wurde das EPAC-Design vom Fraunhofer IIS für die Chipintegration in Globalfoundries 22FDX Low-Power-Technik. Es wird in das von Forth und der Universität Zagreb entworfene FPGA-basierte Board integriert.

Als nächsten Schritt möchten die Projektpartner die nächste Generation an EPAC-Beschleuniger und -Schnittstellen weiter verbessern, um eine noch höhere Leistung sowie eine geringere Leistungsaufnahme in 12-nm-Technik und darunter zu erreichen. Gelingen soll das mit einem Chiplet-Ansatz.