Workflow hilft Entwicklern

Neuronale Netze auf FPGAs umsetzen

Fortsetzung des Artikels von Teil 1

Workflow für das Deep Learning auf FPGAs

Der hier vorgestellte Workflow implementiert eine Ende-zu-Ende-Anwendung mit den in Bild 3 dargestellten wesentlichen Bausteinen. So ist der Deep-Learning-Prozessor mit einer typischen und konfigurierbaren Deep-Learning-Arithmetik und Logik für die Datenbewegung ausgestattet.

Hierzu zählt ein Scheduler, der es dem Anwender ermöglicht, verschiedene Deep-Learning-Netzwerke für die gleiche Prozessor-Hardware zu kompilieren, ohne das FPGA neu programmieren zu müssen. Aufgrund vorhandenen synthetisierbaren RTL-Codes ist der Prozessor Target-unabhängig und in eine individuelle Hardware-Plattform integrierbar.

Jobangebote+ passend zum Thema

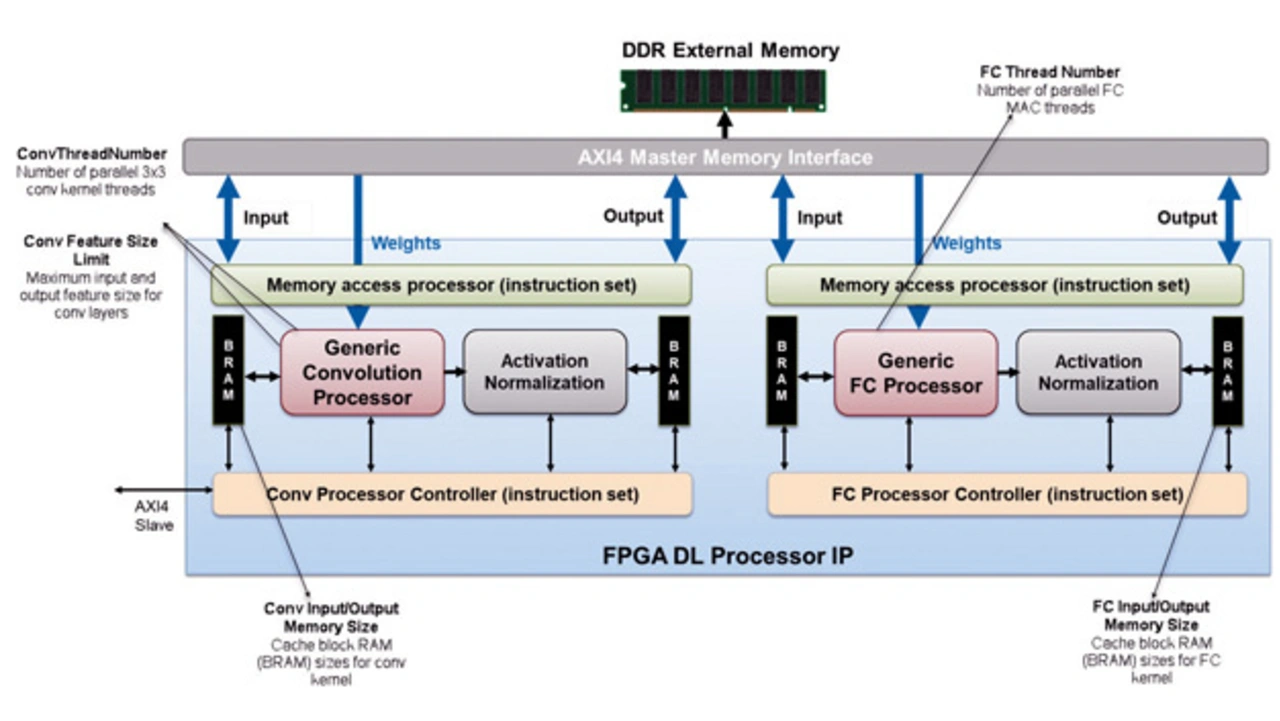

Bild 3 zeigt die vorgeschlagene Architektur des Deep-Learning-Prozessors. Die zu seiner Erzeugung nötigen Schritte sind im Folgenden beschrieben. Eingabebilder, Gewichte und Ausgabebilder werden im externen DDR-Speicher gespeichert und über AXI-Master-Schnittstellen mit dem Prozessor ausgetauscht. Weiterhin führt der generische Convolution-Prozessor die einer einzelnen Faltungsschicht entsprechende Faltungsoperation aus. Anschließend liefert er die Aktivierungen für das Normalisierungsmodul. Es dient zum Hinzufügen der ReLU-Nichtlinearität oder einer Maxpooling-Schicht oder er führt eine »Local Response Normalization« aus. Der generische Fully-Connected- (FC)-Prozessor führt die einer einzelnen vollständig verbundenen Schicht entsprechende Operation aus.

Der Deep-Learning-Prozessor ist konfigurierbar und erlaubt hiermit Trade-offs zwischen Latenzzeit und Chipfläche. Ein erster Entwurfsparameter ist die Anzahl der parallelen Faltungsmatrix-Threads im generischen Faltungsprozessor. Zweitens ist die Größe des BRAM-Caches für die Ein- und Ausgänge der Faltungsmatrix anpassbar. Ebenso lässt sich die Anzahl der parallelen MAC-Threads im FC-Prozessor abstimmen sowie die entsprechende BRAM-Größe für die Ein- und Ausgänge einstellen. Schließlich ist ebenfalls die maximale Feature-Größe für die Ein- und Ausgänge im generischen Faltungsprozessor konfigurierbar.

Unterstützte Anwendungsfälle

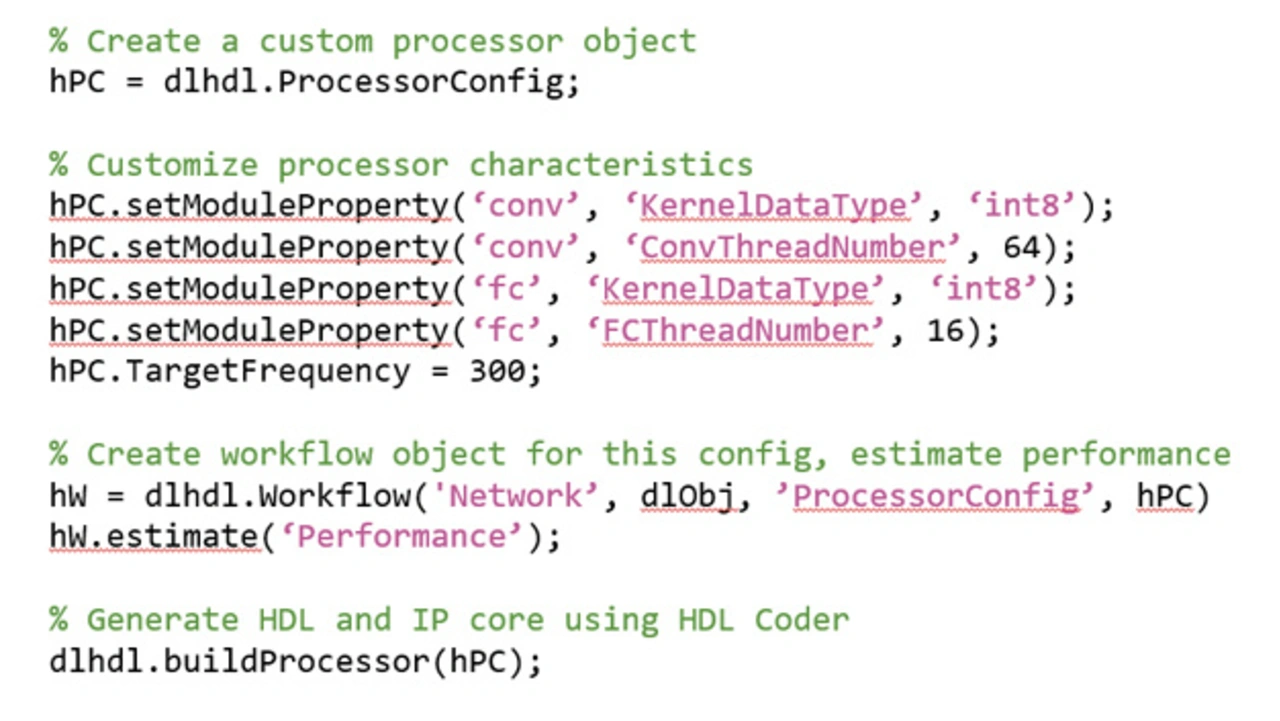

Für die unterstützten Hardware Boards kann man mit wenigen Zeilen Matlab-Programmcode sowohl das Rapid Prototyping als auch das Bereitstellen tiefer neuronaler Netze vornehmen. Nach dem Bereitstellen kann Matlab per Ethernet oder JTAG ein Batch von Eingabedaten an das Target Board senden und dann die Vorhersageergebnisse zusammen mit Profiling-Informationen empfangen. Die Profiling-Daten enthalten Leistungsmetriken wie die Bildrate, die Gesamtlatenzzeit und die Latenzzeit pro Schicht. Basierend auf den Profiling-Daten können Anwender die Leistung mit Überarbeiten des tiefen neuronalen Netzes oder Anpassen der Architektur des Deep-Learning-Prozessors optimieren.

HDL Coder kann den vorgestellten synthetisierbaren IP-Core generieren. Für unterstützte Hardware Boards erfolgt das Bereitstellen ebenfalls automatisiert. Zusätzlich können Entwickler die Leistungsmerkmale und die Fläche für ein gegebenes tiefes neuronales Netz vor dessen Bereitstellen schätzen. Zudem erhöht die Festkomma-Quantisierung signifikant die Leistung in Bezug auf DDR-Speicherverbrauch, Latenzzeit und Fläche.

Teil der vorgeschlagenen Toolchain ist die Deep Network Quantizer App zum automatischen Quantisieren von Gewichten, Bias und Aktivierungen in 8-bit-skalierte Integer-Datentypen mithilfe eines Kalibrierungs-Datensatzes. Zusätzlich lässt sich der Dynamikumfang visualisieren sowie die Leistung nach dem Quantisieren mithilfe eines Validierungs-Datensatzes bewerten. Zum Rapid Prototyping von Deep-Learning-Netzwerken auf FPGAs ist der Deep-Learning-Prozessor mithilfe des »Matlab as AXI Master IP« aus Matlab heraus steuerbar. Anschließend antwortet das IP über eine JTAG- oder PCI-Express-Schnittstelle auf die Lese- oder Schreibbefehle von Matlab.

Systemintegration des IP-Cores

Folgender Abschnitt illustriert die Systemintegration an einem Anwendungsbeispiel, das auf dem Xilinx »ZCU102 Evaluation Kit« implementiert wurde. Bild 4 zeigt das Architekturdiagramm des Systems auf der obersten Ebene.

Das Referenzdesign empfängt einen Kamera-Livestream und nutzt ein bereitgestelltes Netzwerk zur Klassifikation von Objekten in den Videobildern. Anschließend extrahiert der Block »User IP Core« die Region of Interest und führt am Eingabebild ein Down-Sampling mit folgender Nullzentrierung aus – der Vorverarbeitungs-Algorithmus wurde in Simulink entworfen. Hieraus wurde mit HDL Coder ein IP-Core generiert und anschließend in das Referenzdesign integriert.

Im Anschluss wird das vorverarbeitete Bild in den externen DDR-Speicher übertragen. Nach Abschluss des Vorgangs triggert sich der IP-Core des Deep-Learning-Prozessors und benachrichtigt den Algorithmus auf dem ARM-Prozessor. Der IP-Core des Deep-Learning-Prozessors greift auf die vorverarbeiteten Eingaben zu, klassifiziert die Objekte und lädt die Ergebnisse anschließend wieder zurück in den externen DDR-Speicher. Hierauf bearbeitet der ARM-Prozessor die Bilddaten nach und zeigt die Ergebnisse der Objektklassifizierung im ausgegebenen Videobild an.

Mit Matlab sind schließlich noch die Klassifikations-Ergebnisse abzurufen und zu validieren.

- Neuronale Netze auf FPGAs umsetzen

- Workflow für das Deep Learning auf FPGAs