Simulation eines Onboard-Chargers

Streuparameter analysieren

Fortsetzung des Artikels von Teil 2

Abschätzung der Streuinduktivität

Selbstverständlich ist die Modellierung mit S-Parametern genauer, da die Abschätzung der Induktivität der Stromschleife die Kopplungs- und kapazitiven Effekte nicht umfasst. Aber als erste Näherung reicht dies aus, um die Ursache zu quantifizieren.

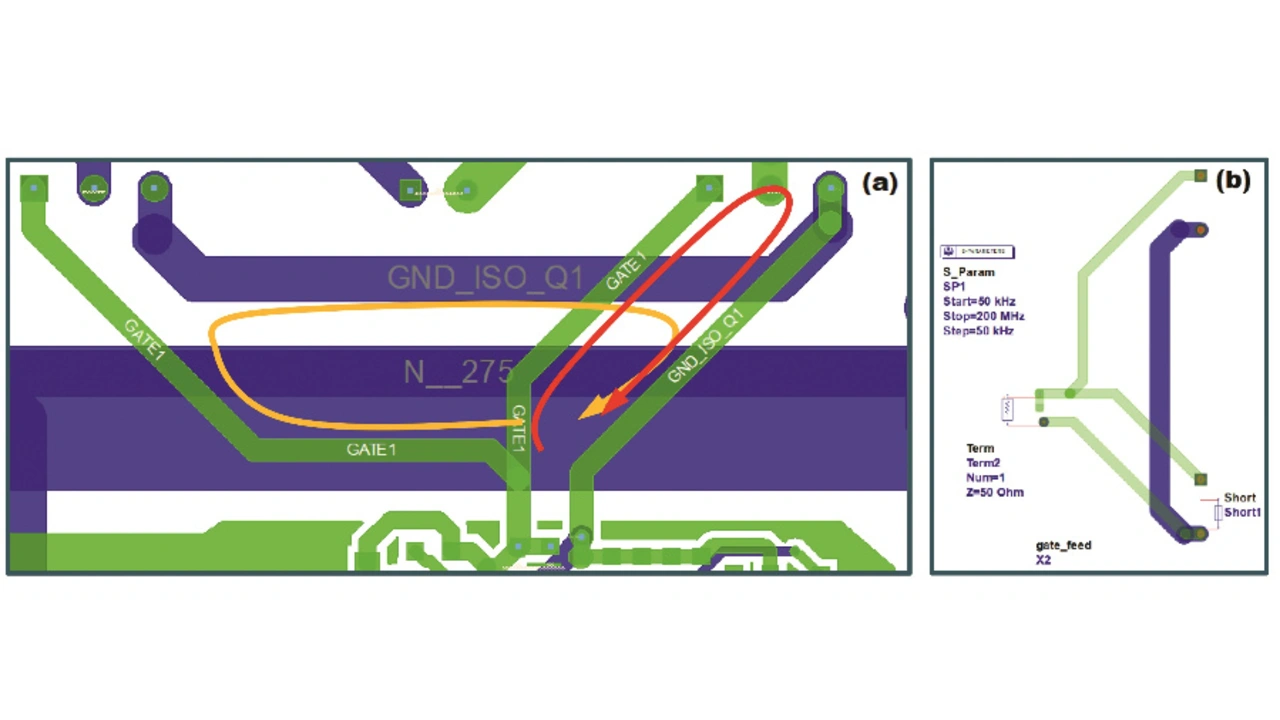

Die Leistungstransistoren sind mit den Treibern durch Leiterbahnen auf der Ober- und Unterseite der Platine verbunden (Bild 10a). Die parasitäre Induktivität bestimmt sich durch den magnetischen Fluss der eingeschlossenen Fläche zwischen Verbraucher (Schalter) und Treiber. Bild 10a zeigt diese Schleifen beziehungsweise Flächen für Q1 und Q2. Die Streuinduktivität lässt sich über das extrahierte EM-Modell der Platine mithilfe einer Ein-Port-Simulation der S-Parameter abschätzen, wobei wechselseitig der Ausgang kurzgeschlossen wird (Kurzschluss als Näherung am Gate-Terminal; Bild 10b). Aus dem Reflektionskoeffizienten S1,1 lässt sich die Induktivität L berechnen:

Jobangebote+ passend zum Thema

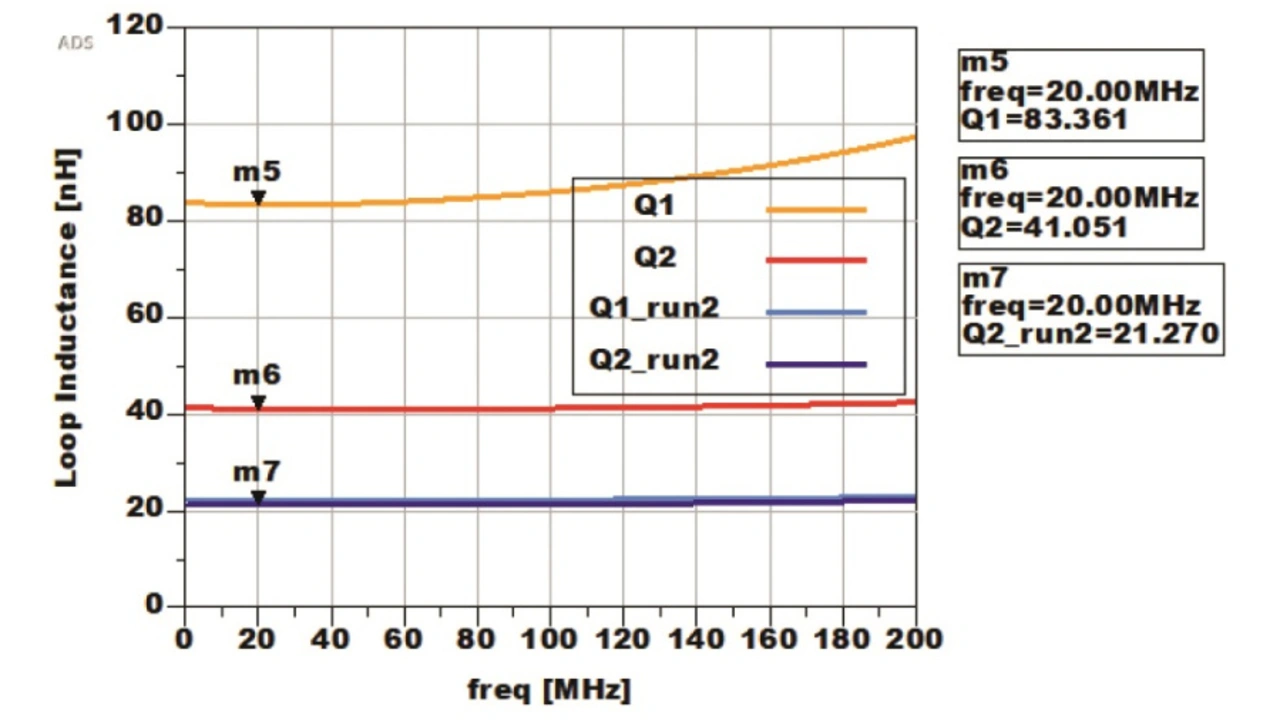

ZL ist die Impedanz von Port 1 und f ist die Simulationsfrequenz. In Bild 11 ist die Schleifeninduktivität der zwei Fälle gezeigt. Die Ergebnisse der anderen Phasen sind ähnlich bis gleich. Der signifikante Unterschied der zwei Schleifen der Variante A (gelbe und rote Linie) kommt durch die Asymmetrie des Layouts zustande, dessen Zuleitungen bei Q1 umso länger sind. Dadurch verdoppelt sich die Induktivität beinahe.

Da wir hier die (kapazitiven) Kopplungen vernachlässigen, hängen die Induktivitäten quasi gar nicht von der Frequenz ab. Trotzdem indiziert das Verfahren die Ursache der Oszillationen, denn die Eingangskapazität der Schalter liegt bei 1,5 nF: Zusammen mit den 83 nH für den kompletten Bias-Schaltkreis ergibt sich eine analytisch berechnete Resonanzfrequenz von 14,2 MHz – also sehr nahe an den 13,5 MHz aus der EM-Cosimulation.

In der zweiten Variante B sind die Schleifeninduktivitäten abgeglichen und daher deutlich symmetrischer und niedriger (blaue und hellblaue Kurven in Bild 11).

Ergebnisse der zweiten Platine

Auf Basis der Simulationsergebnisse wurde das Platinenlayout überarbeitet. Die Hauptziele waren:

- Die Treiberschaltung der zwei SiC-Schalter innerhalb derselben Phase ist vollständig zu entkoppeln. Jeder Schalter erhält einen dedizierten Treiber.

- Die zwei Treiber innerhalb derselben Phase sollen im Layout eine nahezu perfekt symmetrisch sein.

- Das Layout muss eine möglichst minimale Gate-Induktivität der Zuleitungen gewährleisten.

- Die Anzahl der Lagen steigt auf vier, um eine bessere Isolation zwischen den kritischen Leiterbahnen und eine bessere Abschirmung zu gewährleisten sowie eine stabile Masse-Referenz für die Kontrollsignale zu bieten.

Die Bauelemente der zweiten Layoutversion (Rev. B) sind dieselben wie im ersten Layout, der Prototyp der zweiten Version ist in Bild 12 zu sehen.

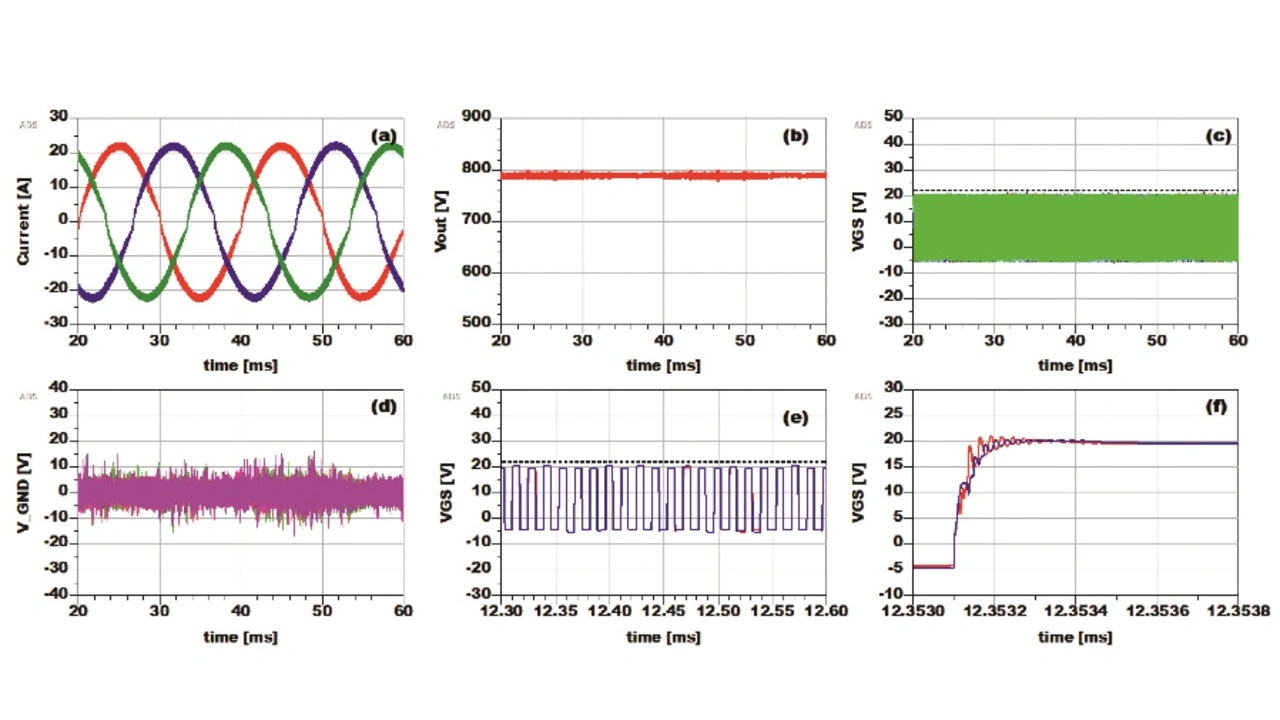

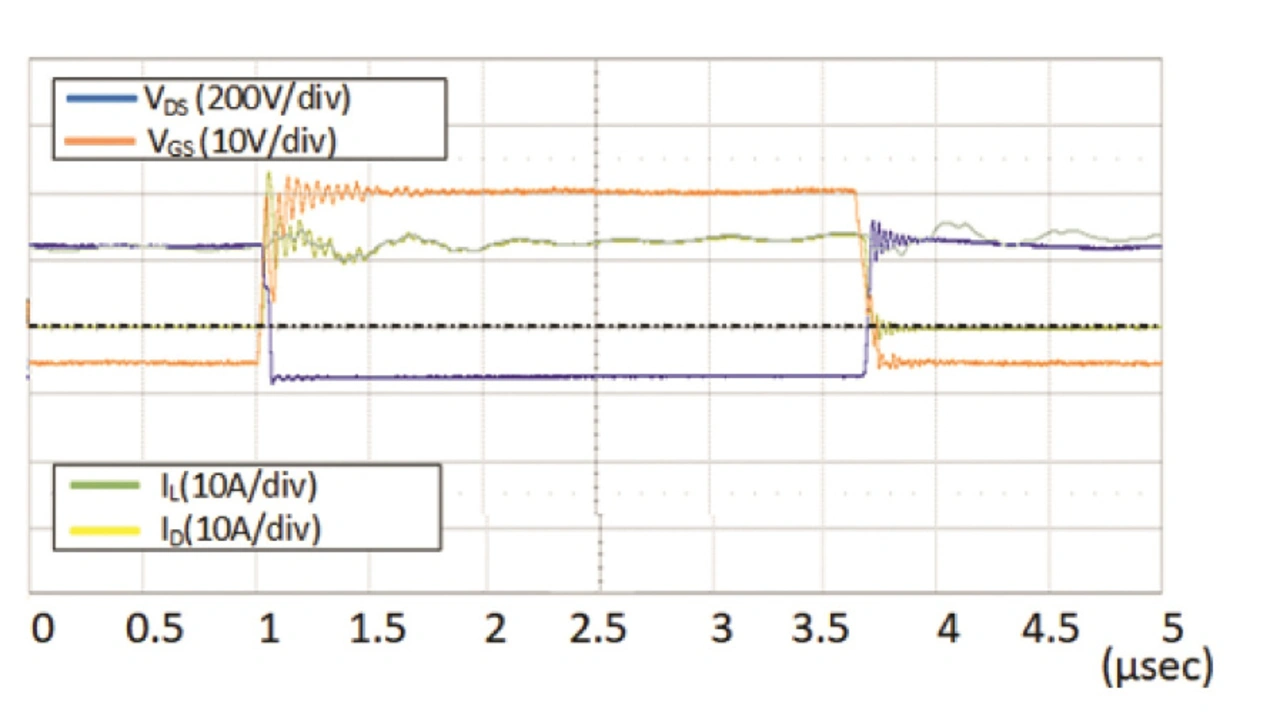

Bild 13 zeigt die entsprechenden Simulationsergebnisse: Die Verbesserungen der Signalqualität sind signifikant (vgl. Bilder 6 und 7). Das Schaltrauschen der Treibersignale ist deutlich niedriger, während die Spannung kürzer überschwingt. Der Wert der Gate-Source-Spannung UGS bleibt sicher unter dem maximal zulässigen Wert. Das Nachschwingen beim Schalten und das Schwingen der Masse (Ground Bounce) sind deutlich reduziert, was auch Messungen (Bild 14) zeigen und die Simulationsergebnisse somit belegen.

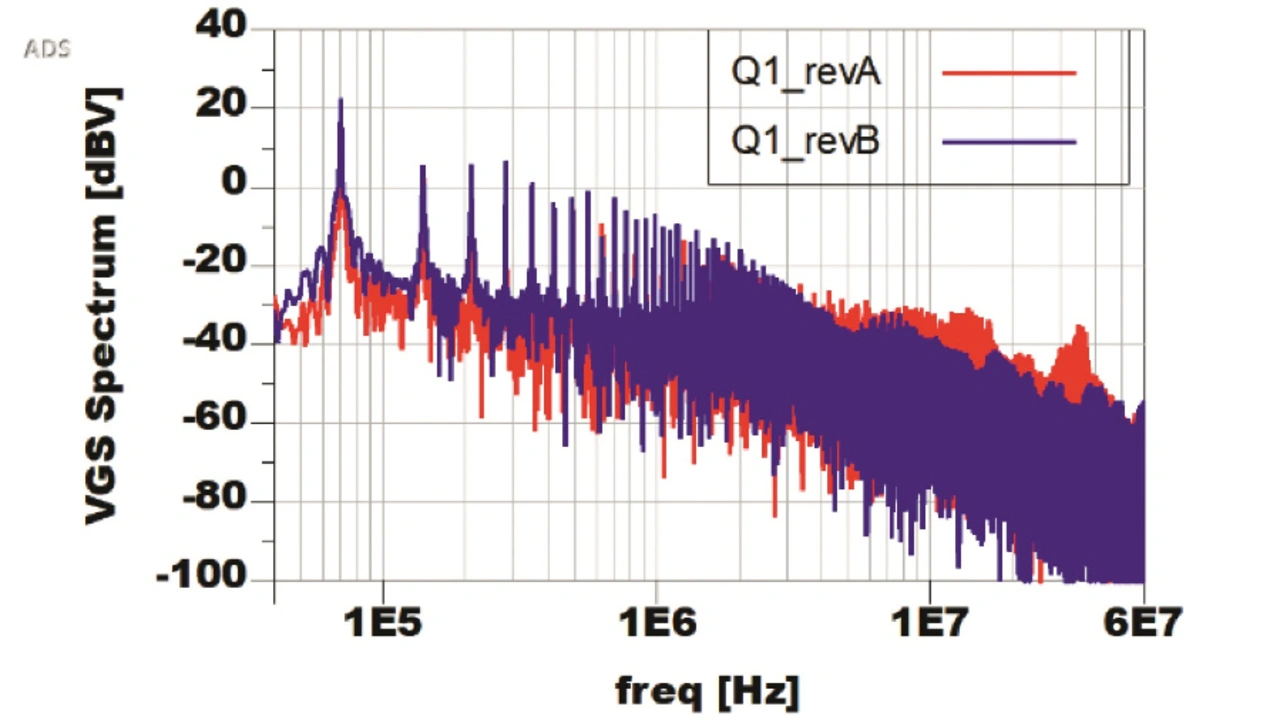

Bild 15 zeigt das Frequenzspektrum der zwei Layoutvarianten im Vergleich. Im Bereich 10 MHz bis 40 MHz zeigt die erste Variante deutlich höhere Emissionen, was an den nachgewiesenen Schwingungen im System liegt. Eine weiterführende Diskussion der Frequenzantwort des Gleichrichtersystems wäre Gegenstand einer weiteren Publikation. Das bereits erwähnte Modul PEPro bietet hierzu eine virtuelle EMV-Kammer, die die zu messenden Fernfeldergebnisse nach CISPR25 automatisch erstellt.

Schlussfolgerungen

Die parasitären Effekte auf Leiterplatten begrenzen oder verringern gar die Leistungsfähigkeit moderner, schnell schaltender Gleichrichtersysteme und sollten von Beginn des Entwurfsprozesses an berücksichtigt werden. Dadurch lassen sich spätere Redesigns oder gar funktionale Ausfällen vorbeugen.

Das Tool ADS mit PEPro bietet hierzu gute Voraussetzungen, um schnell ungewollte Kopplungen und deren Einfluss auf das Schaltverhalten vorauszuberechnen. Durch die recht einfache Bedienung bei der Erzeugung eines EM-extrahierten S-Parameter-Modells sowie die Methode der integrierten Co-Simulation lassen sich Produkte wie dieser 11-kW-Gleichrichter mit SiC-MOSFETs schnell und ausreichend genau entwerfen.

- Streuparameter analysieren

- Designmethode und Simulation

- Abschätzung der Streuinduktivität