Aufbruch in eine neue Debug-Dimension

Multi-Core-MCUs effizient debuggen

Fortsetzung des Artikels von Teil 1

Häufige Fehlerbilder beim Umstieg auf Multi-Core-MCUs

Erfahrungsgemäß werden die meisten Entwickler beim Umstieg von Single- auf Multi-Core-MCUs mit dem einen oder anderen der folgenden Fehlerbilder konfrontiert werden:

Bei älterem Code wird die Kommunikation zwischen einzelnen Tasks über globale Variablen, also über einen gemeinsam sichtbaren Speicher realisiert. Während die Tasks, die wechselseitig auf ein und derselben CPU ausgeführt werden, immer mit dem aktuellen Wert einer solchen Variable arbeiten, kann das auf einem Multi-Core-System mit verteilten Tasks ganz anders aussehen. Core-lokale Caches und Write-Buffer verzögern hier unter Umständen das Schreiben auf den gemeinsamen Speicher, so dass es leicht zu Inkonsistenzen kommen kann. Im schlimmsten Fall wird dann einfach mit dem falschen Wert gerechnet.

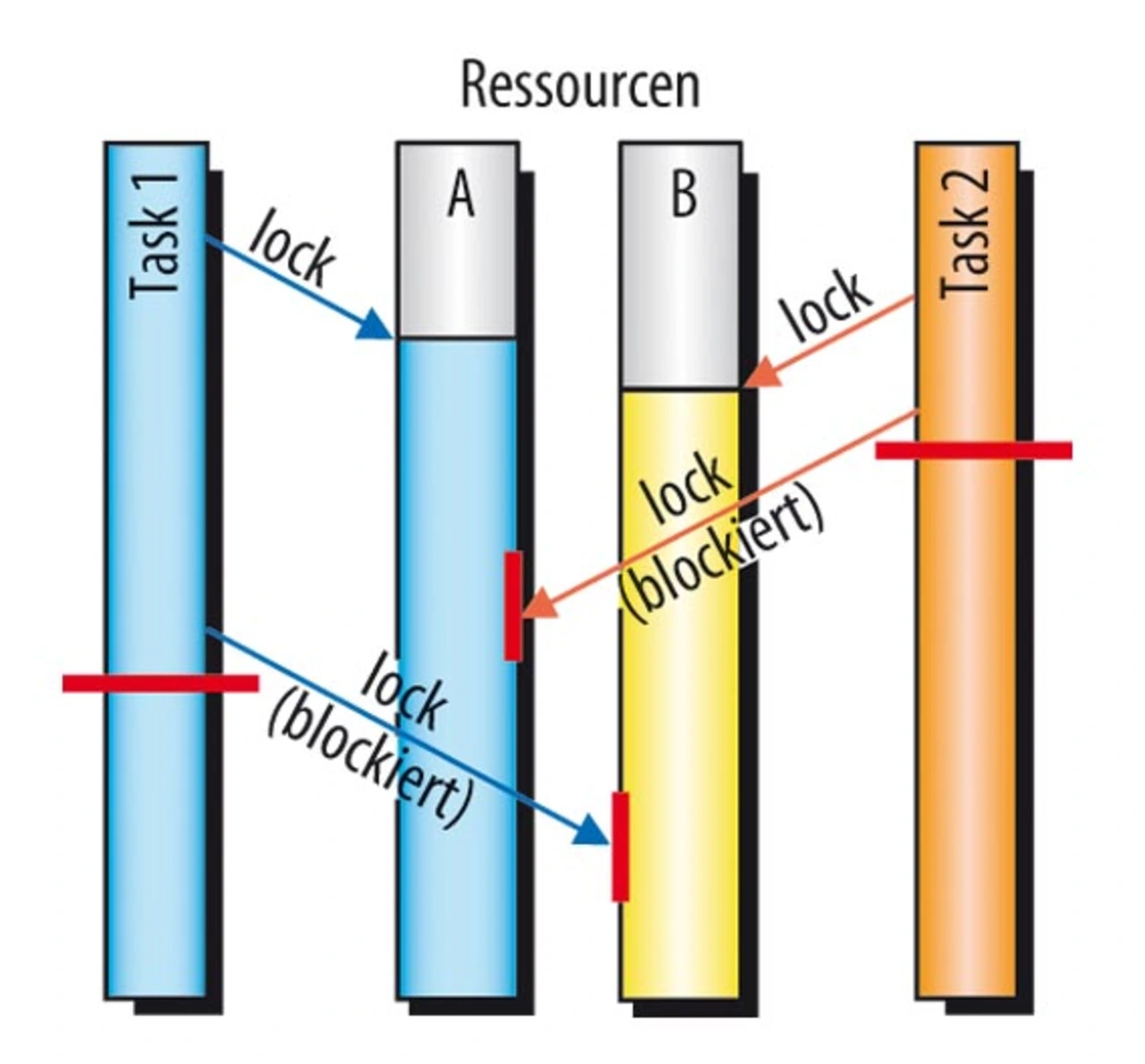

Ein oft auftretendes Fehlerbild bei echt nebenläufigen Prozessen, wie sie ja typisch für Multi-Core-MCUs sind, ist der Deadlock (Bild 2). Benötigen die Tasks 1 und 2 beispielsweise zwei Ressourcen A und B und versuchen diese zu reservieren, dann kann bei ungünstiger Reihenfolge der Reservierungen Task 1 die Ressource A und Task 2 die Ressource B blockieren. Versuchen dann beide Tasks die noch fehlende Ressource ebenfalls zu reservieren, blockieren beide. Auf einem Single-Core-System war dieses Problem nicht sichtbar, da beide Tasks sequenziell abgearbeitet wurden und die Reservierungssequenz eines Tasks immer vollständig ausgeführt wurde.

- Multi-Core-MCUs effizient debuggen

- Häufige Fehlerbilder beim Umstieg auf Multi-Core-MCUs

- Kein übergreifender Zeitbezug für Multi-Core-Systeme

- Jenseits von Stop & go

- Bilder sagen mehr als Worte