Sehtest für Kamerasysteme

Entwicklungsplattform für kamerabasierte Fahrerassistenzsysteme

Fortsetzung des Artikels von Teil 2

Softprozessor als System-Controller

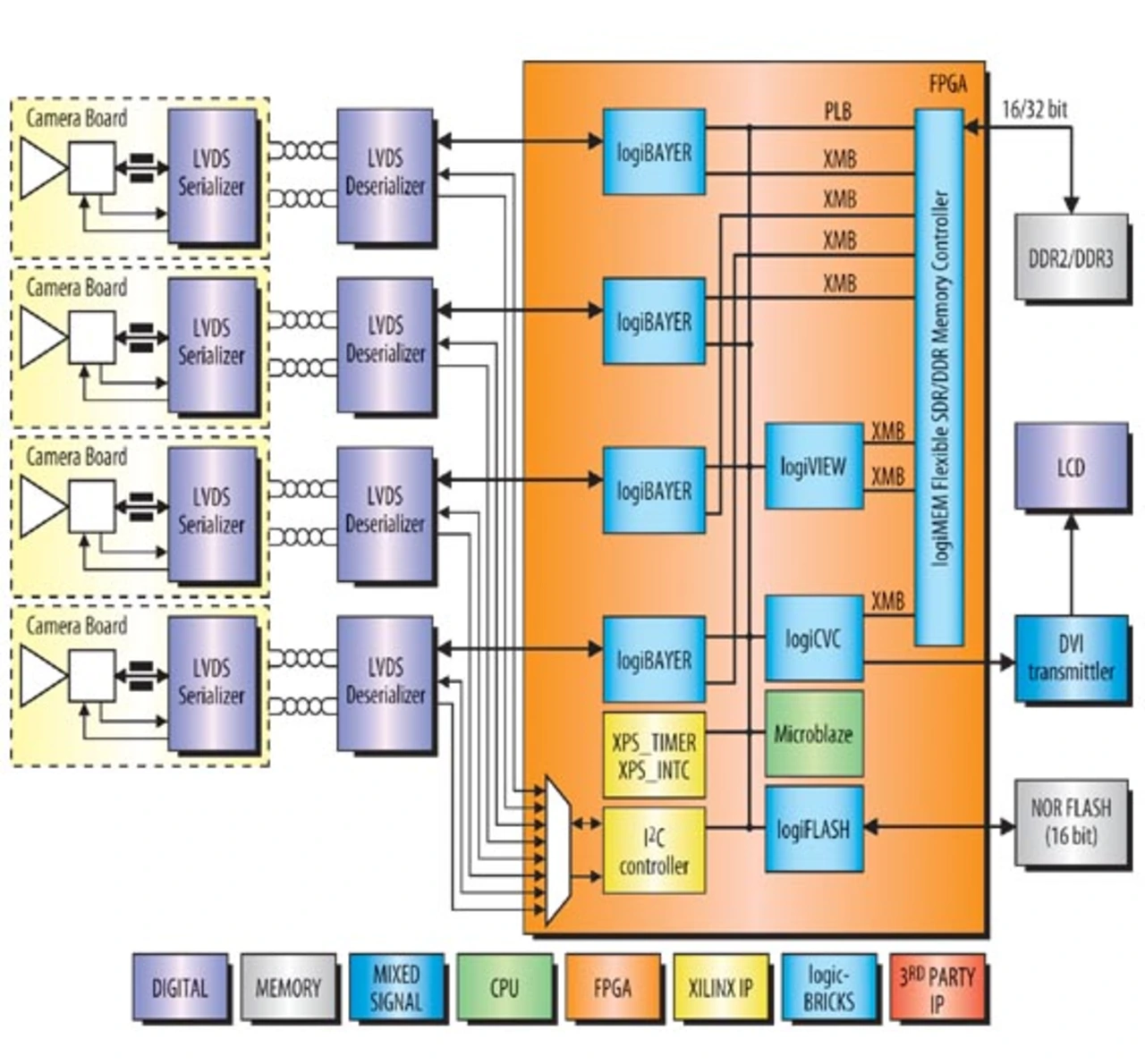

Die Schlüsselkomponente des Bird’s-Eye-View-Systems ist ein Xilinx-Spartan-6-FPGA, dessen Design unter Zuhilfenahme der logicBRICKS-IP-Cores entwickelt wurde (Bild 4). Zentrales Steuerelement dieses Designs ist der Xilinx-Softprozessor MicroBlaze, der wiederum über logiMEM-Speichermodule auf externe Flash- und DDR3-SDRAM-Speicher zugreift. Letzteres gewährleistet eine hohe Datenübertragungsrate bei der Aufzeichnung und Bearbeitung der Video-Informationen sowie deren Ausgabe auf einem Display. Das FPGA unterstützt eine

DDR3-Übertragungsrate bis zu 1,6 Gbyte/s. Das verwendete NOR-Flash speichert die Applikation und grafische Elemente wie Menüs.

Über eine I2C-Schnittstelle werden die hochauflösenden Kameras (1280 × 800 Pixel @ 30 fps) angesteuert. Die I2C-Schnittstelle kann optional auch durch andere Schnittstellen ersetzt werden.

LVDS-Deserializer liefern den Bayer-kodierten Video-Strom direkt von den CMOS-Sensoren der Kameras an das FPGA. Dort konvertiert der IP-Block logiBAYER die Signale in das RGB-Format. Das so gewonnene Bild wird unkorrigiert im DDR3-SDRAM gespeichert.

Die eigentliche Bildbearbeitung im FPGA erfolgt im logiVIEW-Modul. Es korrigiert die durch Weitwinkellinsen hervorgerufenen Verzerrungen und kann die Perspektive von Bildern und Videos anpassen. Die programmierbare Homographic-Transformation-Matrix ermöglicht verschiedene, perspektivische Korrekturen und Transformationen wie z.B. Rotation, Skalierung, Übersetzung, Beschneidung und eine simultane Kombination dieser Funktionen. Zudem übersetzt logiVIEW die aufgenommenen Kamerabilder in die Bird’s-Eye-Perspektive. Dank einer Parallelisierung der Bildverarbeitungsalgorithmen, wie sie in FPGA-Systemen üblich ist, dauert die Verarbeitung aller vier Kamerasignale nur unwesentlich länger als das Einlesen nur eines Kamerabildes. Das FPGA kann in Abhängigkeit von der Bausteingröße eine fast beliebig große Anzahl von Video-Eingängen ohne Einbruch der Systemleistung verarbeiten. Die letztendliche Anzahl der möglichen Video-Ein- und -Ausgänge hängt von verschiedenen Systemparametern ab, etwa der maximal möglichen Speicherdatenübertragungsrate oder der Bildwiederholrate.

Nach der Aufbereitung der einzelnen Kamerasignale werden diese noch für die Darstellung auf dem Display präpariert. Der IP-Block logiCVC (Compact Video Controller-Multilayer) bietet vielfältige Funktionen für eine optimale Darstellung von Bildern und Videos auf einem Display. Zu seinen Funktionen zählen unter anderem verschiedene Auflösungen, Timing-Anforderungen, Farbtiefen sowie Layer-, Pixel- oder Alpha-Blending mit Farbtabellen.

Jobangebote+ passend zum Thema

- Entwicklungsplattform für kamerabasierte Fahrerassistenzsysteme

- FPGAs liefern Flexibilität zur Ansteuerung verschiedener Sensortypen

- Softprozessor als System-Controller

- Flexibilität auch bei der Systemkalibrierung