Flash-Speicher

Off-Chip-Flash ist besser fürs IoT

Fortsetzung des Artikels von Teil 1

Herausforderung Nr. 1: Leistungsengpässe

Der Aufbau eines externen Flashs als Direktzugriffsspeicher in XiP-Architekturen ist eine anspruchsvolle Angelegenheit. So sind der Prozessor und der externe Flash separate Bausteine, die über eine serielle Busschnittstelle verbunden sind. Bei einer herkömmlichen seriellen Schnittstelle werden die Daten seriell über jeweils eine einzelne Leitung übertragen. Dies führt zu Leistungsengpässen und Datenflusslatenzen, insbesondere in Systemen mit hohen Leistungsanforderungen.

Der Hersteller hat den XiP-Speicher EcoXiP so konzipiert, dass der Flash schnell auf Leseanforderungen der Host-MCU reagiert und Anweisungen sowie Daten mit geringer Latenz und hohem Durchsatz bereitstellt. Der Speicher ist zum neuesten Octal-SPI-Protokoll (xSPI) der JEDEC kompatibel, wodurch die Kommunikation viel schneller erfolgt als mit einem seriellen Single-Wire-Flash. EcoXiP verfügt über intelligente serielle Peripherieschnittstellen mit mehreren Leitungen, um den Datenfluss zwischen der CPU und dem externen Flash zu beschleunigen und Daten über acht parallele Datenleitungen gleichzeitig zu übertragen.

Zudem bietet Adestos XiP-Speicher die bei Hochgeschwindigkeits-DRAMs übliche doppelte Datenrate (DDR). DDR sendet Datenbits sowohl an der steigenden als auch an der fallenden Flanke des seriellen Takts. Moderne serielle Flash-Bausteine liefern Taktraten von mehr als 100 MHz. Da das Senden eines Datenbits nur einen halben Taktzyklus dauert, kann DDR den Durchsatz des externen Speichers verdoppeln. Durch die Kombination der Octal-Schnittstelle mit der DDR-Funktion wird der Durchsatz des xSPI-Protokolls über einen seriellen Single-Wire-Flash um das 16-fache erhöht.

EcoXiP adressiert auch die Latenz, indem es den Overhead der Befehlsschnittstelle reduziert. Der Continuous-Modus des Befehls »Burst Read with Wrap« ermöglicht einen schnelleren Zugriff auf Daten, indem er die Anzahl der für nachfolgende Datenlesevorgänge erforderlichen Taktzyklen verringert. Mithilfe dieses Befehls erübrigt es sich, einen Befehl und eine Adresse zu senden und anschließend in aufeinanderfolgenden Cache-Fehlern auf die Array-Zugriffszeit (Dummy-Zyklen) warten zu müssen. Dies kann bei solchen Zugriffen etwa 20 Zyklen einsparen und die durchschnittliche Latenz aus Sicht der CPU verringern.

Herausforderung Nr. 2: Energieeffizienz

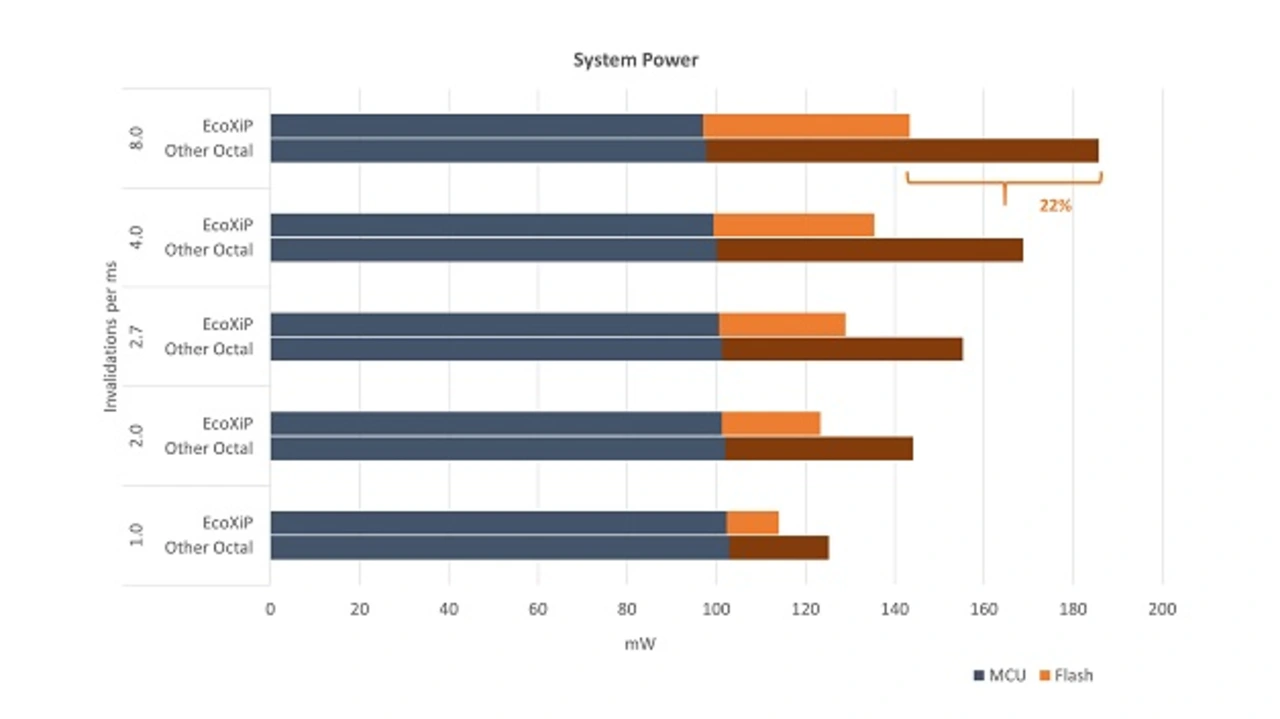

Eine weitere Schwierigkeit beim Aufbau eines XiP-Systems mit diskreter CPU und externem Flash besteht darin, dass die Stromversorgung dieser beiden separaten Bausteine zusätzlich zu der für die Interkommunikation benötigten Energie den Gesamtstromverbrauch eines Systems erhöht. EcoXiP mindert dieses Risiko, indem es im XiP-Modus einen geringeren Stromverbrauch bietet. Bei 133-MHz-Octal-SPI-Lesevorgängen beträgt der EcoXiP-Lesestrom 35 mA – etwa die Hälfte des Werts ähnlicher Octal-SPI-Bausteine. Darüber hinaus gehören zu EcoXiP konfigurierbare I/O-Treiber. Indem man die Treiberstärke optimiert, kann man den für die Kommunikation zwischen CPU und dem Speicherbaustein erforderlichen Stromverbrauch niedrig halten.

Darüber hinaus bietet EcoXiP Deep-Power-Down- und Ultra-Deep-Power-Down-Modi für Zeiten, in denen die CPU den Flash-Speicher nicht benötigt. Im Ultra-Deep-Power-Down-Modus verbraucht der Baustein nur 200 nA, was zu einem sehr niedrigen Stromverbrauch mit nur geringen Auswirkungen auf die Wake-up-Zeit führt.

Der Ultra-Deep-Power-Down-Modus bietet einen weiteren Vorteil von XiP gegenüber RAM-basierten Systemen: Der Stromverbrauch des Flashs in diesem Modus ist deutlich geringer als der des On-Chip-SRAM oder des externen DRAM. Einige Entwickler, die mit RAM arbeiten, haben sich dafür entschieden, den Speicher im Deep-Sleep auszuschalten. Dies würde jedoch ein erneutes Laden des RAM von einem externen Flash erfordern, was zeit- und stromfressend ist.

Herausforderung Nr. 3: Over-the-Air-Updates

Programminformationen auf dem externen Flash über Funk zu aktualisieren (Over-the-Air-/OTA-Update), fordert Entwickler von XiP-Systemen ebenfalls heraus. Das Schreiben in den Flash mit einem OTA-Update kann ihn daran hindern, über einen längeren Zeitraum auf Lesevorgänge zu reagieren, wodurch der nächste Befehl, den das System für das Update benötigt, zu einem Verarbeitungsstopp führt.

Durch den gleichzeitigen Lese- und Schreibvorgang von EcoXiP (Read-While-Write; RWW) kann der Host-Prozessor weiterhin von einer Partition des Flash-Speicher-Arrays lesen und gleichzeitig Daten auf einem anderen Teil ändern. So wird bei der periodischen Datenaufzeichnung, bei der Lösch- und Programmiervorgänge auf dem seriellen Flash-Speicher ausgeführt werden, das XiP-Programm nicht angehalten. Mit der RWW-Funktion setzt sich der Befehls- und Datenabruf während der Programmierung wie gewohnt in einer anderen Partition des Flashs fort.

Fazit

Off-Chip-Flash-Speicher ist zwar nicht immer die Antwort auf jede Herausforderung, der sich Chipentwickler gegenübersehen – jedoch bietet eine XiP-Architektur die Möglichkeit, erweiterbare Mengen an externer Software und Datenspeicherplatz für neue Anwendungen zu unterstützen, insbesondere für Edge-IoT- und KI-Anwendungen. Der Einsatz von externem seriellen Flash in Verbindung mit einem Embedded-Prozessor bietet eine skalierbare Plattform, die sich an viele Herausforderungen von heutigen Embedded-Systemen anpasst. (kv)

- Off-Chip-Flash ist besser fürs IoT

- Herausforderung Nr. 1: Leistungsengpässe