Siliziumkarbid - Teil 3

Zuverlässigkeit und praktische Erfahrungen mit SiC

Fortsetzung des Artikels von Teil 1

Die Zuverlässigkeit der Body-Dioden und SiC-Modulen

Ein weiterer Mechanismus, der sich auf die Zuverlässigkeit von SiC-MOSFETs auswirkt, sind Beeinträchtigungen durch das Leiten der Body-Diode. Wenn ein dauerhafter Vorwärtsstrom durch eine SiC-pn-Sperrschicht fließt, wie sie in den Body-Dioden von MOSFETs existiert, vermehren sich sogenannte Stapelfehler infolge der Rekombinationsenergie von Elektronen und Löchern. Derartige Fehler beeinträchtigen den Stromweg und lassen damit den Durchlasswiderstand und die Vorwärtsspannung der Diode ansteigen. Vervielfacht sich der Rds(on), so macht dies die thermische Auslegung zunichte. Auch die Sperrspannung kann sich durch Stapelfehler verschlechtern. So können gravierende Probleme entstehen, wenn SiC-MOSFETs, deren Body-Dioden durch Stromfluss beeinträchtigt werden, in Schaltungstopologien eingesetzt werden, die ein Kommutieren der Body-Diode bewirken, z.B. Wechselrichter in Brücken-Konfiguration. Dieses Zuverlässigkeitsproblem tritt nur bei bipolaren Bauelementen auf, jedoch nicht bei SiC-Schottky-Dioden oder bei SiC-MOSFETs im ersten Quadranten.

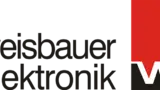

Rohm hat die Häufigkeit der Kristalldefekte in SiC-Wafern und Epitaxialschichten eingedämmt und einen proprietären Prozess entwickelt, der das Fortschreiten von Stapelfehlern verhindert, so dass die Zuverlässigkeit der leitenden Body-Diode sichergestellt ist. Dies bestätigt sich in 1000-Stunden-Tests mit 8 ADC, bei denen sich keine der Eigenschaften (auch nicht Rds(on), Leckstrom) verschlechterte. Dies ermöglicht die problemlose Nutzung von SiC-MOSFETs in Schaltungen, in denen es zu einer Kommutierung der Body-Diode kommt. Rückstrom-Zuverlässigkeitsprüfungen mit Ugs = 18 V und Id = 15 ADC (ebenfalls über 1000 Stunden) ergaben ebenfalls keine nennenswerten Änderungen der elektrischen Eigenschaften (Bild 3).

Da die Chipfläche von SiC-MOSFETs kleiner und die Stromdichte höher ist als bei Si-Bausteinen, ist ihre Kurzschlussfestigkeit (Ausfall durch thermisch bedingte Brüche) tendenziell schlechter als die von Si-Produkten. Der SCWT-Wert (Short Circuit Withstand Time) von 1200-V-SiC-MOSFETs im TO247-Gehäuse liegt bei 8 bis 10 µs (Udd = 700 V; Ugs = 18 V). Der SCWT-Wert steigt bei niedrigeren Gate-Spannungen infolge des geringeren Sättigungsstroms und reduzierten Versorgungsspannungen an.

Viele Gate-Treiber-ICs sind mit Funktionen ausgestattet, die das Erkennen von und den Umgang mit Kurzschlüssen vereinfachen. So kann der BM6103FV-C von Rohm den Baustein innerhalb von ca. 2 µs abschalten, sobald ein Überstrom erkannt wird. Mit seiner Soft-Turn-Off-Fähigkeit reduziert er die Gate-Spannung während des Abschaltens so langsam, dass hohe Spannungsspitzen infolge der hohen dI/dt-Werte an der Drain- und Source-Induktivität verhindert werden. Ratsam ist, das Anlegen zu hoher Spannungen durch eine Soft-Turn-On-Funktion oder anderer Vorsichtsmaßnahmen zu unterbinden.

Es gibt bei Si-MOSFETs einen Ausfallmechanismus, bei dem hohe dU/dt-Werte kurze Stromspitzen durch die Drain-Source-Kapazität fließen lassen und den parasitären Bipolar-Transistor einschalten, was einen Durchbruch des Bausteins zur Folge hat. Dieses Phänomen ist bei SiC-MOSFETs unwahrscheinlich, da die Stromverstärkung ihrer parasitären Bipolar-Transistoren gering ist. Bei SiC-MOSFETs von Rohm wurde der Ausfallmechanismus bei dU/dt-Werten bis 50 kV/µs bisher nicht beobachtet. Die sehr niedrigen Sperrverzögerungsströme von SiC-MOSFETs verursachen ebenfalls keine steilen Spannungsspitzen, so dass das Auftreten dieses Ausfallmechanismus bei SiC-MOSFETs als unwahrscheinlich angesehen wird.

Anwendung und Zuverlässigkeit von SiC-Power-Modulen

Da SiC-Module hohe Schaltgeschwindigkeiten und hohe Ströme ermöglichen, können durch die Leitungsinduktivität im Modul selbst oder an den externen Schaltungen Spannungsspitzen entstehen (U = L x dI/dt), die die Nennspannung übersteigen. Die folgenden Maßnahmen können dieses Problem abmildern oder beseitigen, haben jedoch Auswirkungen auf die Schalteigenschaften:

- Verringern der Leitungsinduktivität durch Verwendung kurzer Leitungen mit großem Querschnitt in den Haupt- und Snubber-Stromkreisen.

- Anschluss von Kondensatoren in der Nähe der MOSFETs zur Senkung der Leitungsinduktivität.

- Hinzufügen Snubber-Schaltung.

- Anheben des Gate-Widerstands zur Reduzierung der dI/dt-Werte.

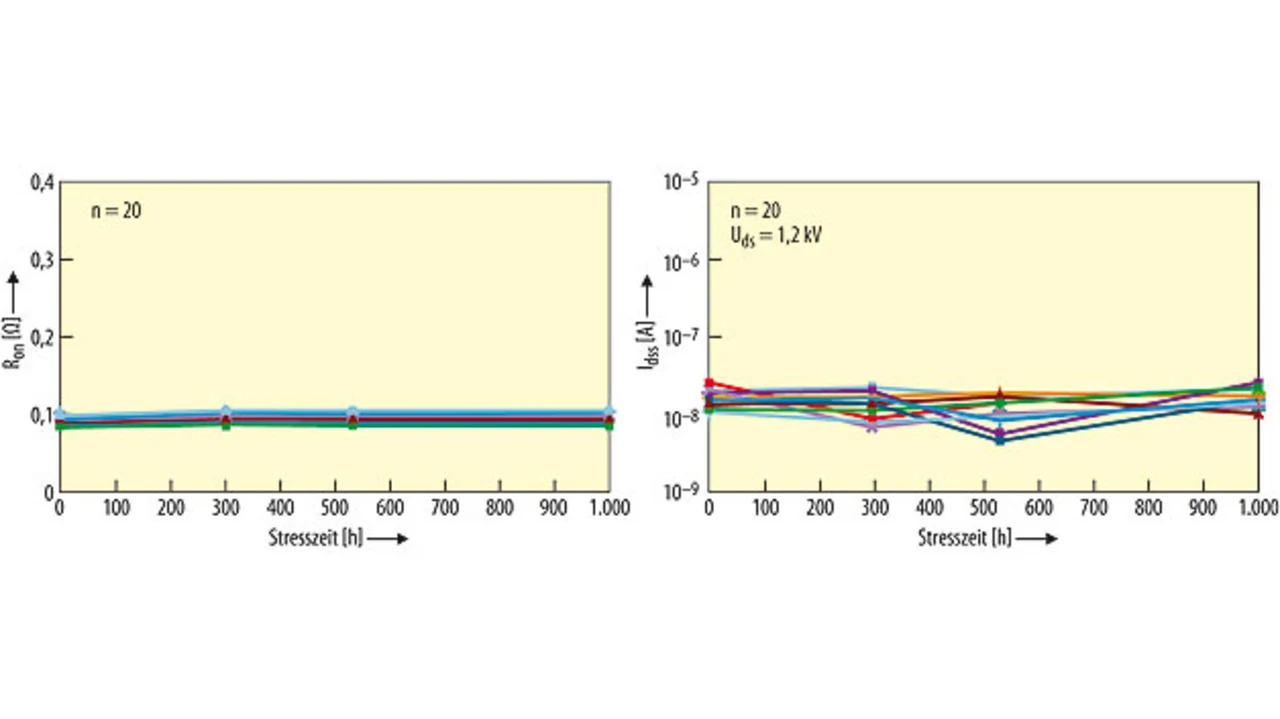

Bild 4 zeigt den oberen Zweig einer Halbbrücke. Wenn der MOSFET M1 einschaltet, fließt in der Freilaufdiode, d.h. in einer externen SiC-SBD oder der Body-Diode, des MOSFET M2 im unteren Zweig ein Sperrverzögerungsstrom, der die Uds von M2 ansteigen lässt. In Folge dieses dU/dt fließt ein kurzzeitiger Gate-Strom durch die Miller-Kapazität Crss von M2 in den Gate-Widerstand, was die Zunahme der Gate-Spannung an M2 bewirkt. Wird dabei die Gate-Schwellenspannung von M2 überschritten, fließt ein Kurzschlussstrom durch den oberen und den unteren Zweig.

Während die bei einigen Milliampere definierte Schwellenspannung von SiC-MOSFETs nur rund 3 V beträgt, wird für höhere Ströme eine Schwellenspannung von 8 V oder mehr benötigt. Die Kurzschlussfestigkeit des Brückenzweigs ist deshalb nicht wesentlich anders als bei IGBTs. Um aber den soeben beschriebenen unerwarteten Kurzschluss zu vermeiden, werden die nachfolgend angeführten Maßnahmen empfohlen – auch bei Si-Power-Modulen. Da sich diese Maßnahmen jedoch auf die Schalteigenschaften auswirken können, ist ein Einstellen der Schaltung unter Beobachtung der Wellenformen anzuraten, um ein ungewolltes Einschalten zu unterbinden:

- Zum Abschalten des MOSFET negative Gate-Vorspannung anheben.

- Einfügen eines Kondensators zwischen Gate und Source.

- Einfügen eines Transistors zwischen Gate und Source, um Ugs bei abgeschaltetem Schalter auf das Massepotenzial zu klemmen.

- Zur Reduzierung der Schaltgeschwindigkeit Gate-Widerstand erhöhen.

Ebenso wie bei IGBT-Modulen umfasst der RBSOA (Reverse Bias Safe Operating Area) von SiC-Power-Modulen den gesamten Bereich bis zum doppelten Nennstrom.

- Zuverlässigkeit und praktische Erfahrungen mit SiC

- Die Zuverlässigkeit der Body-Dioden und SiC-Modulen

- Anwendungen und Vorteile