Die Peripherie macht's

Die rein digitale Regelschleife

Fortsetzung des Artikels von Teil 2

Die rein digitale Regelschleife

Auflösung und Latenzzeit

Die Wahl der Topologie für eine Anwendung bestimmt sich durch die Spezifikation des Netzteils. Verschiedene Topologien bedeuten auch unterschiedliche PWM-Modi wie Standard-, Komplementär-, Gegentakt-, Multiphasen-, Variabler-Phasen-Modus, Strom-Reset- und Strombegrenzungsmodus. Deshalb muss man richtig verstehen, warum die PWM-Auflösung so wichtig ist. Wenn ein PWM-Modul nicht genügend Auflösung bietet, wird das PWM-Ausgangssignal oszillieren, um die gewünschte mittlere Ausgangsspannung zu erhalten.

In Netzteilanwendungen kann dieses PWM-Dithering Brummströme (Ripple) erzeugen und die Regelung in einen bedrohlichen Betriebszustand fahren, »Limit Cycling« genannt. Daher muss der Entwickler einen DSC mit ausreichend hoher Auflösung wählen, um dieses Risiko auszuschließen.

Ebenso wichtig ist es für Entwickler, den Begriff Latenzzeit richtig einzuordnen. In einer Regelschleife versteht man darunter die Zeit, die zwischen der Erfassung der Spannungs- und Strommesswerte bis zur Ausgabe eines neuen Taktratenwertes am PWM-Modul vergeht. Je kürzer die Latenzzeit ist, desto stabiler und exakter reagiert die Regelschleife. Einige DSCs haben PWM-Module, die neue Taktratenwerte nur taktweise akzeptieren. Die Zeitverzögerung durch die Neuberechnung eines Taktratenwertes mittels Software – bis das PWM-Modul also den neuen Wert annimmt – erhöht die Latenzzeit der Kontrollschleife und verringert die Stabilität. Daher sollte man einen DSC mit einem PWM-Modul einsetzen, das die neuen Taktratenwerte sofort akzeptiert und verarbeitet.

Einige Erkenntnisse über analoge Schaltungen können für den Einsatz von DSCs in »intelligenten« Netzteilen recht hilfreich sein. A/D-Wandler sorgen für die Rückmeldung des Systemstatus und sind herkömmlicherweise so konzipiert, dass sie die Abtastwerte in einem Block zusammenfassen und berechnen. Blockabtastung ist in der Audiosignalverarbeitung und in industriellen Steuerungen typisch, jedoch tritt die Spitzenbelastung des Prozessors dann entsprechend dieser Blöcke auf, und die Latenzzeit verlängert sich.

Eine kontinuierliche Überwachung von Signalen ist mit A/D-Wandlern nicht möglich, die Abtastungsgeschwindigkeit ist deshalb auf die Abtastrate des Datenwandlers begrenzt. Einige DSCs haben analoge Komparatoren, die den Prozessor und den ADC zugunsten anderer wichtiger Aufgaben entlasten. So lassen sich analoge Komparatoren zum Beispiel für die Stromregelung einsetzen, ähnlich wie in herkömmlichen Netzteilreglern zur direkten Regelung der PWM-Taktrate. Analoge Komparatoren eignen sich auch zur unabhängigen Überwachung von Überspannungs- und Überstromzuständen.

Nehmen wir zum Beispiel an, die Referenz-DACs und analogen Komparatoren auf den DSCs erreichen von der Strommessung bis zur PWM-Aktualisierung Latenzzeiten von etwa 25 ns. Dann beträgt die typische Zeit von der Erkennung der analogen Spannung bis zur Änderung am PWM-Ausgang durch den Komparator ebenfalls ungefähr 25 ns. Diese Reaktionszeit ist schneller, als sie von Universal-ADCs erreicht wird, die erst eine Abfrage starten müssen, um die PWM-Ausgänge an die veränderten Bedingungen anzupassen. Die Referenz-DACs und analogen Komparatoren auf einem DSC, der für Netzteilanwendungen optimiert ist, sind hier eine wirkungsvolle Hilfe, die taktweise Strombegrenzung für den Stromregelmodus zu realisieren.

PID-Algorithmus

Der PID-Algorithmus kann für Spannungs- und Stromregelschleifen eingesetzt werden. Mit dem PID-Algorithmus werden proportionale, integrale und differenzielle Fehler der tatsächlichen gegenüber der gewünschten Ausgangsspannung zusammengefasst, um die PWM-Taktrate zu regeln.

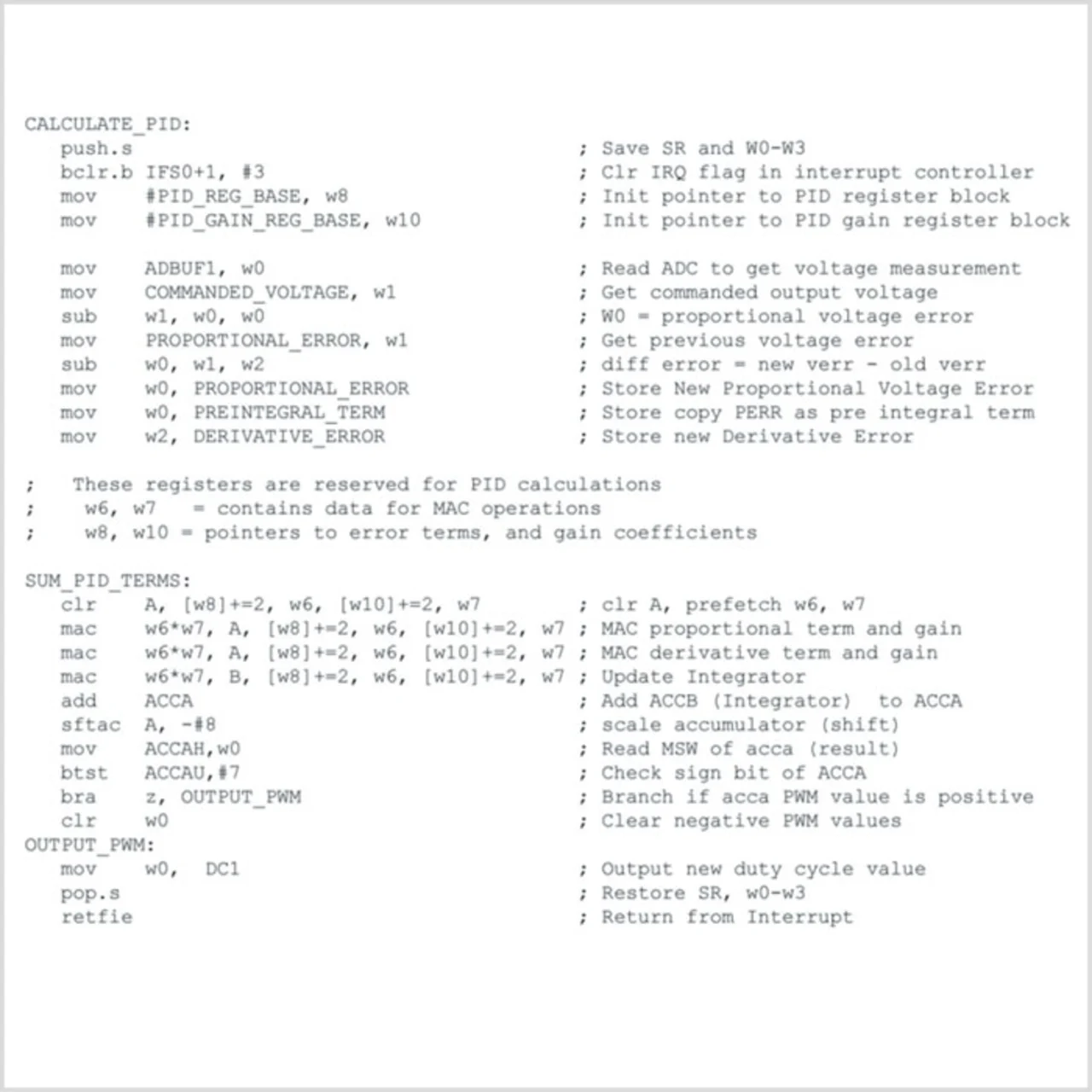

Da die DSP-Funktionen innerhalb der geläufigen Mikrocontrollerarchitektur bekannt sind – zum Beispiel für den »dsPIC« von Microchip –, müssen keine umfangreichen Kenntnisse zur Programmierung des DSPs und Implementierung des PID-Algorithmus’ erworben werden (Bild 5).

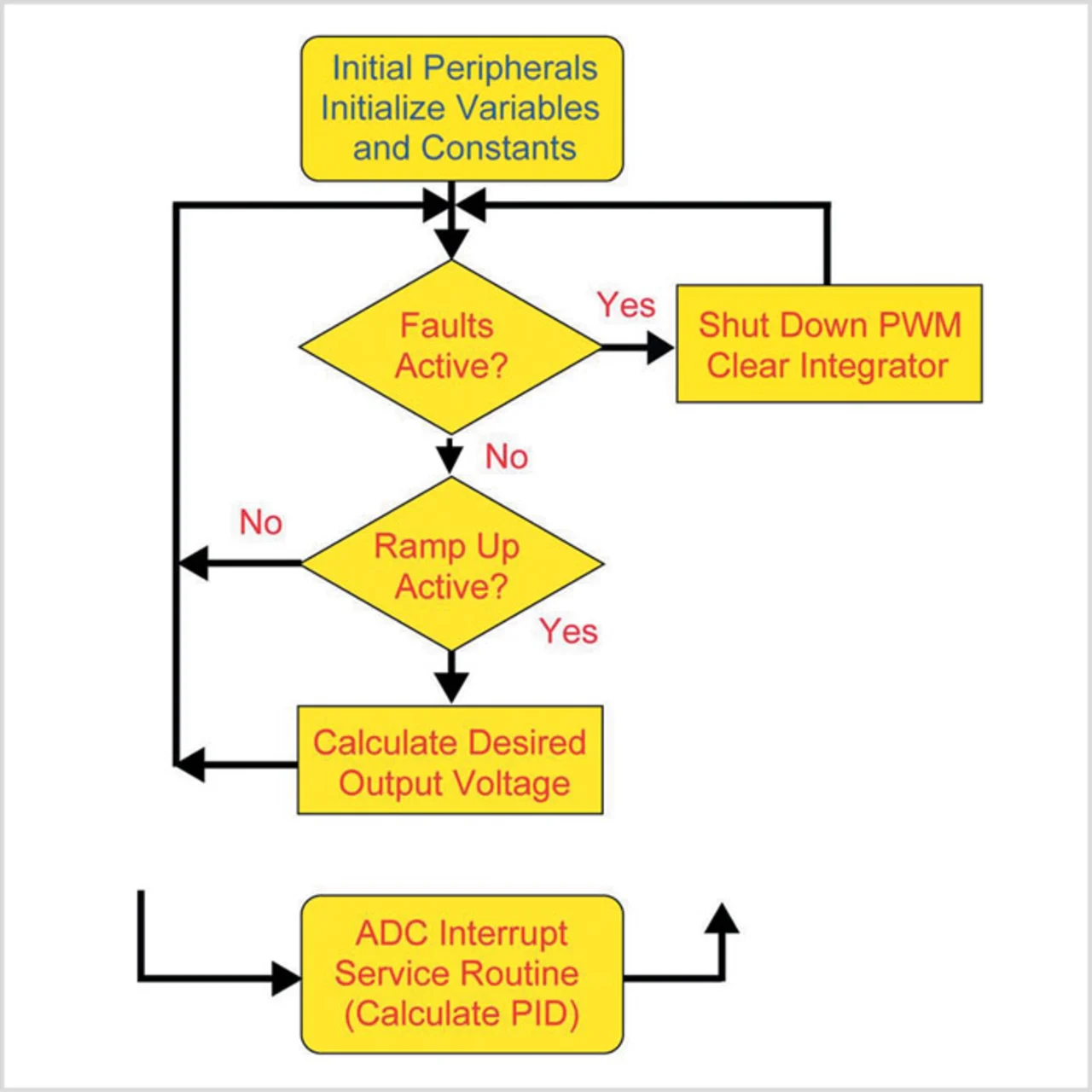

Die PID-Schleife ist das Herzstück der Kontrollsoftware (Bild 6). Obwohl die Software typischerweise nicht so umfangreich ist, ist die Ausführungsrate sehr hoch. Oft werden Hunderttausende Iterationen pro Sekunde abgearbeitet. Diese hohe Rate erfordert PID-Softwareroutinen, die so effizient wie möglich sind und die Leistung maximieren. Ein Assembler hilft, den Code des PID-Algorithmus’ so kompakt wie möglich zu halten.

Da die PID-Kontrollschleife auf einer festen Zeitbasis durch den A/D-Wandler unterbrochen wird, kann der DSC in der Leerlaufzeit der Schleife andere Systemfunktionen ausführen, sodass der Overhead der PID-Software geringer wird. Funktionen wie das Hoch- und Runterfahren der Spannung, Fehlererkennung, Vorausberechnung und Routinen zur Kommunikationsunterstützung können in der Leerlaufschleife ausgeführt werden.

Zur Netzteilsoftware gehört der Regelalgorithmus mit der durch den Interrupt des ADCs gesteuerten PIDSchleife als zeitkritischstem Teil. Die PID-Software sollte nicht mehr als etwa 66% der verfügbaren Prozessorbandbreite verbrauchen, sodass der Rest der Rechenleistung für Software der Leerlaufschleife zur Verfügung steht. Bei einer Rate von 30 MIPS werden demzufolge die 30 Befehle in der PID-Schleife in etwa 1 μs ausgeführt. Beträgt die Iterationsrate 500 kHz oder 2 μs, dann benötigt die PID-Auslastung die Hälfte der zur Verfügung stehenden Prozessorbandbreite oder 15 MIPS.

Der Autor:

Bryan Kris ist Staff Architect für die DSC-Division bei Microchip.

- Die rein digitale Regelschleife

- Die rein digitale Regelschleife

- Die rein digitale Regelschleife