PCIe 3 und Co

Schnelle Schnittstellen testen

Fortsetzung des Artikels von Teil 2

Weitere Messungen

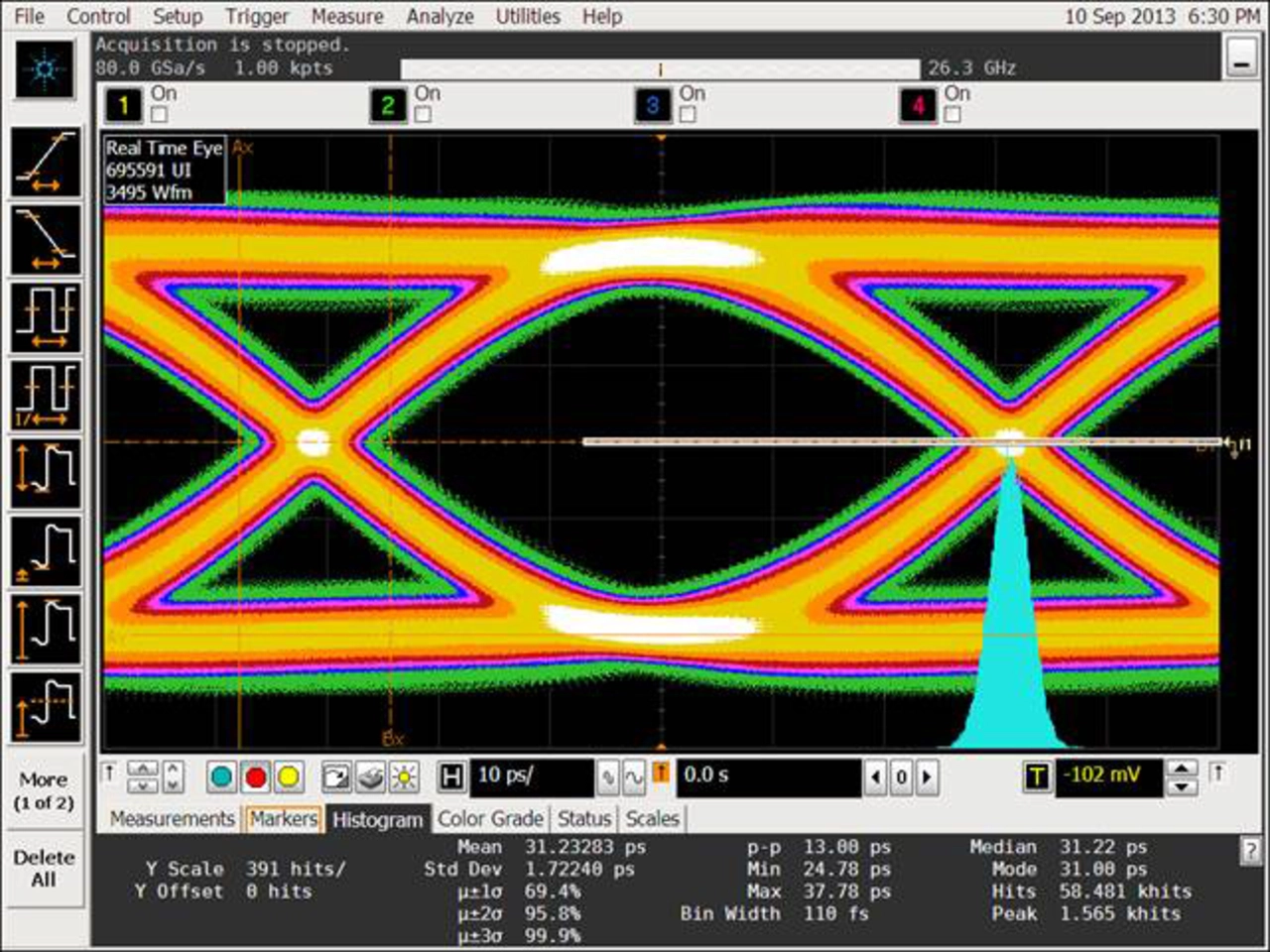

Ebenfalls sind PLL-Tests möglich, die Taktsynchronisierungsfähigkeiten und Toleranzen verifizieren. Dazu erlaubt es Pin Scale SL, sogenannte Frequenz-Offset-Tests durchzuführen und Jitter-Toleranz-Profile zu messen.

Jobangebote+ passend zum Thema

Als Pattern für die meisten ACTests werden generische pseudozufällige

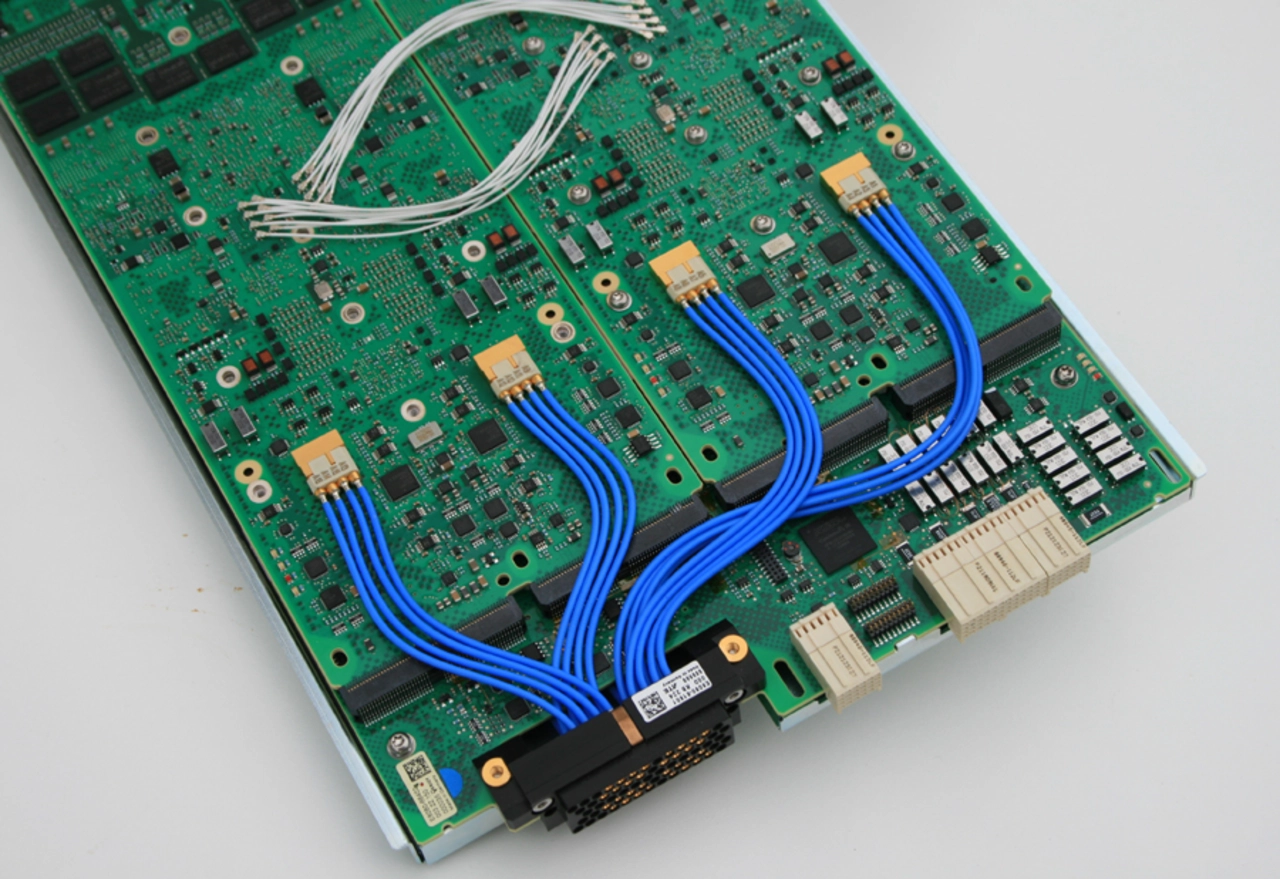

Bitsequenzen PRBS (Pseudo-Random Bit Sequence) verwendet. Diese Sequenzen sind periodisch und enthalten hoch- und niederfrequente Anteile (beispielsweise enthält die PRBS mit der Periodizität 27–1 maximal sieben aufeinanderfolgende gleiche Zustände). Interessant ist hierbei, wie das Design mit einer Clock-Folge 0101 und einem Zustandswechsel nach einer langen statischen Phase, beispielsweise 0000001, zurechtkommt. Beide Muster sind in der entsprechenden PRBS anzutreffen. Im Bereich der Netzwerktechnik sind oftmals PRBS mit sehr langer Periodizität, wie etwa 231–1, vorgeschrieben. Diese Patterns können nur durch Hardware-Generatoren sinnvoll erzeugt werden, da die Programmierung als Benutzer-Pattern nicht im vorhandenen Speicher abgelegt werden kann. Daher enthält Pin Scale SL programmierbare Pseudo-Random-Data-Generatoren und selbstsynchronisierende Vergleicher, die völlig autark in jedem zu testenden Link gleichzeitig genutzt werden können (Bild 3).

Generische ATE-Fähigkeiten

Zusätzlich zu den oben genannten spezifischen High-Speed-I/O-Fähigkeiten verfügt das Pin Scale SL über den klassischen Satz von digitalen Testfähigkeiten, die den strukturellen Test-Support wie Scan-Test unterstützen, d.h. speicherbasierter Pattern Support, inklusive bidirektionaler Ein/Aus-Datenverkehr auf allen Pins. Wichtig ist diese Fähigkeit, wenn die Pins der Hochgeschwindigkeitsschnittstelle auch gleichzeitig zum Zugriffspfad für die Validierung der Logik im Kern des SOC werden.

Des Weiteren verfügt das neue Instrument über native PCIe-3-Fähigkeiten. Somit ermöglicht es die Kommunikation zwischen Prüfling und ATE auf einem höheren Abstraktionsniveau, etwa um durch diesen Zugriffspfad interne Selbsttests in Nicht-Test-Modi des SOC zu konfigurieren und deren Ergebnisse auszulesen [5].

Akzeptanz am Markt

2014 hat Advantest ca. 90 Pin-Scale-SL-Instrumente ausgeliefert. Mehr als die Hälfte davon sind in der Volumenproduktion in Taiwan im Einsatz. Primärer Grund für die hohe Nachfrage ist der Ausbau der Mobilfunkinfrastruktur in China, bei dem eine Welle von neuen ASIC-Designs mit 10 und 12,8 Gbit/s-SerDes-Schnittstellen zum Einsatz kommt. Das Pin-Scale-SL-Instrument liefert genügend Bandbreite, um für die nächste Generation von ASIC-Designs mit 15 Gbit/s gerüstet zu sein.

In Kürze werden erste Entwürfe zum Standard der 4. Generation PCI Express (PCIe 4) veröffentlicht werden, und damit auch erste Testchips für diese Generation. PCIe Generation 4 soll mit einer Datenrate von 16 Gbit/s betrieben werden. Aber auch eine Reihe anderer, z.T. proprietärer Schnittstellendesigns mit SerDes-Technologie sind in Entwicklung, bei denen Pin Scale SL eingesetzt werden kann.

Literatur

[1] PCI Special Interest Group, www.pcisig.com

[2] Serial ATA International Organization, www.sata-io.org

[3] S. Palermo: ECEN720: High-Speed Links Circuits and Systems. Spring 2015. www.ece.tamu.edu/~spalermo/ecen689/lecture1_ee720_intro.pdf

[4] A. Rylyakov, S. Rylov: A Low Power 10 Gb/s Serial Link Transmitter in 90-nm CMOS, CSIC Symposium November 2, 2005.

[5] R. Nettles, F.Hensel: Protocol Aware ATE – Why and How to make the ATE speak PCIe. PCI-SIG Developer Conference 2014, Santa Clara 2014.

Die Autoren

|

Dr. rer. nat. Frank Hensel |

|---|

| ist Senior Applications Consultant für SOC-Testlösungen basierend auf der V93000-Plattform. Er verfügt über 15 Jahre Erfahrung im Bereich Messtechnik für digitale Hochgeschwindigkeitsschnittstellen und Halbleitertests und ist diesbezüglich Ansprechpartner für Kunden weltweit, Vertriebsmannschaft und Entwicklungsbereich. |

|

Dipl.-Ing. Ulrich Schoettmer |

|---|

| ist Produktmanager für SOC-Testlösungen bei Advantest. Er hat 35 Jahre Erfahrung im Bereich Halbleitertest in leitenden Positionen in Entwicklung, Anwendung, Marketing und Kundenberatung gesammelt und ist einer der Väter der heutigen V93000-ATE-Plattform. |

- Schnelle Schnittstellen testen

- Besondere Eigenschaften von digitalen Hochgeschwindigkeits-Schnittstellen

- Weitere Messungen