PCIe 3 und Co

Schnelle Schnittstellen testen

Fortsetzung des Artikels von Teil 1

Besondere Eigenschaften von digitalen Hochgeschwindigkeits-Schnittstellen

Bei der Serialisierung werden die Signale, die klassisch über parallele Signalpfade geführt werden, auf einen Signalpfad konzentriert. Dies hat in der Regel zur Folge, dass die Geschwindigkeit, mit der Daten in diesem Signalpfad übertragen werden, erhöht werden muss, um vergleichbare Datenübertragungsraten zu erreichen. Um die für die Signalübertragung benötigte Leistung klein zu halten (~C·f·U2; C: Typ-Kapazität, f: Frequenz, U: Spannungshub), wird mit kleiner Spannung U übertragen. Dies führt bei vielen Schnittstellen zum Wechsel auf differenzielle Signale. Bei diesem Verfahren ist der Störabstand deutlich verbessert. Erkenntnisse aus der Leitungstheorie werden angewendet, um Störungen und Verluste durch Reflexionen an Impedanzübergängen zu vermeiden. So sind beispielsweise auch Sender und Empfänger immer entsprechend dem jeweiligen Standard korrekt zu terminieren. Wurde anfänglich nur auf korrekte Terminierung geachtet, so ist man mit zunehmender Datenrate zu immer ausgefeilteren Maßnahmen der aktiven Frequenzgangkorrektur

übergegangen, um frequenzabhängige Leitungsverluste im PCB oder Kabelmaterial ausgleichen zu können. Man spricht hier in der Literatur

von Equalization. Senderseitig sind bei Datenraten >10 Gbit/s heute FIR (finite impulse response) und empfängerseitig DFE (decision feedback equalization) Stand der Technik (10GbE-KR, PCIe Gen. 3) [3].

Um den Aufwand der Signalverteilung weiter zu verringern, wird in vielen Fällen auf die gesonderte Übertragung eines Referenztaktes (Clock) verzichtet. In der Welt der parallelen Busse existieren Hilfssignale, die in der seriellen Welt abgebildet werden. Diese Abbildungen werden durch Protokolle definiert. Diese Protokolle beschreiben auch die Bündelung mehrerer serieller Kanäle (Lanes) zu einem Link. Hierbei wird der Datenstrom in der Regel auf alle Lanes gleichmäßig aufgeteilt, um möglichst kurze Antwortzeiten zu erreichen.

Aus den Eigenschaften der digitalen Hochgeschwindigkeits-Schnittstellen lassen sich allgemeine Testanforderungen ableiten, die auch für Produktionstests von Bedeutung sind. Die typische Testliste für High-Speed-SerDes-Technologie umfasst die nachfolgenden Punkte.

DC-Tests

Durch die Einführung der aktiven Equalization in seriellen Hochgeschwindigkeits-Schnittstellen gestaltet sich der Analogteil von Treiber und Empfänger deutlich komplexer [4]. Dadurch ergibt sich eine Vielzahl interner Spannungsteiler, Stromquellen etc., die strukturell

mit Strom- und Spannungsmessungen getestet werden können (DC Margin Tests, wie Ausgangspegel, Ausgangs-Offset, Ausgangsstrom, Eingangs-Leckstrom, Eingangs-Impedanz, differenzieller Abgleich).

Dafür stellt Pin Scale SL ein Präzisions-DC-Messwerk mit einer Genauigkeit von besser als ±2 mV, ±10 nA oder ±0,5 % hinter jedem I/O-Pin zur Verfügung, so dass Messungen auf allen Ressourcen parallel und damit schnell ausgeführt werden können.

Jobangebote+ passend zum Thema

Dynamische AC-Tests

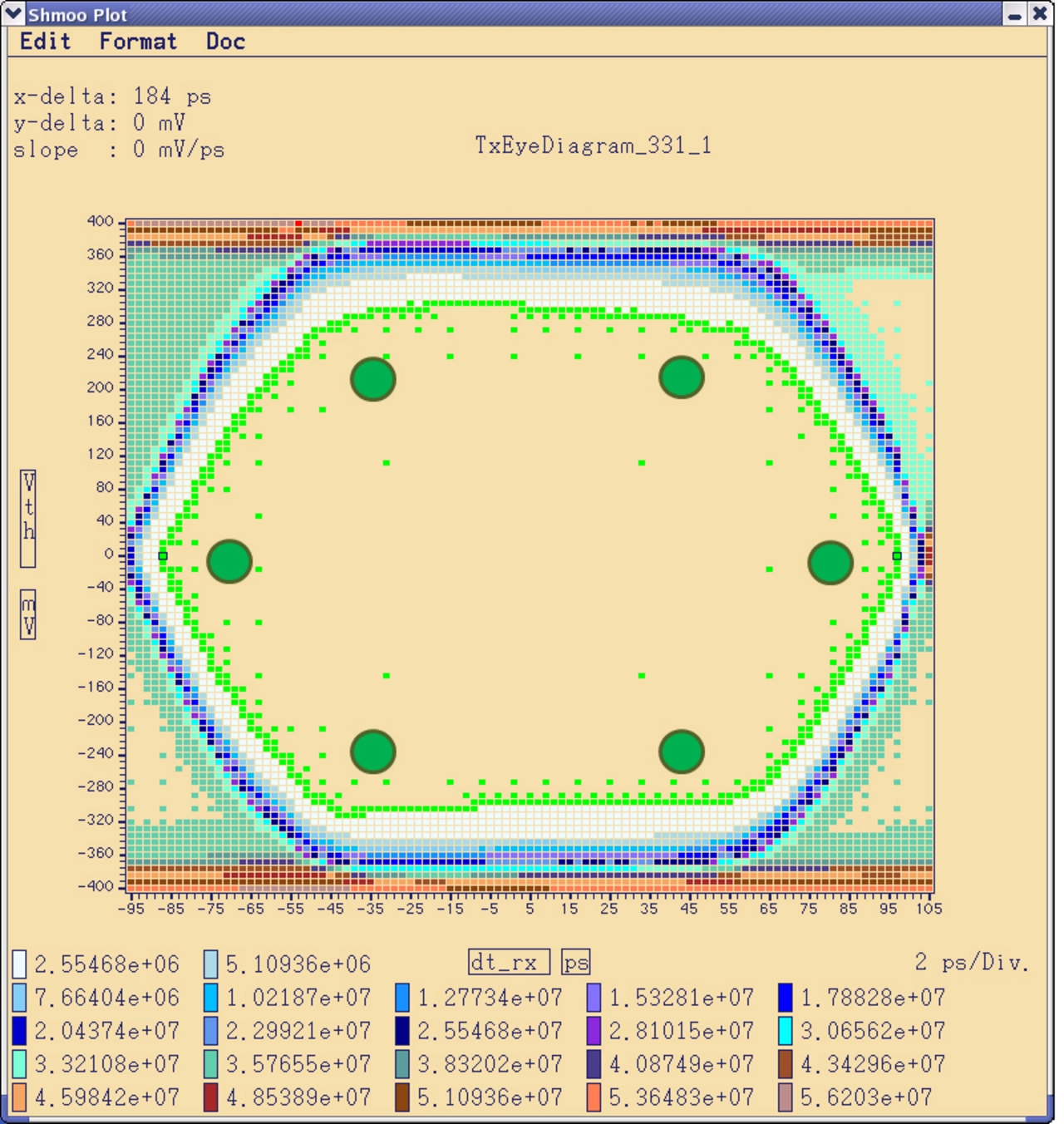

Bei dynamischen AC-Tests werden durch Messung der SerDes-Blöcke bei nominaler Datenrate die Hochgeschwindigkeitseigenschaften verifiziert. Dabei werden auf der Senderseite (TX) des Prüflings die Eye-Mask-Tests und Jitter-Messungen durchgeführt. In den Eye-Mask-Tests wird die Augenhöhe und -breite bestimmt (Bild 1). Zur beschleunigten Erfassung der Messwerte werden oft nur wenige (typisch sechs) Eckpunkte als Go/NoGo-Test ausgeführt, daher der Name n-Punkt-Maskentest. Für die Jitter-Messungen werden bitfehlerratenbasierte (BER) Histogramme erfasst und RJ/DJ-Separationen nach dem Dual-Dirac-Verfahren vorgenommen. In der Produktion lassen sich diese Messungen auf ein Erfassen des totalen Jitter, für das sich die integrierte Time Measurement Unit (TMU) gut eignet, reduzieren. Jeder einzelne Kanal verfügt über ein eigenes TMU-Instrument, so dass die Messwerterfassung voll parallel auf allen Links ausgeführt wird.

Auf der Empfängerseite (RX) des Prüflings werden durch Stimulation mit verzerrten Signalen die Grenzen der Signalaufbereitung bestimmt. Dabei wird die Eingangsempfindlichkeit gemessen, ebenfalls in Bezug auf Pegel (Augenhöhe) und Timing. Und mit der Methodik des gestressten Auges wird Jitter definiert injiziert (Amplitude in Pikosekunden, Frequenz als Parameter).

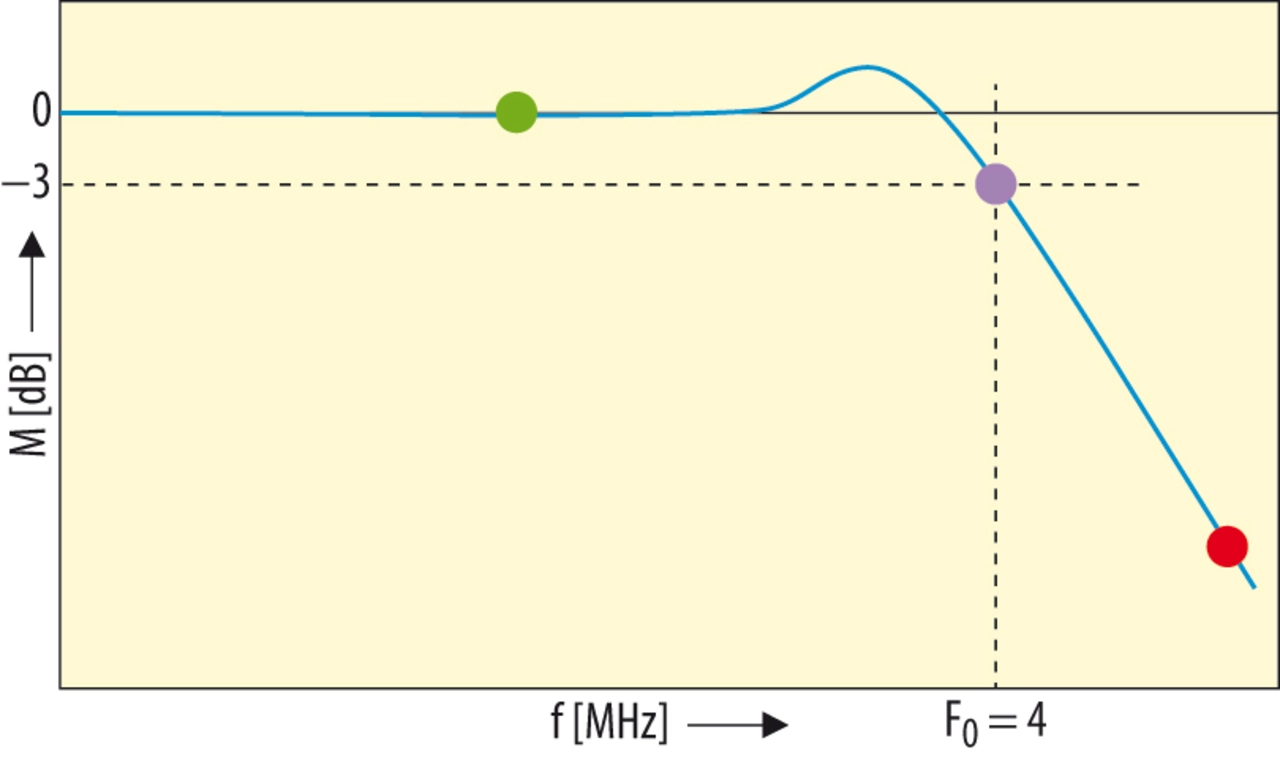

Hier stellt Pin Scale SL programmierbare Pegel sowie hochgenaue Timing-Generatoren, die bis in den Pikosekunden-Bereich einstellbar sind, in der Pin-Elektronik bereit. Die Fähigkeiten, dem Empfänger ein Datenauge mit Stress zu liefern, werden abgerundet durch die Möglichkeit der gesteuerten Injektion von Jitter. Diese kontrollierten Störungen im Zeitbereich dienen der Validierung der CDR (clock data recovery) bzw. PLL des Empfängers. Messungen bei verschiedenen Jitter-Frequenzen zeigen, ob die gewünschte Charakteristik vorliegt (Bild 2). Diese Messungen ermöglichen eine Bewertung, inwiefern das Design mit ähnlichen Störungen in der realen Applikation umgehen kann.

- Schnelle Schnittstellen testen

- Besondere Eigenschaften von digitalen Hochgeschwindigkeits-Schnittstellen

- Weitere Messungen