Bring-up von Prototypen-Hardware

Hardwarefehler finden

Der Bring-up von Prototyp-Leiterplatten ist einer der wichtigsten Schritte für ein Designteam. Boards, die gar nicht oder nicht erwartungsgemäß funktionieren, können ein Projekt bezüglich Marktstart und Kosten komplett aus dem Ruder laufen lassen. Die üblicherweise eingesetzten sondenbasierten Methoden weisen erhebliche Nachteile auf. Einerseits schrumpft ihre Abdeckung ständig und anderseits steigen ihre Kosten. Eine Alternative bieten softwarebasierte, berührungslose Techniken wie Boundary-Scan und Embedded-Instrumente.

Wenn die Prototypen eintreffen, denken viele Techniker sofort daran, eines der Boards hochzufahren, um zu sehen, was passiert − mit katastrophalen Folgen, falls die Leiterplatte größere Hardwarefehler aufweist. Diese Defekte können schweren Schaden anrichten, wenn das Board »unter Strom gesetzt« wird. Stattdessen sollte der für das Bring-up zuständige Techniker zunächst einige visuelle Stichproben machen. Lose oder nur teilweise aufgelötete Komponenten, verbogene Pins, kleine Metallfragmente und andere Defekte können die Platine beschädigen, sobald die Stromversorgung eingeschaltet wird. Bei einer kurzen visuellen Inspektion lassen sich oft die schlimmsten Fehler erkennen.

Sobald der Bring-up-Techniker sicher ist, dass das Board nicht »abraucht«, wenn er die Stromversorgung aktiviert, sollte er die verschiedenen Spannungsregler testen. Dazu eignet sich ein Digitalmultimeter. Ursache für Fehlspannungen können defekte Bauteile, Kurzschlüsse, offene Pins oder eine Aktivierungsleitung zu einem Spannungsregler sein, die nicht korrekt anspricht.

Neben dem Betrieb mit den richtigen Spannungen sollte das System auch in der korrekten Abfolge mit Strom versorgt werden (Sequencing). In der Regel reicht ein kostengünstiges Oszilloskop, um die tatsächliche Schaltreihenfolge der Platine mit den Vorgaben in den Spezifikationen zu vergleichen. Eine fehlerhafte Reihenfolge ist in der Regel ein Hinweis darauf, dass die Firmware für den Power-Controller fehlerhaft ist.

Auf der Suche nach Strukturdefekten

Zu diesem Zeitpunkt sollte auch die Taktung der wichtigsten Prozessoren und Chipsätze des Boards geprüft werden. Ohne korrektes Timing auf der gesamten Leiterplatte startet das System nicht richtig oder ist sogar vollkommen funktionsuntüchtig. Der nächste Schritt kann schwierig sein. Das Board wird mit Strom versorgt und die Taktgeber funktionieren, aber das Board startet trotzdem nicht. Die Symptome, die auf die zugrundeliegenden Probleme verweisen, sind dabei oft recht unterschiedlich.

Das System lässt sich nicht initialisieren, oder es bootet zwar, funktioniert aber nicht; beziehungsweise es startet, um dann unregelmäßige Fehler zu bringen. Wo liegt nun das Problem? In der Hardware, in der Firmware, in der Software oder gar in allen dreien? Am besten fängt man auf der untersten Ebene an. Das heißt, der Techniker überprüft das System auf Hardwarefehler. Er sollte insbesondere kontrollieren, ob das Board korrekt bestückt wurde.

Die berührungslose, softwarebasierte Boundary-Scan-Testmethode auf Basis des Standards IEEE 1149.1, auch JTAG genannt, kann sehr effektiv Strukturdefekte wie Kurzschlüsse und offene Pins erkennen. Um einen Boundary-Scan-Test durchzuführen, muss lediglich ein minimaler Teil des Boards funktionstüchtig sein. Damit lässt sich die Netz- und Pin-Ebene prüfen, wie es sonst nur mit kontaktgebundenen Technologien wie MDA- (Manufacturing Defect Analyzers) und ICT-Systemen (In-Circuit Test) möglich wäre.

Für MDA und ICT sind jedoch teure Halterungen und Testsonden erforderlich. Viele Designs bieten heute aber gar keine Testpunkte mehr für den physischen Zugriff, wie sie für Testsonden nötig sind. Boundary-Scan eignet sich für Prototyp-Tests besonders gut, da die Technologie auf Software basiert und im Gegensatz zu Sondensystemen keinen physischen Zugang erfordert. Boundary-Scan ist auch die kostengünstigste Strukturtestmethode und kommt ohne teure Halterungen aus, wie sie für MDA und ICT benötigt werden.

Als digitale Testtechnologie kann Boundary-Scan in der Regel jedoch keine Abdeckung über das gesamte Fehlerspektrum hinweg bieten. Um zusätzliche Testabdeckung auf dem Prototyp zu erreichen, könnte der Techniker einen Processor-Controlled-Test (PCT) als nächste Testmethode nutzen. Wie beim Boundary-Scan muss auch beim PCT das Board für die Durchführung von Tests nicht gebootet werden. Und da der PCT eine Funktionstest-Technologie ist, die »at speed«, also mit realer Geschwindigkeit, arbeitet, bietet er sowohl Struktur- als auch Funktionstestabdeckung für ein Design.

Fehler bei High-Speed-Bussen finden

Hat der Prototyp alle Boundary-Scan- und PCT-Tests erfolgreich absolviert, kann der Bring-up-Techniker sicher sein, dass alle gröberen Strukturfehler entdeckt wurden. Der nächste Schritt vor dem Debugging der Firmware und Software ist die Suche nach weiteren Hardwarefehlern, die unter Umständen unentdeckt geblieben sind. Eine gute Stelle dafür sind High-Speed-Busse, da die Funktion der meisten Boards von korrekt arbeitenden Komponenten-Interconnects abhängt.

Es gibt mehrere Methoden, die Signalintegrität und die Leistung auf High-Speed-Bussen zu überprüfen. Viele Halbleiterhersteller betten Instrumente in ihre Chips ein, die sich zur Validierung solcher Busse eignen. Beispielsweise hat Intel den »Interconnect Built-In Self Test« (IBIST) entwickelt und baut diesen in alle seine High-End-Chips ein.

IBIST erkennt Fertigungs- und Prozessabweichungen wie Lufteinschlüsse in Lötstellen (Voids), Haarrisse, Head-in-Pillow-Effekte und ähnlich Probleme. Andere Chiphersteller wie PLX Technologies integrieren Embedded-Instrumente nach einem anderen IEEE-Standard, dem P1687 Internal JTAG (IJTAG). IJTAG standardisiert die Schnittstelle zu Embedded-Instrumenten, um diese zwischen Chips portieren sowie sie effektiver managen und steuern zu können.

Jobangebote+ passend zum Thema

Eine weitere Möglichkeit zum Testen von Prototyp-Boards ist die temporäre Einbindung von IJTAG-Instrumenten in ein funktionstüchtiges FPGA. Diese Methode wird als FPGA-Controlled-Test (FCT) bezeichnet. Natürlich wiederholen sich alle genannten Schritte, während das Design die einzelnen Phasen vom ersten Prototypenlauf bis zu den Vorproduktionsläufen durchwandert und dann abschließend ein endgültiger Freigabekandidat für die Massenfertigung wird. In der Produktentwicklung kommen im Laufe dieses Lebenszyklusprozesses viele Werkzeuge zum Einsatz.

Beim Board-Bring-up-Prozess in der Produkt-entwicklung, die mehrere Monate oder sogar Jahre dauern kann, ist ein höheres Maß an Tool-Automatisierung erforderlich, falls Prototypen in größeren Mengen produziert beziehungsweise wenn umfangreiche Vorproduktions-Boardläufe durchgeführt werden. Nur so lassen sich die Kosten im Griff behalten.

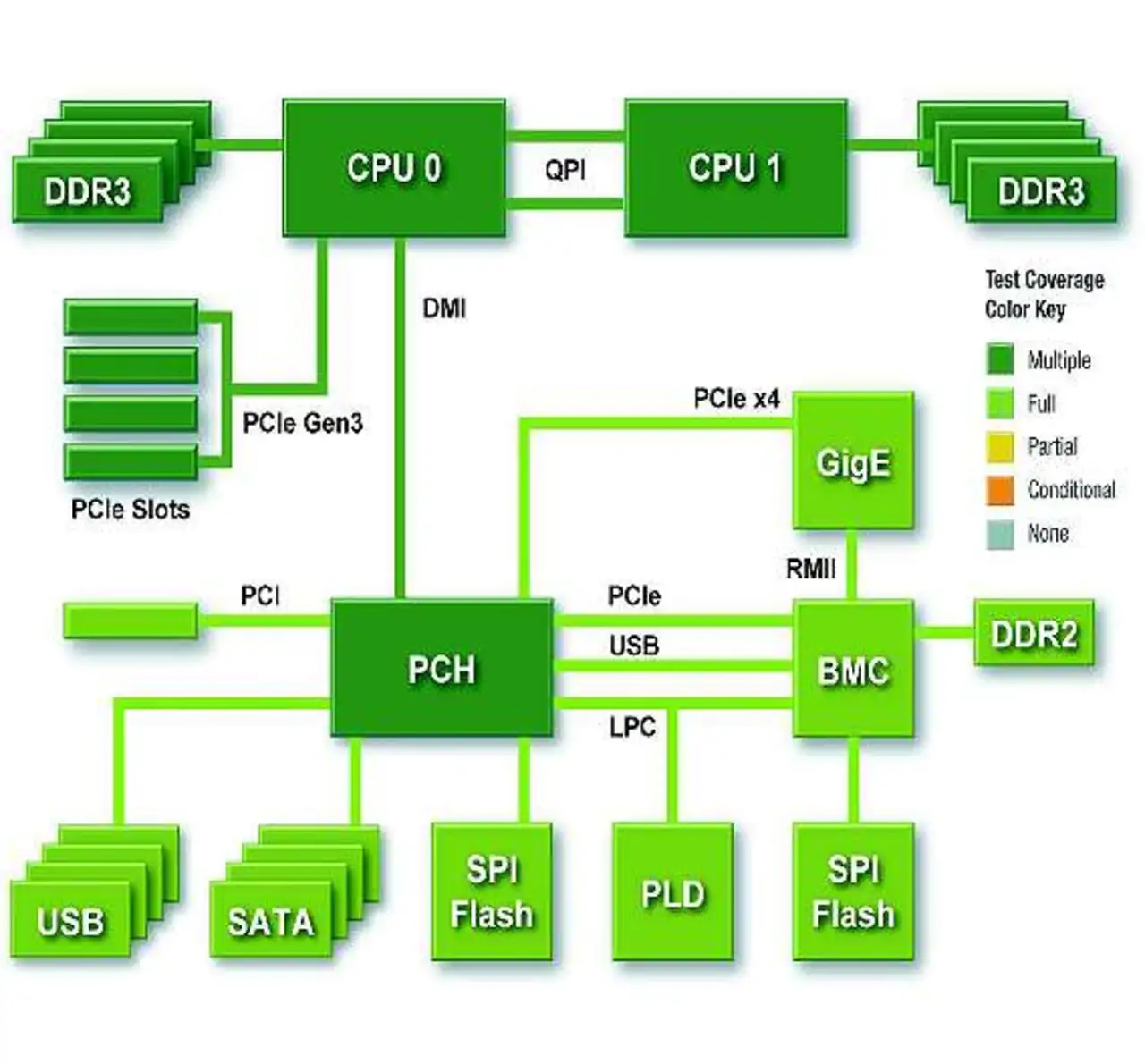

Bild 1 zeigt die kumulative Testabdeckung, die sich mit berührungslosen, softwarebasierten Boundary-Scan-Tests, Processor-Controlled-Tests und High-Speed-I/O-Tests erreichen lässt.

Über den Autor:

Reg Waller ist European Director von Asset InterTech.