Systemdesign / embedded-Test-Design

Abstraktion als Explorationskatalysator

Fortsetzung des Artikels von Teil 1

Konkrete Evaluation

D&E: Das klingt ja sehr theoretisch. Wie evaluiert man einen bestimmten Lösungspunkt?

AP: Letztendlich können Sie die Eigenschaft am Prototyp messen, Simulationen evaluieren oder einen analytischen Prototyp schätzen. Der Prototyp stellt dabei die langsamste Methode mit der höchsten Auflösung, die analytische Schätzung geht am schnellsten ist aber wage.

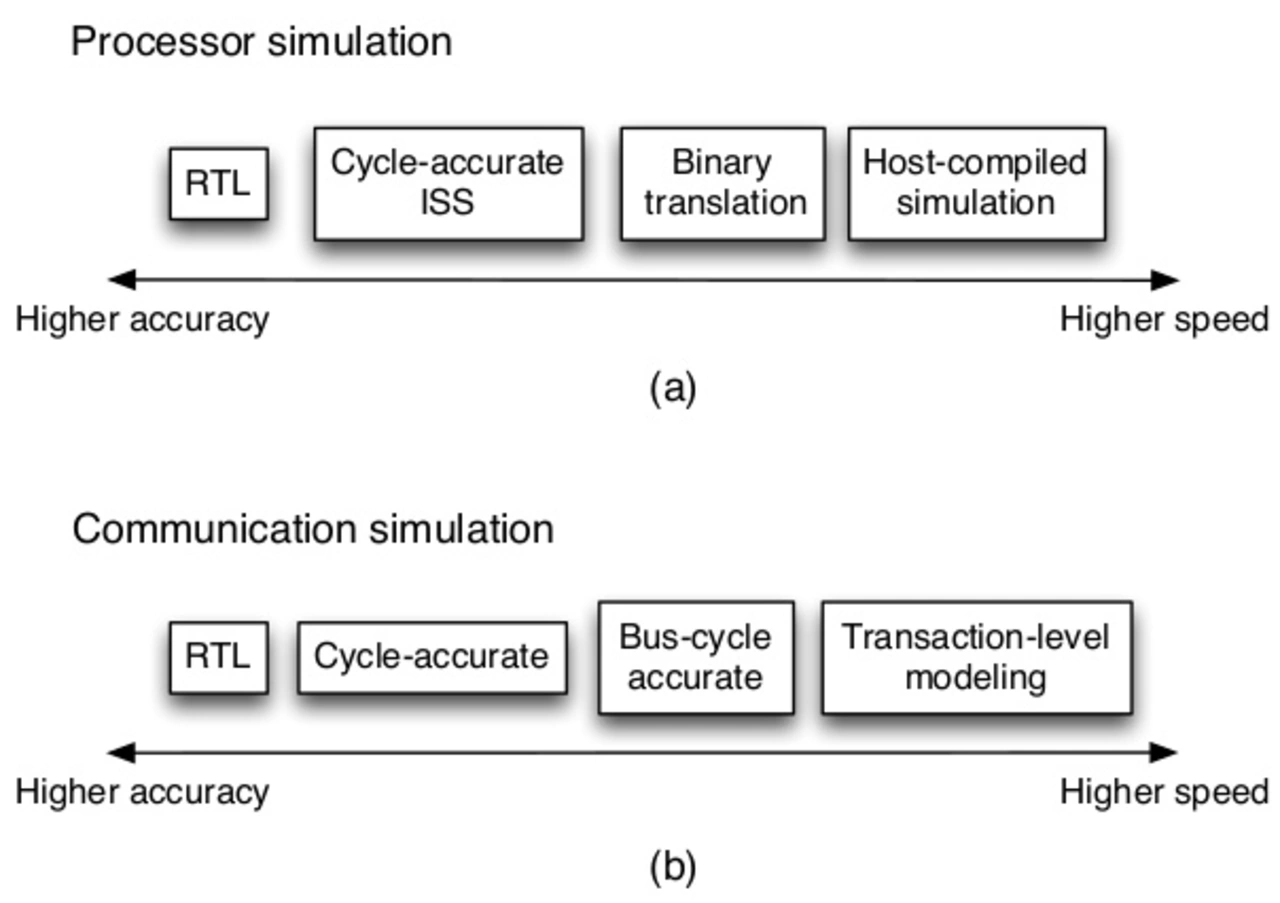

Wenn Sie so wollen liegt der Vorteil einer simulations-basierten Exploration in einer stufenlosen Skalierung zwischen diesen beiden Extremen. Um die Simulation besser zu begreifen, sollten die unterschiedlichen Abstraktionsebenen (Bild 1) verstanden sein.

Jobangebote+ passend zum Thema

Dazu könnten Sie ein digitales System in verarbeitende und kommunizierende Komponenten dividieren. Die exakteste und langsamste Simulation erfolgt dann auf RegisterTransferLevel. Dabei wird der digitale Signalfluss zwischen Registern und Logik explizit simuliert. Die Reichweite der RTL-Simulation zur Exploration ist daher stark limitiert. Typischerweise würden Sie so nur einzelne Systemkomponenten Ihres Designs betrachten.

Eine Abstraktionsebene darüber liegt das Systemverhalten pro Zyklus. Bei Mikroprozessoren ist dazu das ISS-Verfahren populär, welches das Verhalten pro Zyklus der verarbeitenden Logik, Caches, usw. wiedergibt. Der Energieumsatz wird dabei aus aktivitätsbasierten Leistungsmodellen berechnet.

Zur Exploration ist aber auch so ein Verfahren meist noch zu langsam.

Eine Stufe über den binär hinterlegten Einzelinstruktionen simuliert man ganze übersetzte Befehlssätze, bsp. mit QEMU. Zu den Befehlssätzen wird weitere Information, wie Leistung oder Timinig hinterlegt. Analog dazu wird die Kommunikation auf BUS-zyklus-genauem Niveau simuliert.

Ein weitere Stufe darüber findet host-kompilierte Simulation statt - Hier wird das Zielprogramm binär kompiliert und auf dem Host ausgeführt. Auch hier können Zusatzinfos zu Timing und Energieumsatz implementiert werden. Wegen seiner hohen Effizienz eignet sich das Programm zur Exploration, allerdings fällt es schwer dabei Vorgänge wie Verteilung oder das Cachen abzubilden.

Im Kommunikationspfad bedeutet TLM das höchste Abstraktionsniveau. Dabei fallen Signal- und Protokolldetails, nur noch die Transferfunktionalität wie Sender-/Empfängerort und Paketgröße kommen vor.

Trace-Methoden stellen eine Alternative zu obigen befehlszentrierten Simulationen. Der Fokus liegt dabei auf Ereignissen, bsp. dem Aufrufen einer Cacheadresse in der Programmausführung und nicht mehr auf der simulierten Ausführung eines Programmes bzw. einer Befehlsfolge. Eine solche Spur kann aber wieder zu einem Befehlssatz bzw. Programm ergänzt werden. Die höhere Abstraktion bedeutet dabei eine Spur, welche eine Rechneroperation über der grundlegenden Maschinenoperation beschreibt. Der Nachteil sind die großen Speicheranforderungen der Traceevents. Auch kann nicht das gesamte Systemverhalten (z.B. spekulative Instruktionen) abgebildet werden.

D&E: Die analytischen Methoden sind viel zu unscharf?

AP: Dafür taugen Sie aber zur heuristischen Erkundung großer Designräume! - Die Details könnten Sie ja dann in einer Simulation studieren. Analytische Modelle arbeiten meisten intrinsisch oder empirisch, manchmal in einer Kombination aus beiden.

Ein intrinsisches Mikroprozessormodell beinhaltet das Komponentenverhalten explizit, das empirische kennt statistisches Verhalten das in Regressionsmodell oder neuronalem Netz hinterlegt ist. Ein empirisches Modell zu trainieren fällt dabei meistens leichter als mit einem intrinsischen Modell zu arbeiten.

- Abstraktion als Explorationskatalysator

- Konkrete Evaluation

- Abdeckung des Designraumes

- Echte Arbeitslast