Meßtechnik

Embedded Designs optimal mit dem MSO testen

Fortsetzung des Artikels von Teil 1

Parallele Datenbusse analysieren

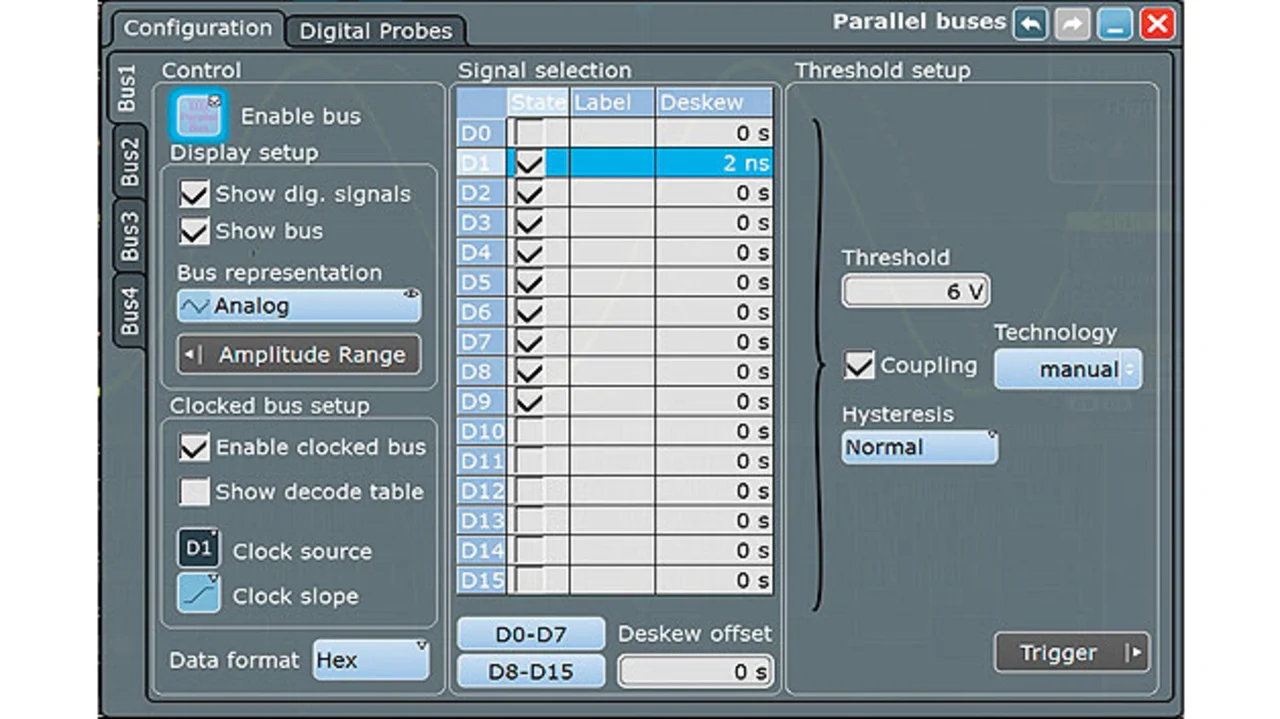

Die zeitlich korrelierte Darstellung analoger Messkurven mit digitalen Signalen ist mit integrierter Logikanalyse möglich. Die Mixed-Signal-Option des R&S RTE erweitert das Oszilloskop zu einem praxisgerecht bedienbaren MSO mit 16 digitalen Kanälen. Im vorliegenden Fall belegt der Ausgang des A/D-Wandlers neun Leitungen, nämlich mit seinen acht Datenbits und mit dem Taktsignal. Der logische Zustand des Busses wird zu den Zeitpunkten gültiger Taktflanken bestimmt. Der Anwender konfiguriert den Bus entsprechend der realen Bustopologie. Er definiert, welche digitalen Kanäle Bestandteil des Busses sind und wo der Pegel der Entscheidungsschwelle zur Binarisierung liegt. Mit dem hier zur Analyse genutzten Oszilloskop ist übrigens die Decodierung von vier parallelen oder seriellen Bussen gleichzeitig möglich: Jeder Bus wird durch ein Signal-Icon am Bildschirmrand repräsentiert. Unabhängig von den übrigen Einstellungen des Oszilloskops zeigt das Icon den aktuellen Status aller aktivierten Logikkanäle (High, Low, Toggle) an, wodurch der Anwender einen schnellen Überblick über die Busaktivität bekommt.

Jobangebote+ passend zum Thema

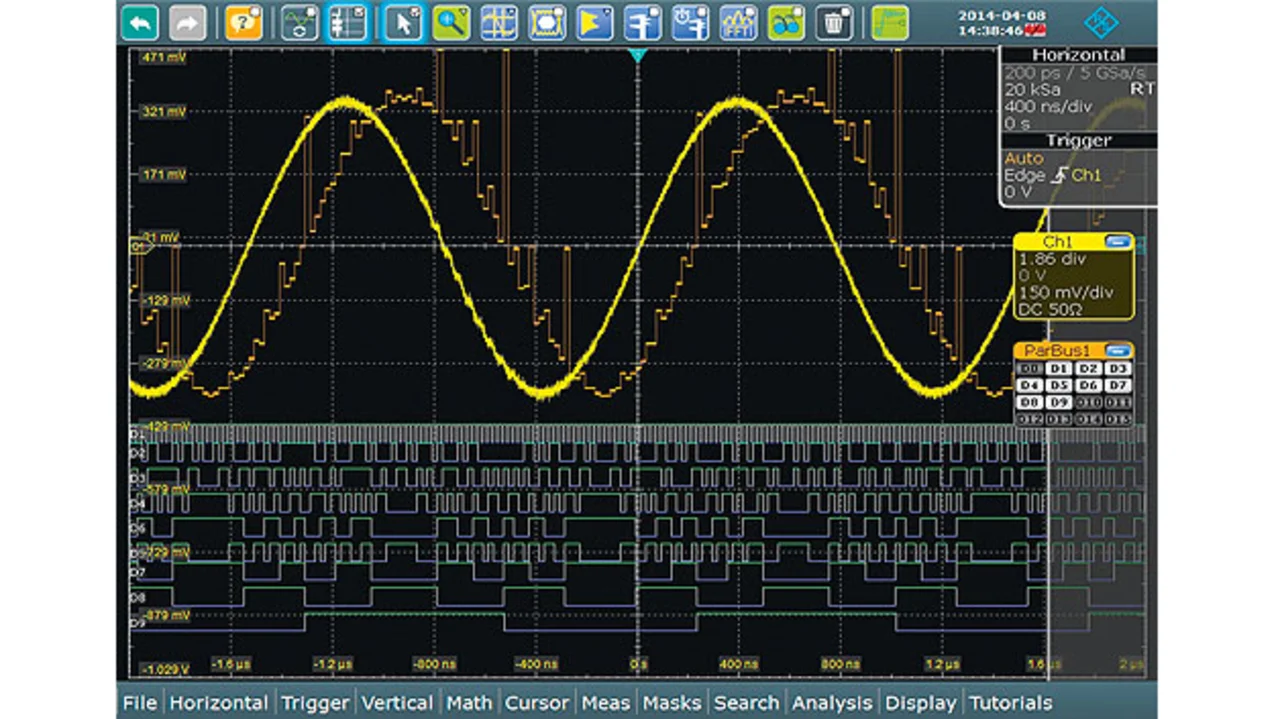

Das gilt auch für die Kanäle, die nicht im Diagramm angezeigt sind. Natürlich ist es möglich, den decodierten Bus im Wabenformat darzustellen. Wie Bild 3 zeigt, eignet sich jedoch die Darstellung als analoge Messkurve speziell für die Analyse eines A/D-Wandler-Ausgangs besser. Damit können Anwender das Eingangssignal direkt mit dem Ausgangssignal vergleichen und zum Beispiel den zeitlichen Versatz zwischen den beiden vermessen. Außerdem werden eventuell vorhandene Verzerrungen im Ausgangssignal sichtbar.

Die gehäuft auftretenden Spikes in der analogen Busdarstellung (Bild 3) machen Probleme im Design des Board deutlich erkennbar. Diese schmalen Spikes werden sichtbar dank der hohen Abtastrate von 5 GS/s pro digitalem Kanal, die gleichbedeutend mit einer zeitlichen Auflösung von 200 ps ist. Diese Abtastrate gilt im hier verwendeten MSO über die gesamte Speicherlänge von 100 MS, so dass sich auch Spikes weit entfernt vom Triggerzeitpunkt noch erfassen lassen.

Die Vermutung liegt nahe, dass die Spikes durch Timing-Probleme bedingt sind, die zu einer Verletzung der Setup&Hold-Zeiten führen. (Unter der Set-up-Zeit versteht man die Zeit, die ein Datensignal vor der nächsten Taktflanke anliegen muss, während die Hold-Zeit die Zeit beschreibt, die das Datensignal nach einer Taktflanke konstant bleiben muss, um Gültigkeit zu erlangen.

Zum Test, ob diese Vermutung richtig ist, genügt es, das Taktsignal im Oszilloskop relativ zu den Datensignalen zeitlich zu verschieben. Moderne Oszilloskope wie das R&S RTE sollten in der Lage sein, jeden digitalen Kanal einzeln gegenüber allen anderen zu verschieben (Bild 4).

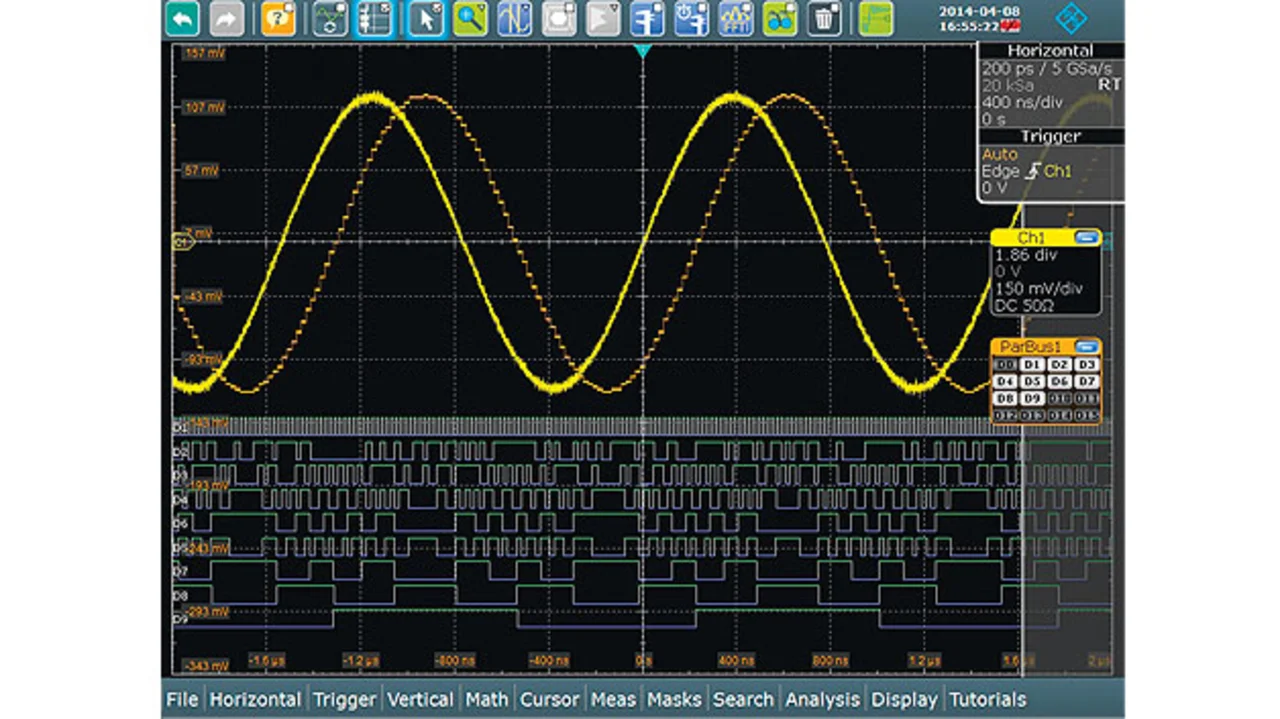

Wie Bild 5 verdeutlicht, reicht im vorliegenden Beispiel ein Versatz von 2 ns, damit die Spikes in der analogen Busrepräsentation verschwinden. Mit dieser Erkenntnis kann der Anwender sein Design überprüfen und gegebenenfalls Änderungen der Signalpfadlängen vornehmen.

- Embedded Designs optimal mit dem MSO testen

- Parallele Datenbusse analysieren

- Serielle Kommunikation testen