Entwicklungsumgebungen

Low-Power-Spezifizierung in IDEs

Fortsetzung des Artikels von Teil 2

Unterstützter Arbeitsfluss

Eine IDE geht über die Visualisierung hinaus; Diese Entwicklungsumgebung unterstützt den Entwickler bei der Codeerstellung. Mit Unterstützung von UPF und CPF ist auch der Syntax implementiert. Bei einem Spezifikationsfehler, z.B. Eingabe von “create_power_domains” im UPF-Editor, wird die IDE diesen Fehler sofort melden und die Korrektur “create_power_domain” vorschlagen.

Eine IDE gibt auch Vorschläge; Bei der Eingabe von “create_” wird ein DropDown-Menue alle möglichen Auto-Vervollständigungen zur Auswahl anzeigen. Ein wesentlicher Nachteil ist die Notwendigkeit das neue UPF-Format zu lernen. Mit dem unterstützten Arbeitsfluss innerhalb der IDE kann diese Last reduziert werden.

Dabei hilft auch das Erzeugen einer Vorlage für ein eingegebenes Kommando, die anzeigt, welche Felder der Anwender zu füllen hat. Für jedes Feld sind dabei wieder Auto-Vervollständigung und Fehleranzeige verfügbar. Das verkürzt die Erstellungszeit einer Leistungsspezifikation erheblich.

Jobangebote+ passend zum Thema

Konsistenzcheck

In SoC-Projekten fällt es schwierig viele Design- und Verifikationsdateien miteinander synchron zu halten. So sind SystemVerilog-Assertions (SVA) populärer als der Property-Specification-Language-Standard (PSL), da die Behauptungen direkt im Design- und Verifikationscode hinterlegt sind. Mit Suchen-und-Ersetzen zur Änderung einer Bezeichnung werden ebenso die Behauptungen und andere Referenzen erfasst.

Obgleich die Leistungsspezifikation in einer separaten Datei hinterlegt wird, kann die IDE die Lücke zwischen diesen und weiteren Datein schließen, sofern die gleichen Designnamen verwendet werden. Da mit jeder Änderung neu-kompiliert wird, erfolgen im selben Schritt auch Konsistenzchecks zu Änderungen in den UPF-/CPF- oder RTL-Dateien.

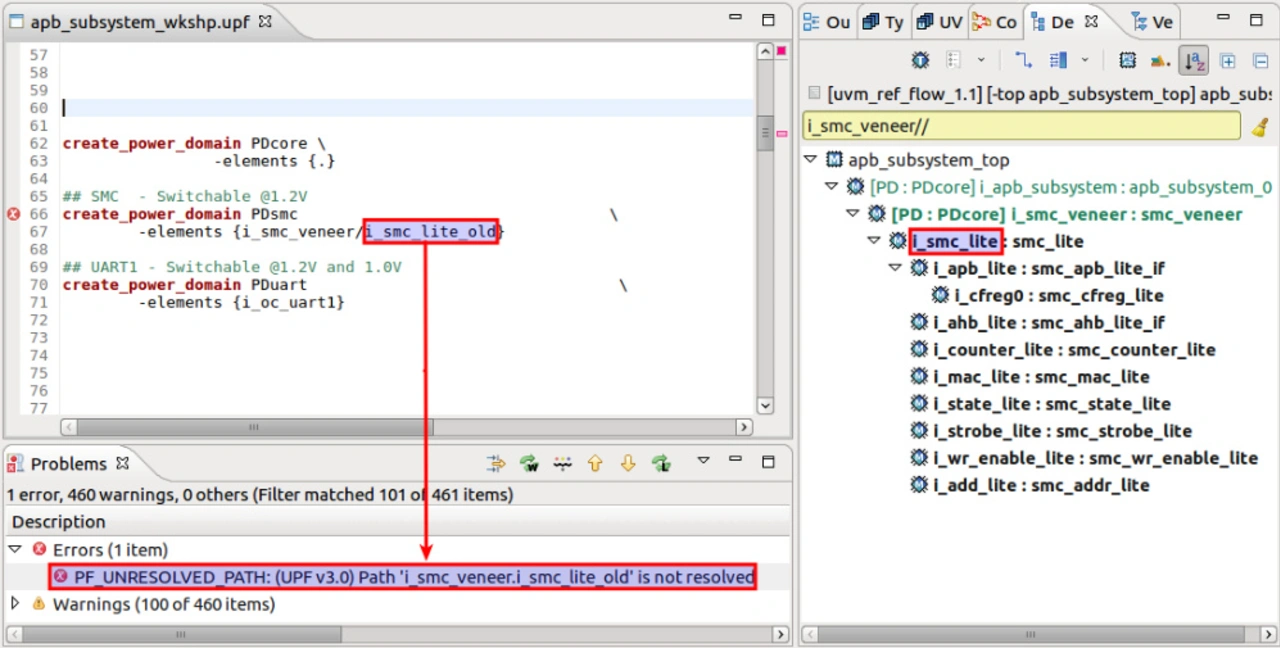

Bild 2 zeigt so einen Check. Im RTL wurde “i_smc_lite_old” zu “i_smc_lite” geändert, die UPF-Namen aber beibehalten. Die IDE erkennt diese Inkonsistenz und gibt eine Warnung.

Fazit

Viele Faktoren werden bei modernen SoCs im LowPower-Design erwogen. Unter den vielen vorhandenen Techniken zur Minimierung des Leistungsumsatzes bietet die Möglichkeit einzelne Leistungsbereiche auf dem Chip zu steuern hohe Flexibilität im Hard- wie Softwaredesign. Diese Leistungsbereiche und ihre Eigenschaften müssen in einer Spezifikation definiert werden. Eine IDE für Design&Verifikation sollte diese Spezifikationsformate unterstützen und die Konsistenz zwischen allen Dateien im Entwicklungsfluss gewährleisten. Damit gelingt eine schnellere Einbindung, einfachere Spezifizierung und ein robuster Zugang zum Low-Power-Design.

- Low-Power-Spezifizierung in IDEs

- Leistungsspezifikation

- Unterstützter Arbeitsfluss