ISSCC 2018

Prozessor-Legende und RISC-V-Erfinder stellt Google-TPU vor

Fortsetzung des Artikels von Teil 1

Googles TPU schlägt CPU und GPU

Die Idee von CPU-Designern bestand lange Zeit darin, für den Entwickler unsichtbar eine Parallelisierung auf Befehls-Ebene im Backend bei den Instruktions-Einheiten zu realisieren, z.B. durch Out-of-Order-Befehlsausführung. Nachdem man hier nicht mehr wirklich weiterkam, folgte 2004 der erste Multicore-Prozessor.

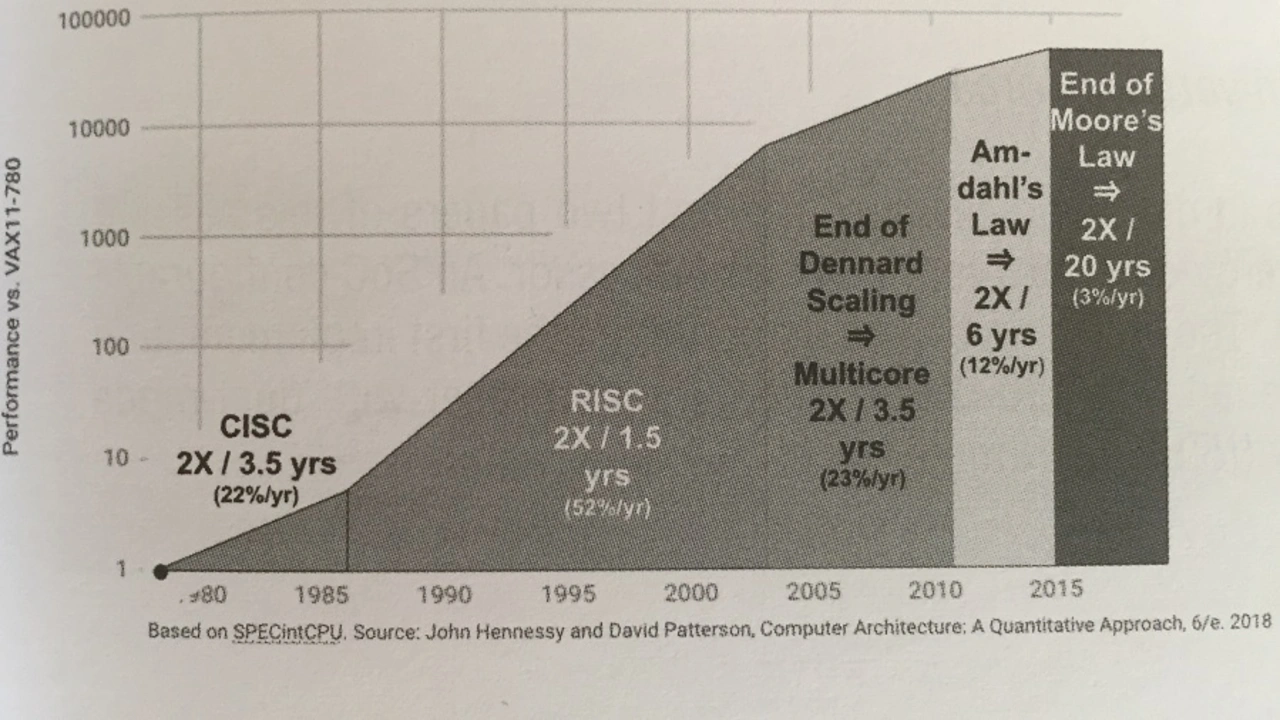

Wie Gene Amdahl 1967 nachwies, kann man jedoch nur bedingt von der Skalierung über mehrere Cores profitieren, Enthält ein Programm 1/8 sequentiellen Code, kann man maximal um Faktor 8 beschleunigen, selbst wenn man 100 Cores einsetzt. Wie in Bild 1 ersichtlich ist, trägt dies sogenannte Amdahlsche Gesetz dazu bei, dass sich die Rechenleistung, wenn sich der Trend so fortsetzt, in den nächsten 20 Jahren nicht verdoppeln wird.

Die anderen beiden limitierenden Faktoren sind das absehbare Ende des mooreschen Gesetzes und die steigende Leistungsaufnahme pro mm2 Chipfläche, was dank thermischer und mechanischer Limitierungen, einem gewissen Power-Budget pro Chip sowie EMV-Überlegungen der Fall ist.

Laut Prof. Patterson gibt es nur eine Lösung für diese Dilemma: Sogenannte domänenspezifische Architekturen (DSA).

Jobangebote+ passend zum Thema

Eine Beispiel-DSA: Googles TPU

Ein Beispiel ist die 2015 vorgestellte sogenannte Tensor-Processing-Einheit (TPU) von Google für neuronale Netzwerk-Anwendungen. Sie arbeitet entsprechende Algorithmen 15 bis 30x schneller als CPU/GPU ab und ist dabei 30-80x energieeffizienter in derselben Chip-Fertigungstechnologie.

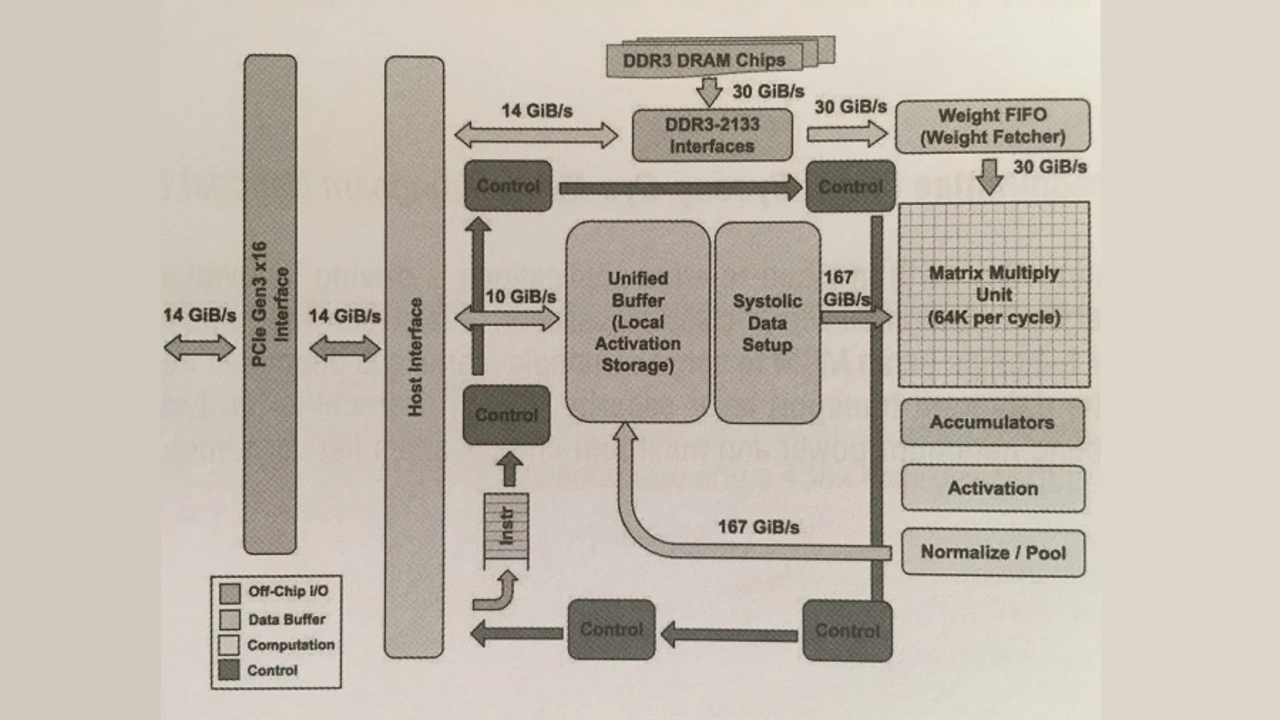

Bild 2 zeigt das Blockdiagramm. Ein Host sendet Befehle über den PCI-Bus in den Befehlspuffer. Die internen Blöcke sind über 256 bit breite Datenpfade verbunden. Herzstück der TPU ist die Matrizen-Multiplikations-Einheit, die 256x256 MACs beinhaltet, die jeweils 8-bit-Integer-Zahlen multiplizieren und addieren können. Die 16-bit-Produkte werden dann von 4096 32-bit-Addierern für jeweils 256 Elemente zusammengefasst. Die Matrizen-Einheit liefert pro Taktzyklus eine Teilsumme bestehend aus 256 Elementen.

Da das Lernen in neuronalen Netzen in den Gewichten stattfindet und diese das gelernte Wissen des Netzes speichern, werden die Netzgewichte als Matrix dargestellt. Die Gewichte für die Matrizen-Einheit werden über eine On-Chip-Gewichts-FIFO festgelegt, welche von einem Off-Chip-DRAM-Speicher gefüttert wird.

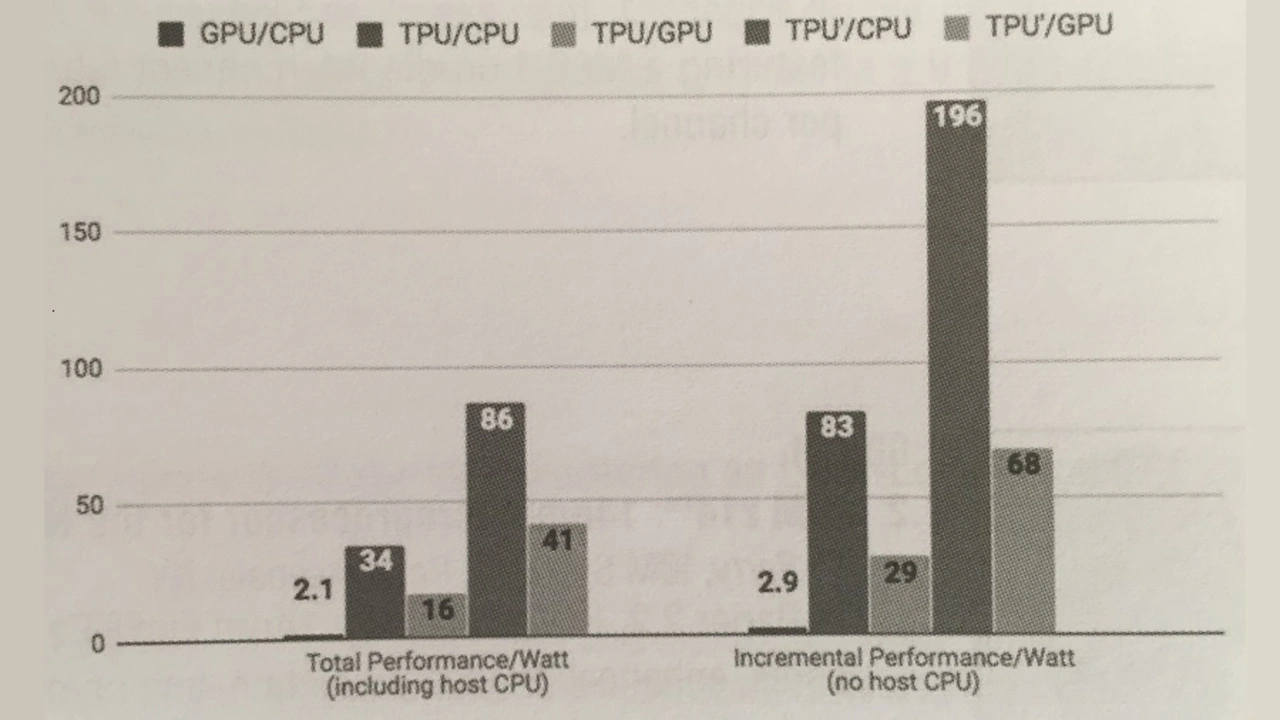

Im Folgenden wird die TPU mit einer Intel-Haswell-CPU (18 Cores, 662 mm2 Chipfläche) und einer GPU des Typs Nvidia Kepler K80 (561 mm2 Chipfläche) verglichen. Obwohl Chipfläche und Leistungsaufnahme nur rund halb so groß sind, liefert sie 100x mehr MACs als die CPU und 25x mehr MACs als die GPU.Bei einer Taktfrequenz von 700 MHz werden 92 Tera-Operationen pro Sekunde ausgeführt (65526 x 2 x 700 mit 256x256=65536).

Bild 3 zeigt die Rechenleistung/W für GPU vs. CPU, TPU vs. CPU und TPU vs. GPU. Die Energieeffizienz, die direkt zu den Kosten eines Rechenzentrum korreliert, ist damit bei der TPU 83 mal höher als bei der CPU und 29 mal höher als bei der GPU. Würde man eine hypothetische TPU mit GDDR5-Speicher annehmen, würden die Werte sogar auf Faktor 196 bzw. 68 ansteigen. Selbst gegenüber einer kombinierten CPU/GPU-Architektur hat die TPU noch einen Vorteil um Faktor 2.9.

Seit 2015 wird die TPU erfolgreich bei Google eingesetzt.Der zweidimensionale Ansatz passt zu den Workloads neuronaler Netzwerk-Anwendungen besser als der eindimensionale Ansatz, den CPU und GPU verfolgen.

- Prozessor-Legende und RISC-V-Erfinder stellt Google-TPU vor

- Googles TPU schlägt CPU und GPU

- Die Zukunft von RISC-ISAs: RISC-V