Infineons neue Low-Cost-Mikrocontroller

XMC1000: Peripheriewunder mit Cortex-M0

Fortsetzung des Artikels von Teil 7

ARMs kleiner Core: Cortex-M0

Natürlich ist eine 32-bit-ARM-Architektur für jeden 8- und 16-bit-Entwickler attraktiv: Höhere Rechenleistung, ein größerer Speicheradressraum und vor allen Dingen die Aufwärtskompatibilität zur am weitesten verbreiteten 32-bit-Embedded-Prozessorarchitektur. Nichtsdestotrotz muss der Cortex-M0, um diese geringe Größe zu erreichen, auch Kompromisse eingehen: Er kann keine ARM-32-bit-Software ausführen, da er bis auf wenige Ausnahmen nur 16-bit-Thumb- und Thumb-2-Anweisungen unterstützt.

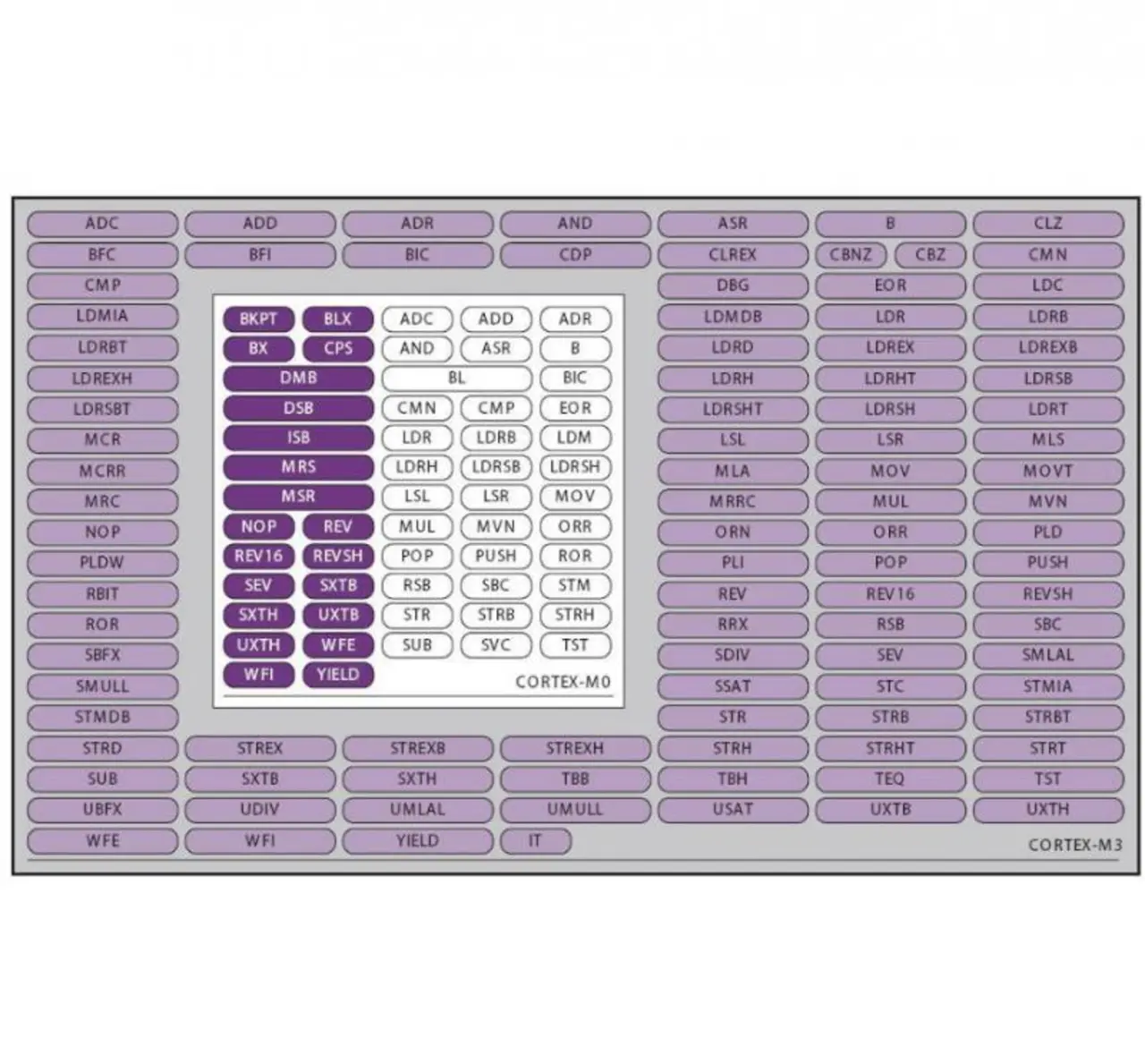

Während Cortex-M3 und -M4 den ARMv7-M-Befehlssatz unterstützen, hat der M0 nur eine ARMv6-M genannte Teilmenge. Diese unterstützt, um Speicher zu sparen, nur Thumb- und Thumb-2-Befehle und einige wenige 32-bit-Befehle primär zur Interrupt-Verarbeitung. Daher ist der M0-Code aufwärtskompatibel zum M3/M4 (Bild 8), aber nicht umgedreht. Bei einer Software-Entwicklung in C reicht allerdings eine Recompilierung des M3/M4-Codes, um auf dem M0 zu laufen.

Der Cortex-M0 hat eine dreistufige Pipeline ohne leistungssteigernde Merkmale wie Sprungvorhersage oder superskalare Befehlsausführung. Um ein deterministisches Verhalten in Echtzeit-Systemen garantieren zu können, hat er keinen Cache, sondern greift auf Code und Daten im Hauptspeicher zu.

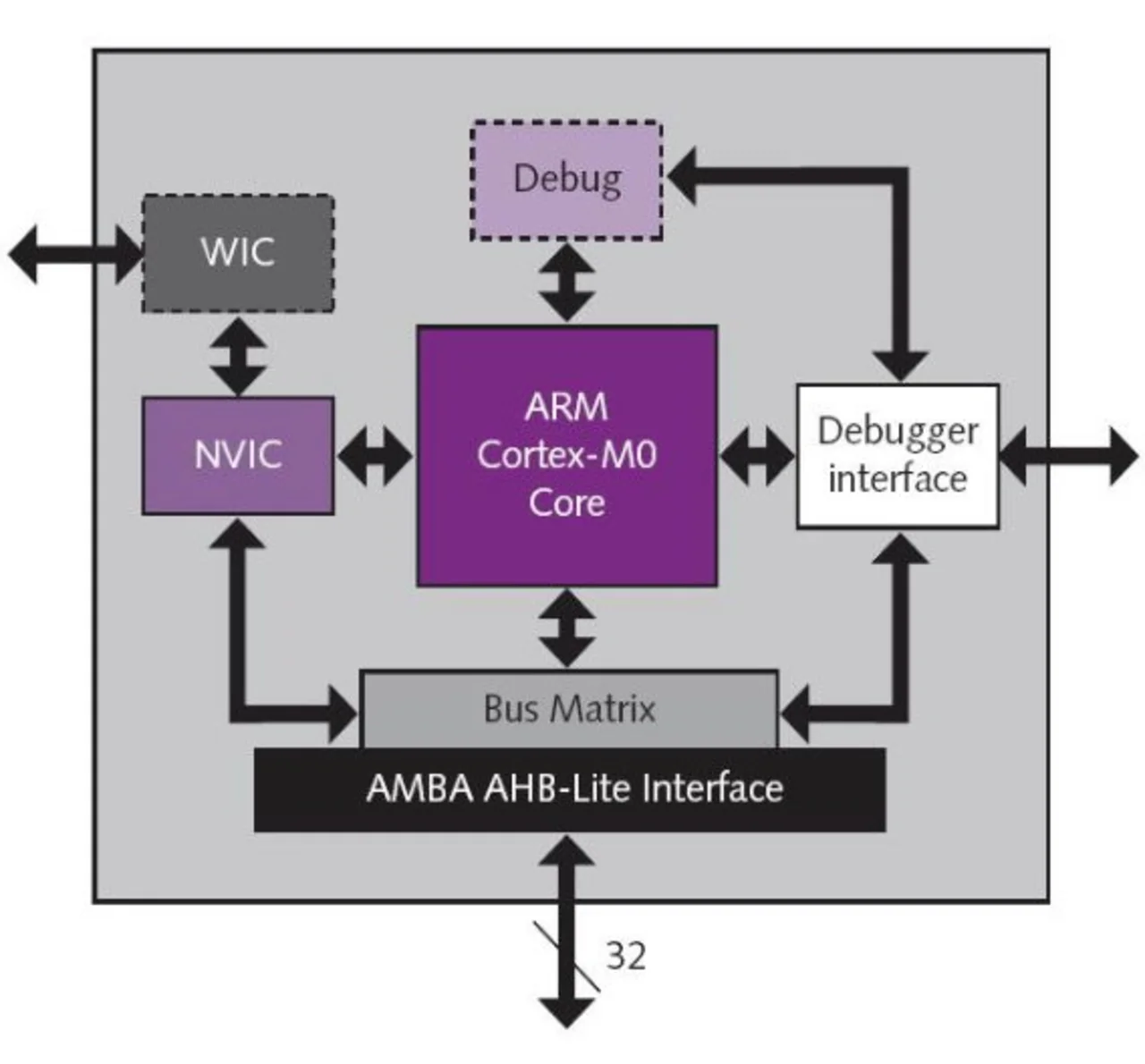

Er beinhaltet eine Von-Neumann-Architektur (einheitlicher I/O-Bus für Daten und Befehle) und unterstützt kein TCM. Er holt Daten und Anweisungen direkt über eine einzige AMBA-AHB-Lite-32-bit-Schnittstelle (Cortex-M3 und -M4 haben zwei AHB-Lite-Schnittstellen).

Der Befehlssatz besteht lediglich aus 56 Anweisungen (die Hälfte eines 8051), die bis auf sechs alle 16 bit breit sind (Bild 8). Es handelt sich um 35 Thumb-Anweisungen vom ARM7TDMI zuzüglich 21 Thumb-2-Anweisungen, die 2004 mit dem ARMv7-M-Befehlssatz eingeführt wurden. Der Cortex-M3 hat diese 56 zuzüglich 99 weiterer Anweisungen, der M4 80 weitere Befehle für digitale Signalverarbeitung und 29 für die Gleitkommaverarbeitung, wenn die optionale FPU implementiert ist.

Jobangebote+ passend zum Thema

Um noch mehr Gatter einzusparen, hat ARM kräftig abgespeckt: Weder gibt es einen 32-bit-Dividierer noch eine Speicherschutzeinheit (MPU) oder die integrierte Echtzeit-Trace-Logik. Der 32-bit-Multiplizierer benötigt in der Basis-Variante 32 Taktzyklen, der optional erhältliche und im XMC1000 implementierte 1-Zyklus-Multiplizierer kostet zusätzlich 3.000 Gatter.

Keine Kompromisse machte ARM bei der Interrupt-Verarbeitung. Diese ist für viele Embedded-Systeme lebenswichtig und eine Schwäche der alten ARM7TDMI-S-Architektur. Diese benötigte einen externen Interrupt-Controller und antwortet vergleichsweise langsam auf Interrupts. Ebenso fehlt ein nicht maskierbarer Interrupt (NMI).

Der in der Cortex-Familie implementierte konfigurierbare Nested-Interrupt-Controller (NVIC) ist eng mit dem Core verbunden und unterstützt beim M0 bis zu 32 Interrupts in vier Ebenen, NMIs und weist zudem erheblich kürzere Interrupt-Latenzen auf. Beim Cortex-M0 beinhalten die 16 Taktzyklen die Prioritätserkennung, die Verschachtelung, die Sicherung der Register auf dem Stack, die Verzweigung in die Interrupt-Routine und den Beginn der Ausführung der ersten Anweisung in der Interrupt-Routine. Der Cortex-NVIC führt alle diese Operationen in Hardware aus.

Die 12.000-Gatter-Basis enthält einen NVIC mit einem Interrupt, den 32-Zyklen-Multiplizierer und den AHB-Lite-Bus. Im „Vollausbau“ nimmt der Core 27.000 Gatter in Anspruch. Im XMC1000 findet sich eine Konfiguration mit 26.500 Gattern; lediglich auf den Wake-up-Interrupt-Controller (WIC), der primär bei Low-Power-Standby-Applikationen Sinn macht, hat Infineon verzichtet (Bild 9) und die Aufweck-Funktionen über den NVIC implementiert.

- XMC1000: Peripheriewunder mit Cortex-M0

- Hochstrom-Digital-I/O-Pins und AES-Engine

- Software-Entwicklung mit Code-Generator

- Innovative Peripherie im Cortex-M0-Universum

- Fünf virtuelle A/D-Wandler

- Lighting für Fortgeschrittene

- Fazit: Klein, aber mehr als oho

- ARMs kleiner Core: Cortex-M0