Mikrocontroller

Neustart mit RISC-V

Fortsetzung des Artikels von Teil 1

RISC-V Cores

Nachdem die RISC-V ISA gezeigt wurde, sollen zuerst vorhandene RISC-V-Cores kurz vorgestellt werden. Tabelle 7 zeigt eine kleine Auswahl der unter [5] gelisteten Cores. Auffallend ist, dass die verschiedenen Cores mit unterschiedlichen Lizenzen ausgestattet sind. Neben den technischen Merkmalen ist das ein Aspekt, den es gerade in kommerziellen Projekten zu bedenken gilt.

Jobangebote+ passend zum Thema

| Name | Links | User spec | License | Supplier |

|---|---|---|---|---|

| Rocket Core | [7] | 2.3-draft | BSD | SiFive, UCB Bar |

| RI5CY | [8] | RV32IMC | Solderpad Hardware License v. 0.51 | ETH Zurich, Università di Bologna |

| SweRV EH1 | [9] | RV32IMC | Apache 2.0 | Western Digital |

Tabelle 7: Auswahl von RISC-V-Cores.

Der Link beim Rocket Core verweist auf den Rocket-Core-Generator, einem Open-Source-SoC-Designgenerator [10]. Der Rocket-Chip-Generator erzeugt General-Purpose-Processor-Cores, die die RISC-V ISA implementieren.

RI5CY ist ein kleiner RISC-V-Core, der das RV32IMFC-Instruction-Set und zahlreiche kundenspezifische Extensions für Signalverarbeitung implementiert. RI5CY wurde als Teil der PULP-Plattform für energieeffizientes Computing entwickelt und wird derzeit als Prozessorkern für PULP und PULPino verwendet [11].

SweRV ist eine von Western Digital entwickelte RISC-V Core-Implementierung, die dem Ziel folgt, deren Speicherlösungen von proprietären hin zu Cores mit RISC-V ISA umzustellen. Das Release steht auf WDs GitHub-Repository zur Verfügung [9]. Es enthält Register-Transfer-Level-Code (RTL) im Verilog-Format für den Kern sowie eine Kurzanleitung zum Konfigurieren und Erstellen eines Modells in Verilator-, Synopsys- und Cadence-Targets.

Kundenspezifische RISC-V-Cores lassen sich nach folgendem Muster entwickeln: Auswahl einer ISA, Auswahl eines Herstellers oder Eigenentwicklung des betreffenden Cores, Hinzufügen eigener Extensions. SiFive bietet hierzu die folgende Vorgehensweise an:

- Auswahl und Anpassung eines SiFive- Standard-Cores an die genauen Anforderungen.

- Simulation mit voll funktionsfähigem, synthetisierbarem Verilog RTL. Ausführen der Anwendung auf einem FPGA.

- Lizenzierung und Lieferung der benutzerdefinierten RISC-V-Core-IP innerhalb weniger Wochen.

| Core Serie | E2 | E3 | E7 | S2 | S5 | S7 | U5 | U7 |

|---|---|---|---|---|---|---|---|---|

| Compatibel zu ARM Cortex- | M0, M0+, M3, M4, M23, M33 | R4, R5 | M7, R7, R8 | R4, R5 | M7, R7, R8 | A5, A7, A35, A53 | A55 |

Tabelle 8: SiFive Standard-Cores.

SiFive bietet die in Tabelle 8 aufgelisteten Standard-Cores zur Auswahl und Anpassung an. Im Ergebnis des SiFive Core Designs kann so z. B. auf Basis der E2-Serie ein RISC-V-Mikrocontroller entworfen werden. Nach dem Review kann der Build Prozess angestoßen werden und das im Ergebnis bereitgestellte SiFive-Core-IP-FPGA-Eval-Kit enthält alles, was zur Programmierung eines Xilinx-Arty-A7-Artix-7-FPGA-Evaluation-Kits an Informationen notwendig ist.

RISC-V-SoCs und Development-Kits

Nach all den Betrachtungen bleibt festzuhalten, dass RISC-V nur den Core darstellt, der in einem Gesamtsystem arbeitet [13]. RISC-V beschreibt eine offene ISA:

- RISC-V-Implementierungen können sowohl Open- als auch Closed-Source sein,

- Es gibt zahlreiche Implementierungsoptionen (Extensions),

- Implementierungen können in unterschiedlichen Sprachen (Chisel/VHDL/Verilog) erfolgen,

- Implementierungen können auf verschiedenen Targets (FPGA/ASIC) erfolgen.

Ein Gesamtsystem entsteht erst durch eine um Peripheriekomponenten erweiterte RISC-V-Plattform (Cores, Interconnections, Accelerators). Tabelle 9 listet SoCs, die verfügbar sind und mindestens einen RISC-V-Core (keine FPGAs) aufweisen [5]. Ich habe hier einige davon markiert, zu denen es Development-Kits gibt, mit denen man erste Schritte aus Anwendersicht gehen kann.

| Name | Lieferant | Core | ISA | Devkit | Availability |

|---|---|---|---|---|---|

| FE310-G000 | SiFive | E31 | RV32IMAC | HiFive1 | public since 2016Q4 |

| FE310-G002 | SiFive | E31 | RV32IMAC | HiFive1 Rev B | public since 2019Q2 |

| Freedom U540 | SiFive | U54 (4 cores), E51 (1 management core) | RV64GC (application cores), RV64IMAC (management core) | HiFive Unleashed development board | public since 2018Q1 |

| GAP8 | GreenWaves Technologies | PULP / 1 + 8 RI5CY | RV32IMC (+ Priviledged and custom ISA extensions) | GAPuino development board | public since 2018Q1 |

| K210 | Kendryte | K210 | RV64GC | KD233 development board, Sipeed MAiX/M1 development board | spublic since 2018Q4 |

| RV32M1 | NXP | RI5CY + Zero RI5CY + Arm Cortex M4F + Arm Cortex M0+ | RV32IMC | VEGAboard | available for preorder as of 2018Q4 |

| RavenRV32 | efabless | PicoRV32 | RV32IMAC | RavenRV32 DevKit | Limited Quantity |

| GD32VF103 | GigaDevice | Bumble-bee Core | RV32IMAC | GD32VF103V-EVAL, Longan Nano etc. | available |

Tabelle 9: RISC-V-SoCs, Stand: 02.12.2019.

Nicht jeder potentielle RISC-V-Anwender wird sich seinen eigenen RISC-V-Prozessor bauen, sondern andere Vorteile dieser Technologie nutzen wollen. RISC-V-Development-Kits sind deshalb nicht nur für RISC-V-Core-Entwickler zum Test ihrer Designs sondern vor allem für diejenigen von großer Bedeutung, die sich von der Anwendungsseite dem Thema RISC-V nähern wollen. Ich habe hier drei solcher Boards herausgegriffen, die auch verfügbar sind und kurz vorgestellt werden sollen.

Von SiFive wurde bereits 2016 das FE310-SoC angeboten und im HiFive1-Development-Board eingesetzt. Aktuell liegt mit dem FE310-G002 ein Upgrade dieses SoCs vor, welches das bestehende Design um die RISC-V-Debug-Spec 0.13, Hardware-I2C, zwei UARTs und Low-Power-Sleep-Modes ergänzt.

Die Basis für das FE310-G002-SoC ist ein E31-CPU-Core, der einen RV32IMAC mit 16 KByte L1-Instruction-Cache, 16 KByte Data-SRAM sowie Hardware-Multiplikation/Division implementiert.

Das HiFive1-Development-Board wurde daraufhin ebenfalls einem Update unterzogen. Ein ESP32 sorgt für WiFi/Bluetooth-Connectivity und der USB-Debugger wurde nun auf einen Segger-J-Link aktualisiert, der Drag&Drop für das Code-Upload unterstützt. Bild 1 zeigt das neue SiFive-HiFive1 Rev. B im Arduino-Uno-Formfaktor.

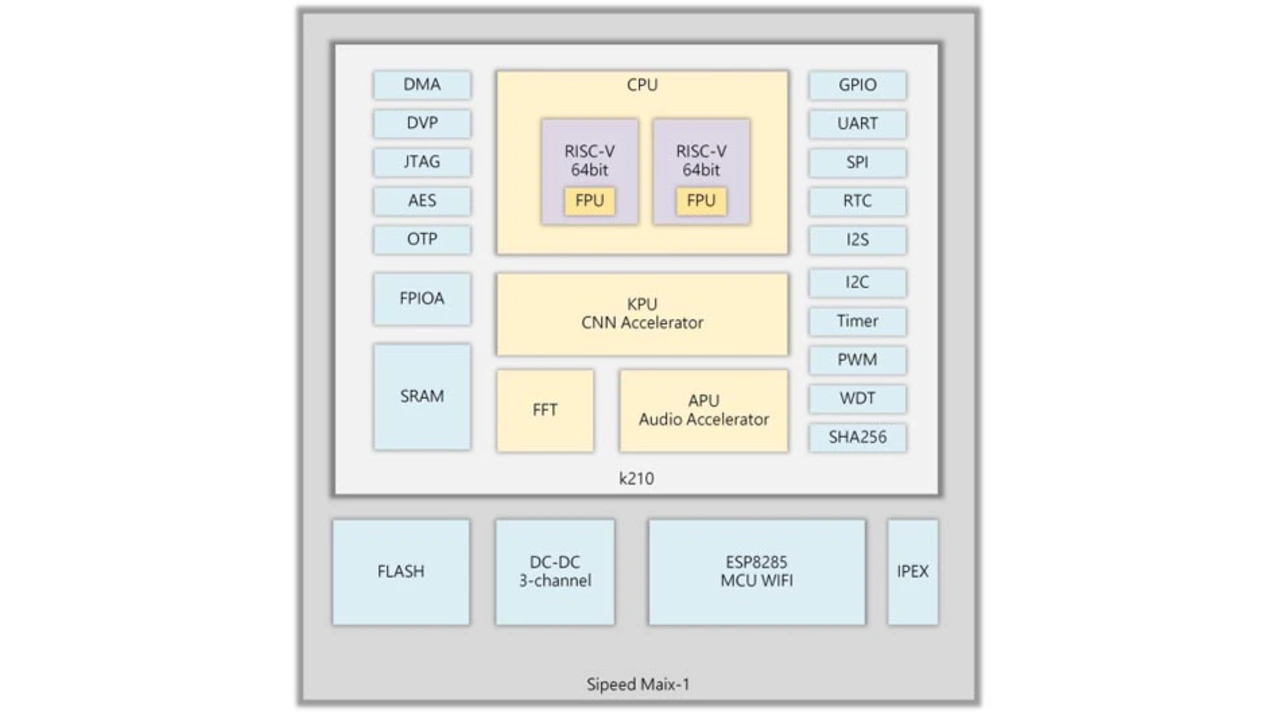

MAIX ist ein von Sipeed entwickeltes Modul, mit dem KI-Aufgaben sensornah ausgeführt werden können. Die MAIX-CPU enthält einen auf dem Rocket-Core basierenden Dual-Core-64-bit RISC-V-Prozessor Kendryte K210 (RV64IMAFDC), der mit bis zu 400 MHz getaktet werden kann und folgende Hardware-Erweiterungen on-board hat:

- KPU CNN Hardware-Beschleuniger,

- APU Audio-Hardware-Beschleuniger unterstützt bis zu 8 Mikrofone und eine Abtastrate bis zu 192 kHz,

- FPIOA (Field Programmable IO Array) mapping von 255 IO-Funktionen zu allen 48 GPIOs,

- 8 Mbyte SRAM,

- AXI ROM, um Anwendungsprogramme von SPI-Flash zu laden und

- zahlreiche andere Beschleuniger für AES, SH256 und FFT sowie Peripherals: OTP, UART, WDT, I2C, SPI, I2S, TIMER, RTC, PWM, etc.

Bild 2 zeigt ein Blockdiagram des Moduls Sipeed MAIX M1 mit den genannten Blöcken der MAIX-CPU (Kendryte K210) in der oberen Hälfte und den das Gesamtmodul ausmachenden Zusatzmodulen in der unteren Hälfte. Das MAIX-M1-Modul gibt es mit (M1W) und ohne (M1) WiFi-Zusatz.

Bild 3 zeigt das mit einem MAIX M1W bestückte MAIX Dock, ein Development Board, welches bei einer Größe von nur 5,08 cm × 2,54 cm folgende Funktionen bereitstellt:

- Storage – Micro-SD Card Steckplatz, 8 MByte SPI-Flash,

- Display I/F – MCU LCD FPC Connector für optionales 2,4" LCD (ILI9341 Controller),

- Camera I/F – DVP Camera FPC Connector (OV2640),

- USB – 1× USB Type-C Port zu Spannungsversorgung und Programmierung,

- Expansion – Stiftleisten für UART, I2C, SPI, I2S, PWM, etc.,

- Misc – 2× Taster, 1× RGB LED und

- Power-Supply – Via USB Type-C Port.

Vom Hersteller werden die folgenden Performance-Daten angegeben: 0,25 TOPS @ 0,3 W, 400 MHz.

uch bei Sipeed ist man sich bewusst, dass die Verbindung mit Peripherals über bekannte Schnittstellen sehr hilfreich ist. Das kürzlich vorgestellte Grove AI HAT mit Raspberry-Pi-kompatibler Buchsenleiste ist eine weitere Option. Die Programmierung der MAIX-Module kann über das Original-Standalone-FreeRTOS-SDK mit C/C++ erfolgen. Ein MicroPython-Port ist ebenfalls vorhanden (https://github.com/sipeed/MaixPy), wodurch die Evaluation dieses Boards sehr vereinfacht wird.

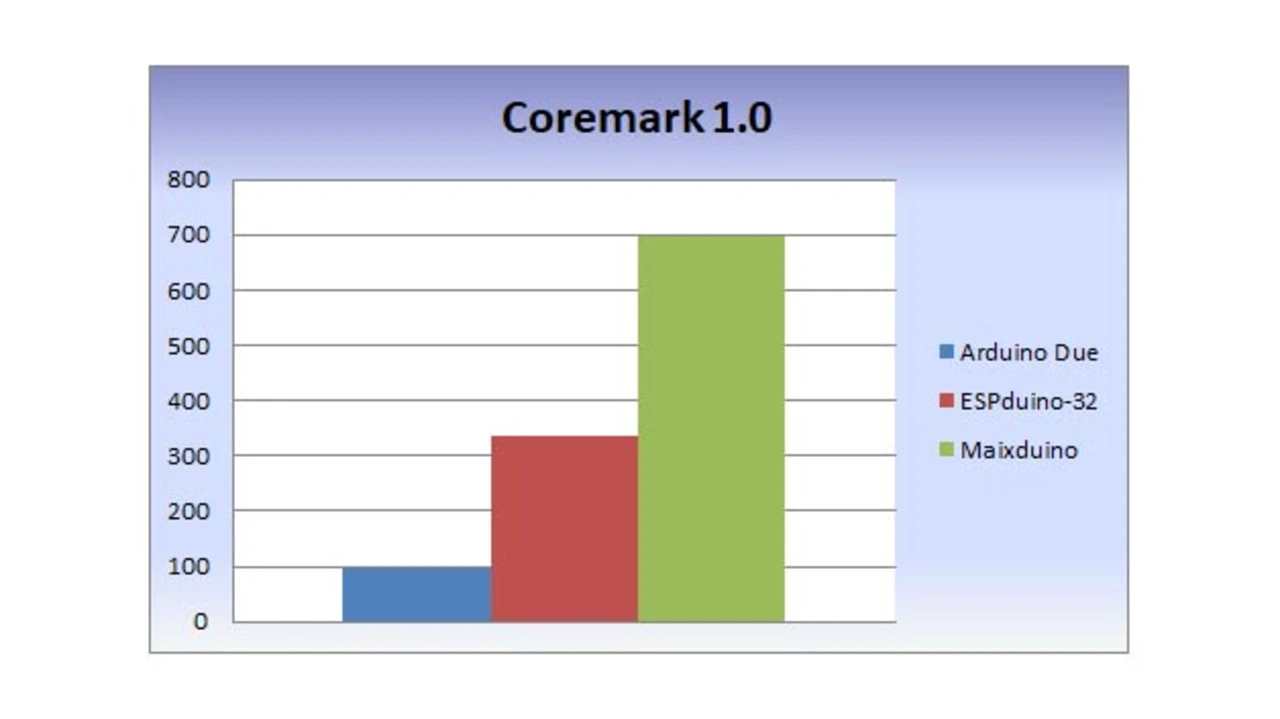

Um die Performance des MAIX M1 gegenüber anderen Arduino-Mikrocontrollern zu bewerten, habe ich zwei Benchmarks laufen lassen [23]: das Sieb des Eratostenes und CoreMark, ein vom EEMBC empfohlener Test, der zudem an die Arduino-Umgebung angepasst ist. Der Vergleich mit dem Arduino Due zeigt, dass schon der ESP32 eine deutliche Verbesserung bringt, die vom MAIX M1 nochmal wesentlich überboten wird (Bild 4).

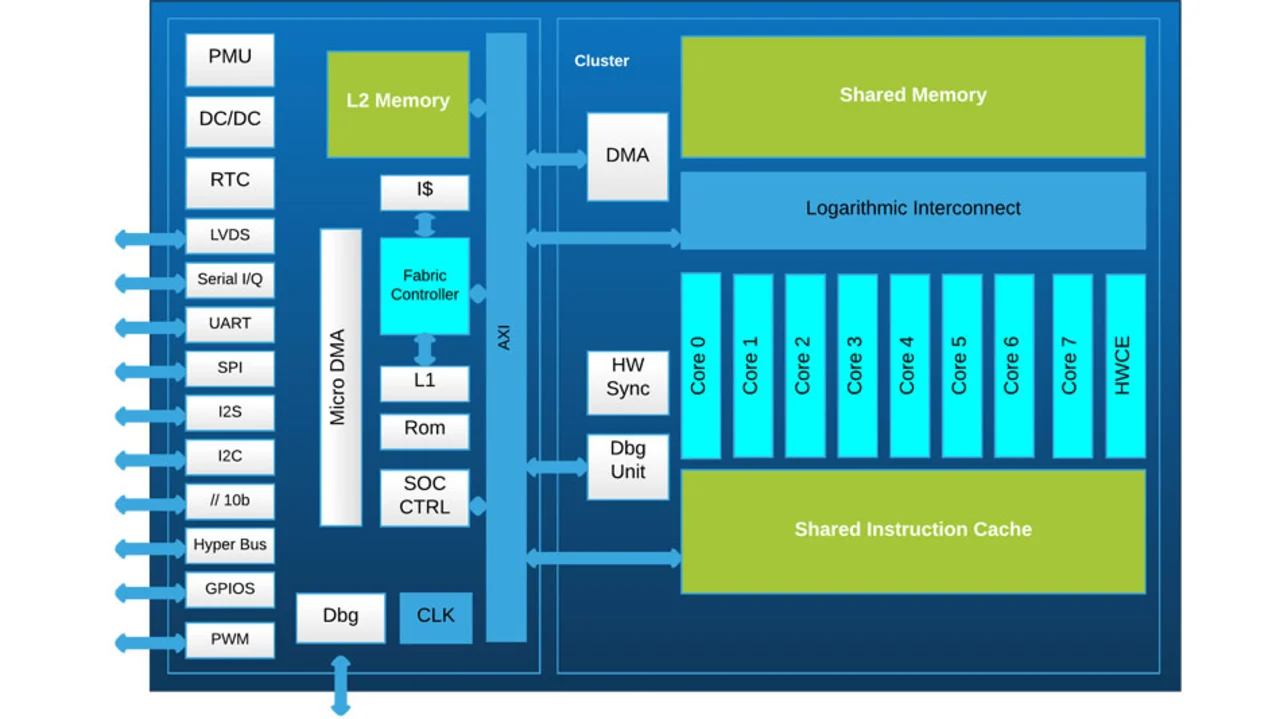

Wie schon das HiFive1-Board von Sipeed ist GAPuino von Greenwaves Technologies ein Development-Board im Arduino-Uno-Formfaktor. GAPuino enthält einen GAP8 und zahlreiche Peripherals. Folgende Merkmale kennzeichnen das Board:

- Anschluss für externe Kamera (z. B. Himax HM01B0),

- HyperBus combo DRAM/Flash 512 Mbits Flash + 64 Mbits DRAM,

- USB to GAP8 JTAG + UART,

- Reset-Taster,

- konfigurierbare I/O-Spannung (3,3V/5V) und

- Stromversorgung über DC-Connector oder USB.

Ein Blockdiagramm des GAP8-SoC zeigt Bild 5. Alle neun Cores in Bild 5 weisen die gleiche ISA-RV32IMC und Teile des Supervisor-ISA-Subsets auf. Diese Standard-Extensions werden durch spezifische Instruktionen ergänzt, die der Performance-Optimierung beim Signal-Processing und Machine-Learning u. a. m. dienen. Weitere Details sind im GAP8-Hardware-Reference-Manual [15] zu finden.

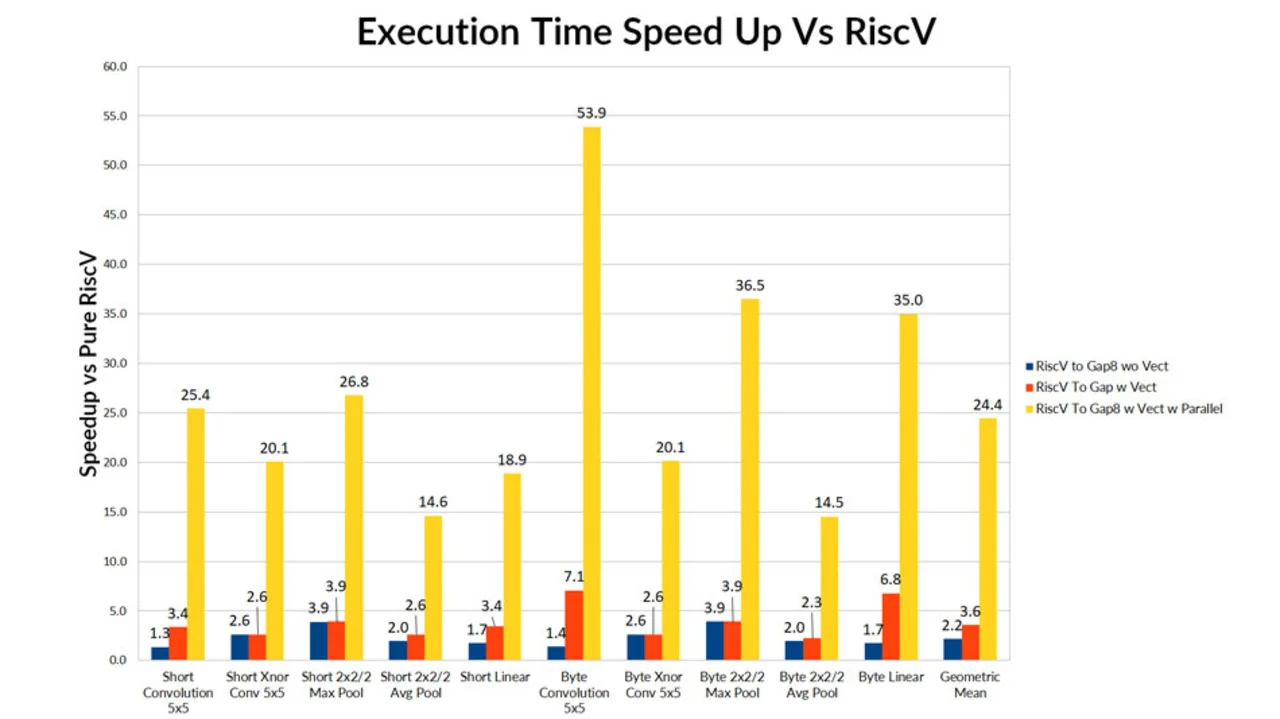

Mit dem GAP8-SDK können GAP8-Anwendungen compiliert und ausgeführt werden. Auf Github enthaltene Benchmarks dokumentieren die Leistungsfähigkeit dieser GAP8-Implementierung [16]. Aus Bild 6 wird sichtbar, dass GAP8 von allen drei Optimierungsstufen profitiert. Der Performance-Gewinn durch die GAP8-ISA-Extensions, Vectorization und Parallelisierung liegt zwischen 14,5 und 53,9. So dauert bei maximaler GAP8-Taktfrequenz ein »5×5 byte convolutional layer on a 112×112 grayscale input image with 100 output filters« auf einem GAP8 12,8 ms, während das auf einem Single-Core-Standard-RISC-V-ISA 729,4 ms dauern würde.

Fazit

RISC-V hat bereits eine eindrückliche Entwicklung genommen und durch die RISC-V Foundation wird sie weiter koordiniert. K. Asanovic dokumentiert in [17] den Stand der RISC-V-Entwicklung und verweist auf die Dinge, die für 2019 vorgesehen waren:

- Core-Standards weitgehend ratifiziert;

- Software-Ecosystem erweitert sich rasch;

- es ist Zeit Plattform-Profile zu standardisieren;

- es liegt viel Arbeit vor uns.

Beim SiFive Technical Workshop in München im Mai 2019 konnte man sich von der durch SiFive gebotenen Unterstützung beim RISC-V-Design sowie von einigen die Entwicklung begleitenden Tools weiterer Anbieter überzeugen. So unterstützt IAR mit der Einführung seiner Entwicklungsumgebung IAR Embedded Workbench für RISC-V die RISC-V-Entwicklung mit einem ersten kommerziellen Tool. Es gibt aber neben Design- und Performance-Aspekten noch weitere, durch die sich RISC-V im Wettbewerb der Technologien behaupten kann. RISC-V ist die perfekte Plattform für lange Produktlebensdauer. Die RISC-V ISA ist stabil und auf Herz und Nieren geprüft. Es bestehen keine Verpflichtungen oder Lizenzvereinbarungen, die eine langfristige Produkt-Road-Map, Entwicklung oder den Technologietransfer verhindern könnten.

Die Hamburger Firma Trinamic entwickelt Motor-Control/Motor-Treiber-SoC mit eingebettetem Mikrocontroller-Kern. Beim Rocinante genannten Treiber wählte Trinamic aus diesen Gründen und der Möglichkeit ihre im FPGA implementierte Logik und den erforderlichen Controller zu kombinieren RISC-V als Grundlage seiner Motion-Control-Elektronik [18]. Anwendungen in der Medizin-, Flug- und Militärtechnik profitieren in gleichem Masse von diesen Aspekten [19]. (jk)

REFERENZEN

[1] Reduced Instruction Set Computer. https://de.wikipedia.org/wiki/Reduced_Instruction_Set_Computer

[2] RISC-V: All Hype or Real Hope for the Processor Market? https://www.allaboutcircuits.com/industry-articles/risc-v-all-hype-or-real-hope-for-the-processor-market/

[3] RISC-V - Members at a Glance. https://riscv.org/members-at-a-glance/

[4] Patterson, W.; Waterman, A.: The RISC-V Reader: An Open Architecture Atlas. Strawberry Canyon, 2017.

[5] RISC-V Cores and SoC Overview. https://github.com/riscv/riscv-cores-list

[6a] The RISC-V Instruction Set Manual. Volume I: User-Level ISA, Document Version 2.2 https://riscv.org/specifications/

[6b] The RISC-V Instruction Set Manual. Volume II: Privileged ArchitecturePrivileged Architecture Version 1.10. https://riscv.org/specifications/privileged-isa/

[7] Rocket Chip Generator. https://github.com/freechipsproject/rocket-chip

[8] RI5CY: RISC-V Core. https://github.com/pulp-platform/riscv

[9] SweRV RISC-V CoreTM from Western Digital. https://github.com/westerndigitalcorporation/swerv_eh1

[10] The Rocket Chip Generator. http://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.pdf

[11] PULP - An Open Parallel Ultra-Low-Power Processing-Platform. http://iis-projects.ee.ethz.ch/index.php/PULP

[12] SiFive Core Design. https://www.sifive.com/core-designer

[13] RISC-V Tutorial - HiPEAC 2019, Valencia. https://pulp-platform.org/docs/hipeac/pulp_intro_kgf.pdf

[14] MicroPython auf RISC-V (Kendryte K210). https://ckmicropython.wordpress.com/2019/03/11/micropython-auf-risc-v-kendryte-k210/

[15] GAP8 Hardware Reference Manual. https://gwt-website-files.s3.amazonaws.com/gap8_datasheet.pdf

[16] GAP8 CNN Benchmarks. https://github.com/GreenWaves-Technologies/benchmarks/tree/master/gap8/cnn

[17] RISC-V – State of the Union. 1st RISC-V Summit, Santa Clara 2018. https://content.riscv.org/wp-content/uploads/2018/12/8.40-Asanovic-RISC-V-State-of-the-Union.pdf

[18] Trinamic introduces world’s first motor driver SoC with integrated RISC-V Core. https://www.trinamic.com/company/news/news-detail/trinamic-introduces-worlds-first-motor-driver-soc-with-integrated-risc-v-core/

[19] Using RISC-V in FPGAs for strategic defense systems. http://mil-embedded.com/articles/using-risc-v-fpgas-strategic-defense-systems/

[20] ARM Architecture Reference Manual - ARMv7-A and ARMv7-R edition. https://silver.arm.com/download/ARM_and_AMBA_Architecture/AR570-DA-70000-r0p0-00rel2/DDI0406C_C_arm_architecture_reference_manual.pdf

[21] Intel® 64 and IA-32 Architectures Software Developer’s Manual. Combined Volumes: 1, 2A, 2B, 2C, 2D, 3A, 3B, 3C, 3D and 4. https://software.intel.com/sites/default/files/managed/39/c5/325462-sdm-vol-1-2abcd-3abcd.pdf

[22] Is x86 RISC or CISC? https://stackoverflow.com/questions/13071221/is-x86-risc-or-cisc

[23] Maixduino – Arduino-kompatibel auf Basis RISC-V. https://ckblog2016.net/2019/08/19/maixduino/

- Neustart mit RISC-V

- RISC-V Cores