ISSCC 2020

Macht Maschinenlernen Chip-Designer arbeitslos?

Fortsetzung des Artikels von Teil 1

ML für das Chip-Design

Aus Deans Sicht gibt es einen Bereich, der in Zukunft besonders von der Nutzung von ML profitieren könnte: Der gesamte Workflow für die Entwicklung eines ASICs. Als Beispiel verweist Dean auf das Place and Route, das große Teams an Designer benötigt, die beim High-Level-Placement anfangen und sich dann iterativ auf die unteren Ebenen vorarbeiten. Bekanntermaßen sind für komplexe ASICs ganze Teams erforderlich, um ein Design zu stemmen. Dean: »Nachdem am Placement viele Leute beteiligt sind, ist es nicht vorstellbar, dass wirklich unterschiedliche Layouts berücksichtigt werden können, ohne dass damit der Zeitplan eines Projekts vollkommen aus dem Ruder läuft.« Hier könnte ML helfen, denn aus Deans Sicht ist Place and Route ein Problem, das sich mit RL-Ansätzen (Reinforcement Learning, verstärkendes Lernen), wie sie erfolgreich bei Alpha Go angewandt wurden, lösen lässt. Dean weiter: »Es ist vielleicht möglich, RL-Algorithmen zu entwickeln, die Place and Route schneller und effektiver durchführen können als bisherige Entwicklungs-Teams.«

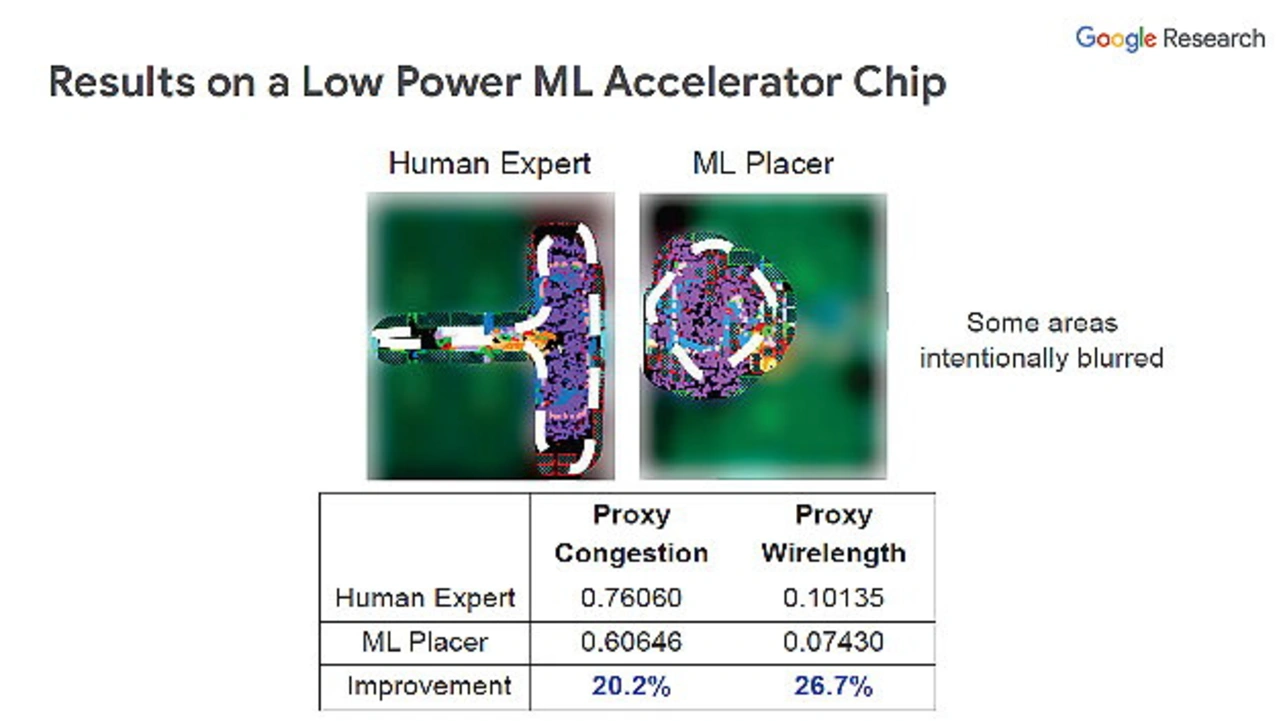

Google hat diese Ansätze selbst schon getestet und laut Dean sind die vorläufigen Ergebnisse durchaus vielversprechend. Google hat bei drei Funktionsblöcken einen ML-Placer laufen lassen und die Ergebnisse mit einem manuellem Placement verglichen: In allen Fällen fiel beim Einsatz des ML-Placers die benötigte Fläche für die Funktion etwas geringer aus. Geht es um den WNS-Wert (Worst Negative Slack) sind die Ergebnisse aber nicht eindeutig. In einem Fall ist der WNS-Wert beim ML-Placer beispielsweise größer als beim manuellen Ansatz, sprich das Layout wurde so realisiert, dass die Signale deutlich mehr Zeit haben, um an den Eingängen der Flip-Flops anzuliegen. Im zweiten Fall fällt der WNS-Wert aber schlechter aus und beim dritten Funktionsblock kommt sowohl der manuelle Ansatz wie auch der ML-Placer auf einen negativen WNS-Wert, sprich in beiden Fällen tritt ein Timing-Problem auf. Ein aber entscheidender Vorteil von ML-Placern ist der Zeitaufwand: Ein ML-Placer brauchte für das Placement eines TPU-Blocks mit Speicher und Logik 24 Stunden, und konnte gleichzeitig ein Layout realisieren, in dem die Verbindungslinien kürzer ausfielen. Der manuelle Ansatz dauerte hingegen sechs bis acht Mann-Wochen. Dean: »ML-basiertes Place and Route hätte viele Vorteile. ASIC-Designer könnten beispielsweise in kurzer Zeit viele Alternativen mit unterschiedlichen Trade-offs hinsichtlich Fläche, Timing etc. realisieren. Außerdem könnte bei großen Änderungen im Design einfach ein neues Layout schnell gemacht werden. Und zu guter Letzt könnten mit ML-Placern der gesamte Aufwand und damit die Kosten für ASICs deutlich sinken.« Aus Deans Sicht könnte ML aber auch für die HL-Synthese oder die Verifikation genutzt werden. Und mit einem ganz weiten Blick in die Zukunft kann sich Dean vorstellen, dass »statt heute für jede Task ein eigenes Modell zu erstellen in Zukunft ein Modell für 1000e oder 1000000e Tasks generiert wird.«

Jobangebote+ passend zum Thema

- Macht Maschinenlernen Chip-Designer arbeitslos?

- ML für das Chip-Design