MCU mit Coprozessor

LPC4300 vereint Cortex-M4- und Cortex-M0-Cores

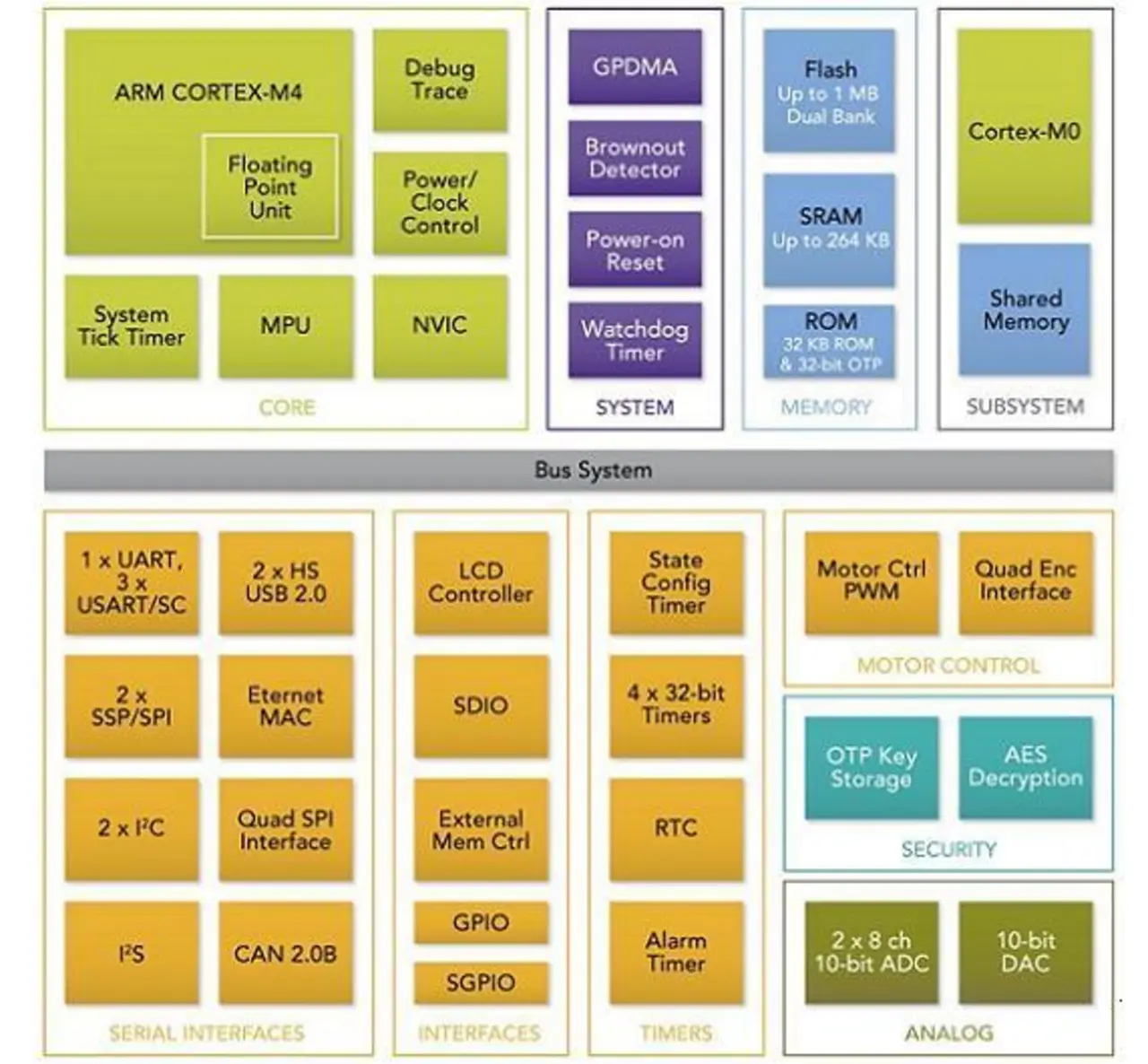

Die Architektur des LPC1800, den NXP im September vorgestellt hatte, deutete bereits darauf hin, dass es bald einen Nachfolger mit dem Cortex-M4-Core geben würde. Jetzt ist es soweit, mit dem LPC4300 hat NXP heute die ersten MCUs mit ARMs Cortex-M4-Core vorgestellt. Dabei gab es eine große Überraschung.

Wie erwartet, handelt es sich bei dem LPC4300 um eine Weiterentwicklung des LPC1800, zu welchem er pin- und peripherie-kompatibel ist, d.h. auf dem LPC4300 finden sich exakt dieselben Peripherie-Blöcke, die auch auf dem LPC1800 angeboten werden. Auch der LPC4300 wird in einem 90 nm-Prozess gefertigt und erreicht durch die schneller schaltenden Transitoren eine Taktfrequenz von 150 MHz.

Besonders interessant ist die Ausführung der MCU als Multi-Prozessor-System mit zwei Cores. Der Cortex-M4 wird durch einen Coprozessor des Typs Cortex-M0 ergänzt, ARMs kleinstem Core, der nur 130µA/MHz aufnimmt. Dieser hat die Aufgabe, den Cortex-M4 besonders bezüglich rechenintensiver DSP-Aufgaben zu entlasten, indem er die Echtzeitsteuerung (Peripheriesteuerung und Protokollemulationen) übernimmt.

Jobangebote+ passend zum Thema

Das Bild zeigt das Blockdiagramm des LPC4300. Die Pheripheriekomponenten können mittels unterschiedlicher Taktquellen individuell getaktet und sogar bei Nicht-Benutzung abgeschaltet werden. Daneben gibt es vier Power-Modi:

- Im Sleep-Modus wird die CPU angehalten, nur die Peripherie wird weiter mit Takt versorgt.

- Im Deep-Sleep-Modus wird die Taktversorgung bis auf den Inetrrupt-Controller abgeschaltet, der Flash-Speicher in einen Standby-Modus überführt.

- Im Power-Down-Modus werden auch Interrupt-Controller und Flash-Speicher abgeschaltet, der Registerstatus wird in speziellen Registern gespeichert.

- Im Deep-Power-Down-Modus wird die interne Spannungsversorgung komplett gekappt, der Systemstatus geht verloren, nur einige Register in der Echtzeituhr bleiben erhalten, damit ein Aufwecken per Echtzeituhr (oder Reset-Pin) möglich ist.

Die Kommunikation zwischen Cortex-M4 und Cortex-M0 wird über einen gemeinsamen Speicher vorgenommen, der Cortex-M0 hat desweiteren separate Taktversorgung und Power-Management.

Bei einer Motorsteuerung würde beispielsweise die feldorientierte Regelung von dem Cortex-M4 mit seinen DSP-Befehlen berechnet, während der Cortex-M0 die Steuerungsbefehle über den CAN-Bus abarbeitet. Bei der Dekodierung einer Audio-Datei, die über den USB-Port eingelesen wird und ein Kopfhörer über den I2S-Port angeschlossen ist, würde der Cortex-M4 das Audio-Prozessing vornehmen und der Cortex-M0 die Peripheriesteuerung von USB- und I2C-Port vornehmen.

Für Entwickler ist wichtig, dass Cortex-M4 und Cortex-M0 eine Debug-Schnittstelle teilen, so dass mit einer JTAG/SWD-Einheit Debugging auf beiden Cores ermöglicht wird.

Wie der LPC1800 kann auch der LPC4300 Daten bei maximaler Taktfrequenz direkt aus dem Flash-Speicher lesen. Um dies und den Bus-Mastern den simultanen Zugriff auf Flash-Speicher und Peripherie zu ermöglichen, wurden 256 bit breite Busse implementiert. Dazu kommt eine intelligente Prefetch-Einheit, bei welcher ein eingebauter Algorithmus entscheidet, ob Befehle per Pre-Fetch eingelesen werden, wenn der Core schnell läuft, oder gewartet wird, bis der Flash-Puffer fast leer ist, wenn der Core langsam getaktet wird. Bei maximaler Taktfrequenz kann der Algorithmus mehr als acht Worte pro Pre-Fetch laden.

Für Applikationen, die eine hohe Ausfallsicherheit benötigen, kann der Flash-Speicher in einem sogenannten Front-Back-Modus betrieben werden, wo der Speicher in zwei Hälften geteilt und der Code nach einer Kopieraktion doppelt (einmal pro Speicherhälfte) vorhanden ist. Damit kann auch die sogenannte „Golden-Copy-Methode“ verwendet werden, bei welcher der Code in einer Speicherhälfte ausgeführt und zeitgleich die andere Hälfte z.B. bei einem Software-Update neu beschrieben wird -- eine Anforderung speziell aus der Automobil-Industrie.

Ein großer Vorteil des LPC4300 ist der Multi-Layer-AHB-Bus. Dessen Schaltmatrix ermöglicht es, RAM in mehrere Blöcke aufzuteilen, auf die dann von Core und allen Peripherieelementen parallel zugegriffen werden kann. Letztere können sogar als Bus-Master fungieren, insgesamt können acht Bus-Master definiert werden. So können für die DSP-Nutzung zwei SRAM-Blöcke für Code und Daten definiert werden (128 Kbyte und 72 Kbyte groß). Wenn die Befehle in einer Bank und die Daten in der anderen Bank gespeichert werden, steigt die Rechenleistung um rund 10 Prozent, noch mehr, wenn mittels der DSP-Operationen z.B. im Speicher abgelegte Wellenformen ausgelesen werden. Für Daten können dann noch drei weitere SRAM-Blöcke von 32, 16 und nochmals 16 Kbyte definiert werden.

Diese ganzen Verbindungen benötigen natürlich viele Leiterbahnen auf dem Die, weshalb der LPC4300 sieben Metallisierungeebenen inklusive zwei über den Speicherbereichen enthält.

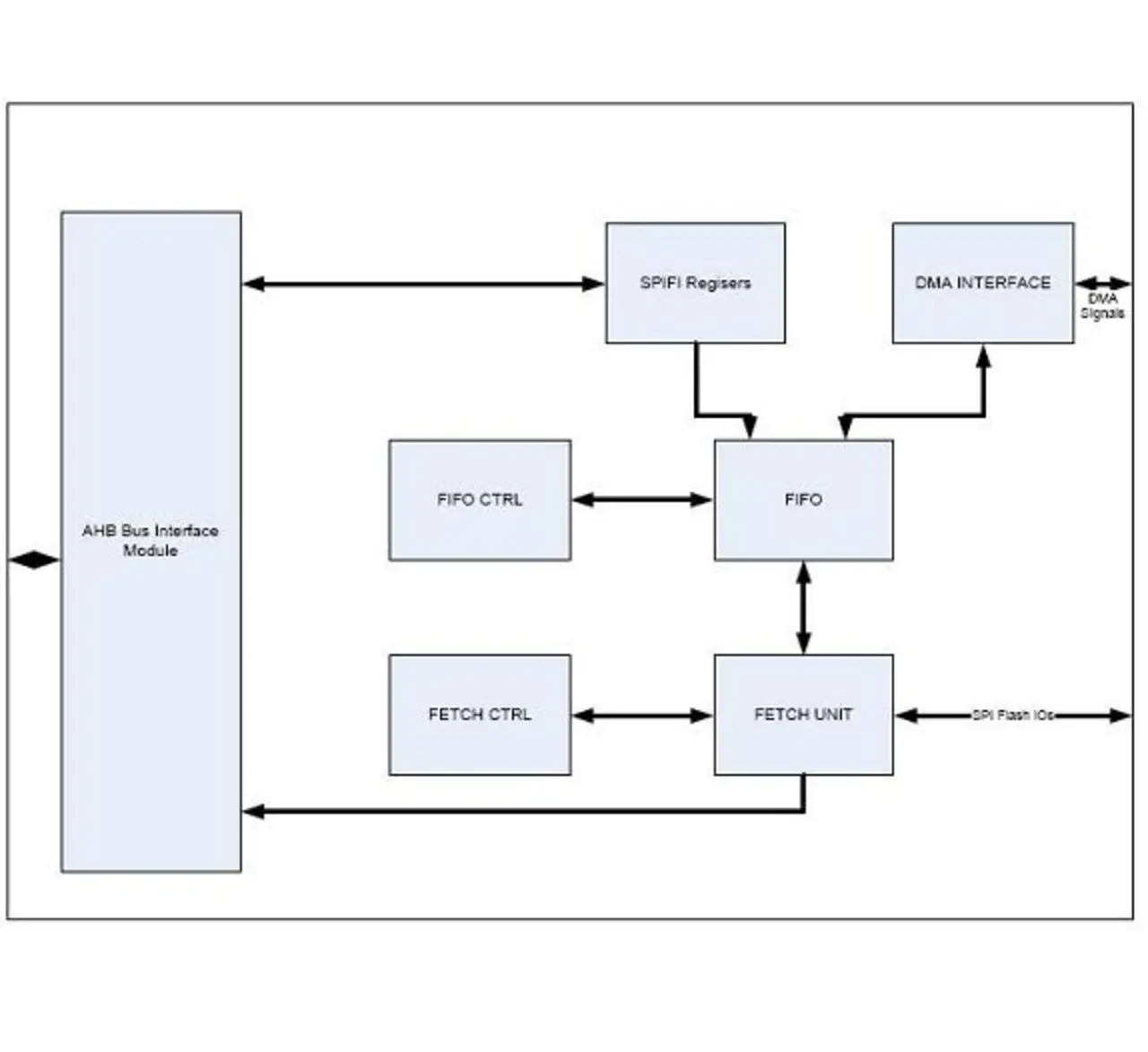

Mit dem LPC1800 wurden drei neue Peripherieelemente eingeführt, die auch im LPC4300 zum Einsatz kommen. Das erste ist eine SPI-Schnittstelle, die eine Quad-Mode-Operation für 8-Pin-Flash-ICs ermöglicht (Bild). Diese Schnittstelle kam bislang primär bei PCs zum Einsatz, die das BIOS darüber laden. Nach Abarbeitung des Handshake-Protokolls werden die Pins der SPI-Schnittstelle in vier Datenleitungen umkonfiguriert, die jeweils Datentransfers mit 80 Mbit/s ermöglichen - zusammen also 40 Mbyte/s. Damit kann der Inhalt des gesamten Flash-Speichers bei einem Kaltstart in 1/3 bis 1/100 s in den SRAM-Speicher auf dem Chip bzw. externes RAM transferiert werden. Diese Werte sind freilich nur dann erzielbar, wenn 256 Bytes pro Fetch gelesen werden und sinkt mit weniger gleichzeitig gelesenen Bytes ab: Wird jeweils nur 1 Byte gelesen, sinkt die Rate auf 5 Mbyte/s.

NXP hat die Quad-Mode-Operation mit 80 unterschiedlichen Flash-Chips von 512 Kbyte bis 16 Mbyte von den Herstellern Atmel, Gigadevice, Macronix, Micron, Microchip und Winbond getestet.

Ein typisches Problem bei MCU-Anwendungen mit LCD-Display ist die Speicherung von Bildern, die dann auf dem LCD-Display dargestellt werden. Sie werden im Flash-Speicher abgelegt und müssen in der Regel in den SRAM-Speicher kopiert werden, bevor sie zum LCD-Controller gesendet werden. Daher wird ein vergleichsweise großes SRAM benötigt. Mit der SPI-Schnittstelle können die Bilder mittels DMA jedoch direkt zum LCD-Controller geschickt werden, wodurch das SRAM nicht benötigt wird. Ebenfalls hilfreich ist die Schnittstelle bei der Ausführung von DSP-Algorithmen, die aus dem Flash-Speicher zur Ausführung in SRAM geladen werden müssen. Der LPC4300 kann zur Codespeicherung billigsten externen SPI-Flash-Speicher verwenden.

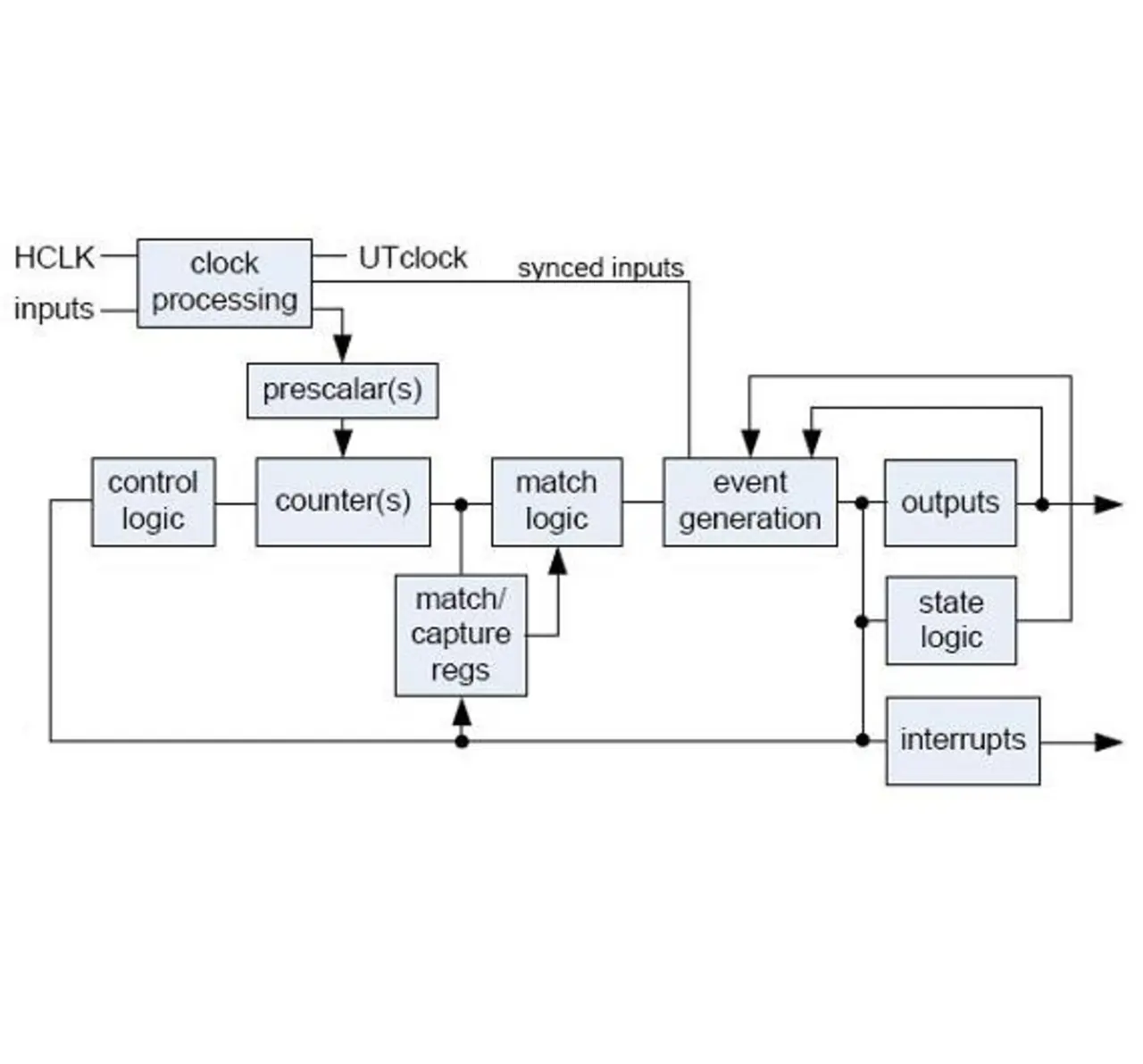

Das zweite interessante Peripherieelement das das sogenannte „State-Configurable-Timer-Subsystem“ (SCT, Bild). Dabei handelt es sich um einen programmierbaren Allzweck-Zustandsautomaten in Kombination mit einem Timer.

Die acht Eingänge des Zustandsautomaten und 16 Timer-Ausgänge werden auf Pins herausgeführt, um mit externer Hardware kommunizieren zu können. Nachdem der Zustandsautomat einmal von der CPU initialisiert wurde und vorausgesetzt, dass die Anzahl der Zustände nicht mehr als 16 beträgt, arbeitet der Timer für die Zustandsänderungen völlig autonom und benötigt keine weitere Involvierung der CPU.

Ein weiterer Block dekodiert aus Eingängen, Ausgängen und Zuständen bis zu 16 Ereignisse, um den Zustandsautomaten von einem Zustand in den nächsten zu überführen.

Als triviales Anwendungsbeispiel für eine reine Hardwareimplementierung könnte man eine Ampelsteuerung heranziehen, bei der man fünf Ausgänge (3 Lampen für die Autos und zwei für die Fußgänger), einen Eingang (Knopf den Fußgänger drücken, um Ampelsignal anzufordern) und vier Stati (Auto=Grün, Fußg.=Rot, Auto=Gelb, Fußg.=Rot, Auto=Rot, Fußg.=Rot und Auto=Rot, Fußg.=Grün) hat.

Die Funktionalität soll laut NXP jedoch auch dazu ausreichen, auch komplexe Funktionalität wie die Steuerung eines bürstenlosen Gleichstrommotors, eines Schrittmotors oder eines Wechselstrom-Induktionsmotors abzubilden. Möglich wäre auch der Betrieb einer seriellen Schnittstelle wie DALI oder LIN, die nicht als Peripherie auf dem Chip abgebildet sind. Um den Zustandsautomaten zu programmieren, kann das Tool Fizzim (www.fizzim.com) eingesetzt werden.

Das dritte interessante Peripherieelement nennt sich SGPIO (Serial-GPIO) und hat die Aufgabe, den Prozessor beim seriellen Datentransfer zu entlasten. Das Problem für Designer ist oft, dass am Markt erhältliche Peripherie (z.B. LCD-Treiber, Audio-Codecs) proprietäre serielle Schnittstellen einsetzen. Der Entwickler muss dann für die Erzeugung und den Transfer der Bit-Ströme Schleifen programmieren („Bit-Banging“), die nicht nur Rechenzeit kosten, sondern auch eine Überführung in Low-Power-Modi verhindert.

Beim LPC4300 ist folgende Lösung implementiert: Es gibt 16 Ein-/Ausgänge, die jeweils eigene Timer- und zwei 32-bit-Schiebe-Register enthalten. Dazu kommt noch ein Zähler, der die Anzahl der Bits, die gesendet bzw. empfangen werden, zählt. Durch einfache Programmierung dieser Register werden die Bit-Ströme definiert und automatisch ausgegeben. Wenn der Bit-Strom komplett gesendet wurde, wird ein Interrupt ausgelöst. NXP wird für diverse Schnittstellen (z.B. Quad-SPI, I2S, I2C oder SPI) Beispiele in Form von Bibliotheken bereitstellen.

Wo kann der LPC4300 mit dem Cortex-M4 seine Stärken ausspielen? Nehmen wir als Beispiel einen IIR-Filter 2. Ordnung, der folgender Gleichung genügt:

y[n] = b0x[n] + b1x[n-1] + b2x[n-2] – a1y[n-1] – a2y[n-2]

In der Tabelle ist der entsprechende Code mit der Anzahl der Taktzyklen auf dem Cortex-M3 (LPC1800) bzw. Cortex-M4 (LPC4300) nur für die innere Schleife dargestellt. Dabei sei angenommen, dass sich die Koeffizienten b0, b1, b2, a1 und a2 ebenso in Registern befinden wie die vorhergehenden Zustände x[n-1], x[n-2], y[n-1] und y[n-2]. Durch die DSP-Befehle des Cortex-M4 kann die Anzahl der Taktzyklen von 27-47 (abhängig von den Daten) auf 16 reduziert werden. Durch eine weitergehende handische Optimierung ist sogar eine Reduzierung auf 10 Taktzyklen möglich.

NXP wird kostenlose C-Bibliotheken von DSP-Algorithmen bereistellen, die u.a. FFT (16- und 32-bit-Daten, Blockgrößen 64, 256 und 1024 bit), FIR- und IIR-Filter (16- und 32-bit-Biquad), PID-Controller, Zufallszahlengenerator und Vektor-Kreuzprodukt beinhalten.

Die ersten verfügbaren Mitglieder der LPC4300-Familie (4310, 4320, 4330 und 4350) werden ohne Flash-Speicher ausgeliefert und können daher nur mit externem Flash-Speicher betrieben werden. Muster soll es im ersten Quartal 2011 geben, die Chips mit Flash-Speicher folgen im 2. Quartal 2011. Diese MCUs werden dann 512 Kbyte, 768 Kbyte oder 1 Mbyte Flash-Speicher aufweisen.

| Instruktion | Zyklen Cortex-M3 | Zyklen Cortex-M4 |

|---|---|---|

| xN = *x++; |

2 | 2 |

| yN = xN * b0; | 3-7 | 1 |

| yN += xNm1 * b1; | 3-7 | 1 |

| yN += xNm2 * b2; | 3-7 | 1 |

| yN -= yNm1 * a1; | 3-7 | 1 |

| yN -= yNm2 * a2; | 3-7 | 1 |

| *y++ = yN; | 2 | 2 |

| xNm2 = xNm1; | 1 | 1 |

| xNm1 = xN; | 1 | 1 |

| yNm2 = yNm1; | 1 | 1 |

| yNm1 = yN; | 1 | 1 |

| Schleifenzähler verringern | 1 | 1 |

| Verzweigung | 2 | 2 |

| Summe Taktzyklen | 27-47 | 16 |

Durch die DSP-Anweisungen kann ein IIR-Filter auf dem Cortex-M4 mit weniger Taktzyklen implementiert werden als auf dem Cortex-M3.