Der schnellste ARM-Mikrocontroller

150 MHz für den Cortex-M3

NXP ist einer der treuesten ARM-Lizenznehmer für Mikrocontroller: Die Cores Cortex-M3, -M0 und -M4 finden sich in den MCU-Produkten der Niederländer wieder. Jetzt gibt es mit dem LPC1800 eine weitere Serie mit Cortex-M3, die gegenüber der aktuellen Familie LPC1700 erhebliche Vorteile aufweist.

Der erste Fortschritt des LPC1800 (Bild 1) besteht im Schrumpfen der Prozessgeometrie auf 90 nm. Durch die schneller schaltenden Transistoren wird eine Taktfrequenz von 150 MHz erreicht, laut NXP werden in späteren Controllern sogar 200 MHz angestrebt. Die größte Herausforderung ist dabei nicht die Erhöhung der Core-Frequenz, sondern der Zugriff auf den Flash- Speicher. Schon der LPC1700 konnte Daten bei maximaler Taktfrequenz direkt aus dem Flash-Speicher lesen; dies ist beim LPC1800 trotz der Erhöhung der Core-Frequenz ebenfalls so. Um dies und den Bus-Mastern den simultanen Zugriff auf Flash-Speicher und Peripherie zu ermöglichen, wurden von NXP breitere Busse implementiert.

Während bei dem 128 bit breiten Flash im LPC1700 „nur“ 4×32-bit-Befehle in einem Taktzyklus gelesen werden konnten, wurde im LPC1800 ein 256 bit breiter Bus implementiert. Des weiteren wurde im Vergleich zum LPC1700 eine intelligentere Prefetch- Einheit verwendet, bei welcher ein eingebauter Algorithmus entscheidet, ob Befehle per Prefetch eingelesen werden, wenn der Core schnell läuft, oder gewartet wird, bis der Flash-Puffer fast leer ist, wenn der Core langsam getaktet wird. Mit diesem Verfahren wird im Vergleich zum LPC1700 eine erhebliche Einsparung bei der Leistungsaufnahme erzielt. Bei maximaler Taktfrequenz kann der Algorithmus mehr als acht Worte pro Prefetch laden.

Für Applikationen, die eine hohe Ausfallsicherheit benötigen, kann der Flash-Speicher in einem so genannten Front-Back-Modus betrieben werden, wo der Speicher in zwei Hälften geteilt und der Code nach einer Kopieraktion doppelt (einmal pro Speicherhälfte) vorhanden ist. Damit kann auch die „Golden-Copy-Methode“ verwendet werden, bei welcher der Code in einer Speicherhälfte ausgeführt und zeitgleich die andere Hälfte, z.B. bei einem Software-Update, neu beschrieben wird – eine Anforderung speziell aus der Automobil-Industrie.

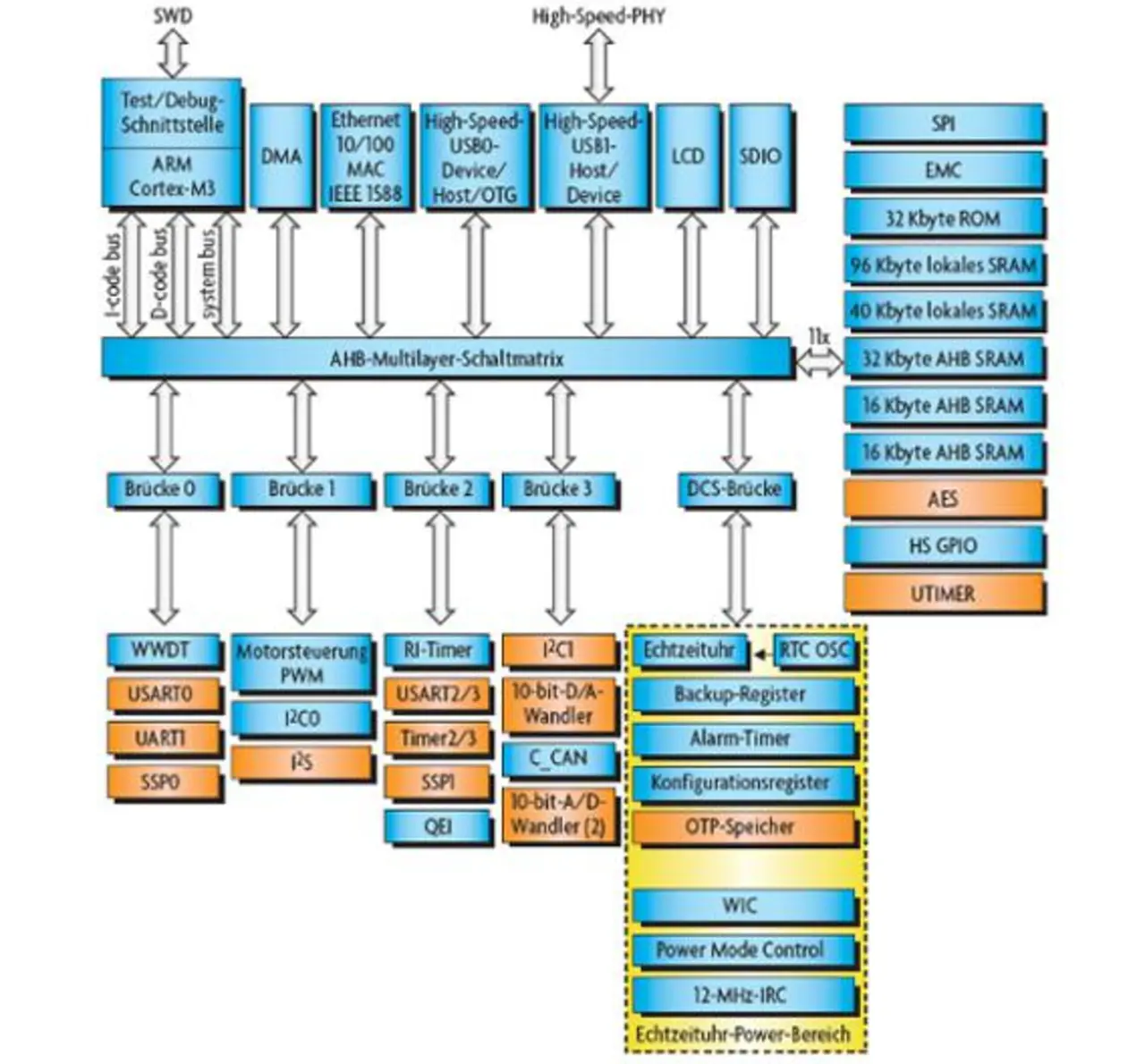

Ein großer Vorteil des LPC1800 auch gegenüber dem LPC2000 ist der Multi- Layer-AHB-Bus. Dessen Schaltmatrix ermöglicht es, RAM in mehrere Blöcke aufzuteilen, auf die dann vom Core und von allen Peripherieelementen parallel zugegriffen werden kann. Letztere können sogar als Bus-Master fungieren; insgesamt können acht Bus- Master definiert werden. Diese ganzen Verbindungen benötigen natürlich viele Leiterbahnen auf dem Die, weshalb der LPC1800 sieben Metallisierungsebenen inklusive zwei über den Speicherbereichen enthält.

Die Möglichkeit, den Flash-Speicher in zwei Hälften zu teilen, hat noch einen anderen Vorteil: Wenn die Befehle in einer Bank und die Daten in der anderen Bank gespeichert werden, steigt die Rechenleistung um rund 10 Prozent. Noch relevanter als beim LPC1800 dürfte dieses Verfahren jedoch bei NXPs zukünftigen Cortex- M4-basierenden Produkten sein, wenn mittels der DSP-Operationen z.B. im Speicher abgelegte Wellenformen ausgelesen werden.

Jobangebote+ passend zum Thema

- 150 MHz für den Cortex-M3

- Zwei bemerkenswerte Peripherie-Elemente