Moderne Halbleitertechnologien

GaN – Die Zeit ist reif

Fortsetzung des Artikels von Teil 2

GaN in HF-Leistungsanwendungen

Damit GaN-on-Si in High-End-HF-Applikationen durchgehend mit etablierten GaN-on-SiC-Bauelementen konkurrieren kann, sind noch einige technische Hürden zu überwinden. Einige davon wie die geringere thermische Leitfähigkeit von Si im Vergleich zu SiC lassen sich durch eine starke Reduzierung der Substratdicke bei der Fertigung der Bausteine überwinden.

Eine weitere größere Hürde ist die unerwünschte Ausbildung einer leitfähigen Schicht zwischen dem Si-Substrat und der III-Nitrid-Schichtstruktur während der Epitaxieabscheidung. Dieser parasitäre Pfad bewirkt einen HF-Signalverlust. Transistoren, die auf derartigen verlustbehafteten Substraten gefertigt werden, können niemals hohe Effizienz bei hohen Frequenzen erreichen.

Jobangebote+ passend zum Thema

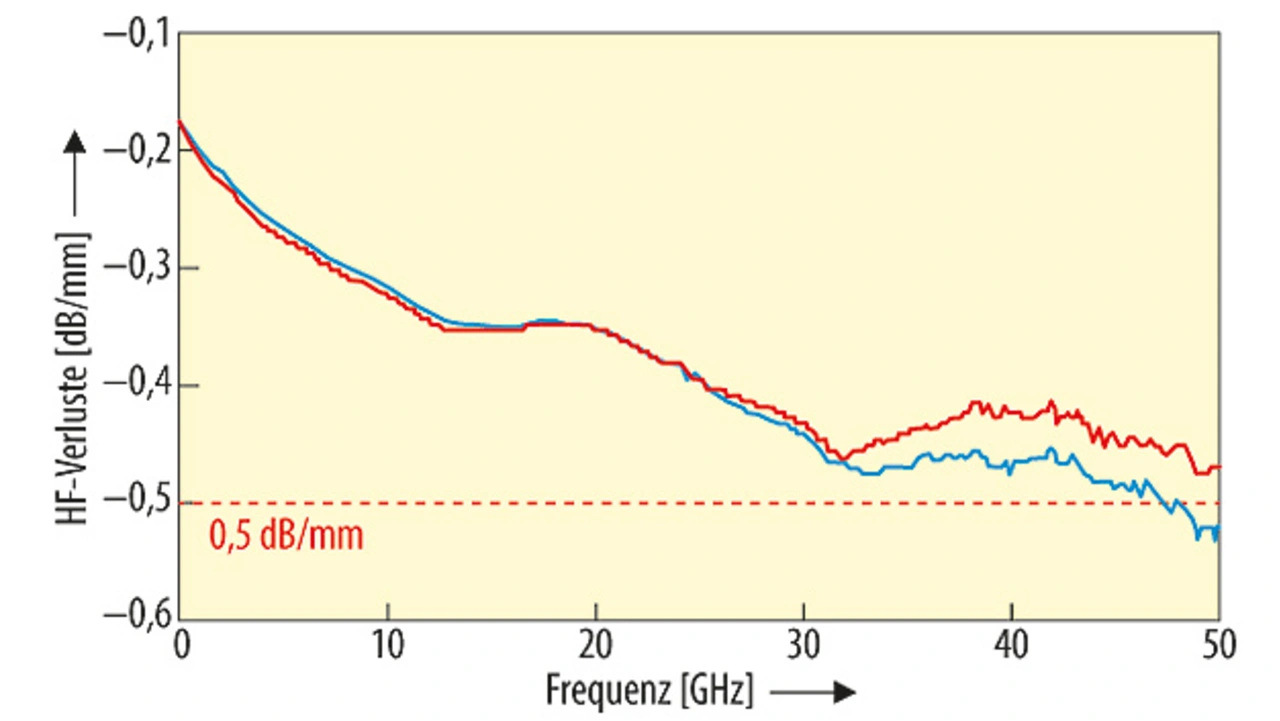

Bei EpiGaN wurde deshalb eine robuste Interface-Technologie entwickelt, um die Effekte dieses leitfähigen Pfads zu minimieren. Dadurch wird der HF-Signalverlust von GaN-on-Si bei 2 GHz von vorher 1,5 dB/mm (und mehr) auf weniger als 0,25 dB/mm abgesenkt, was den Werten, die sich mit dem sehr viel teureren GaN-on-SiC-Material erreichen lassen, bereits sehr nahe kommt. Sogar bei 50 GHz liegt der HF-Signalverlust für GaN-on-Si jetzt unterhalb von 0,5 dB/mm (Bild 1).

In naher Zukunft will EpiGaN die Machbarkeit von hochohmigen 200-mm-CZ-Wafer-Si-Substraten für HF-Leistungsanwendungen validieren. Dies dürfte im Endeffekt die Kosten für HF-Leistungsbausteine auf der Basis der GaN-on-Si-Technologie weiter drücken und ihren Einsatz in den heutigen Fertigungslinien für 200-mm-Wafer ermöglichen – und zwar sowohl bei den Si-IDMs als auch bei Si-Foundries.

Vorteil der binären AlN-Barriere

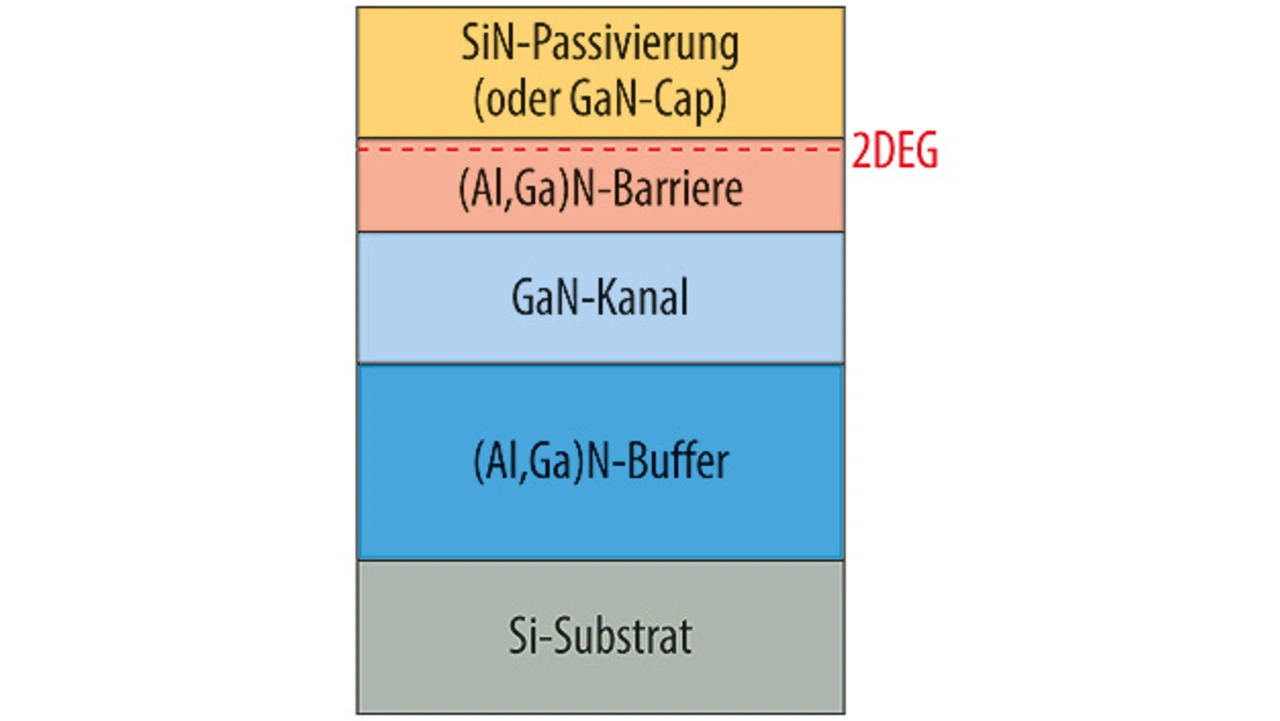

Parallel zur Unterdrückung der HF-Verluste hat sich EpiGaN auf die Entwicklung von HEMT-Heterostrukturen mit reinen AlN-Barrieren konzentriert, die außerdem über eine In-situ-SiN-Cap-Schicht verfügen. Sie sind eine Alternative zu den typischen AlGaN-Bausteinen und könnten diese eventuell eines Tages ersetzen. In dieser spezifischen Konfiguration ist es möglich, die Dicke der Barriereschicht von den heute typischen Werten von etwa 20 nm auf bis zu 4 nm zu reduzieren. Dies erlaubt die Anordnung des Transistor-Gate sehr nahe am leitenden Kanal und damit die Maximierung der elektrostatischen Kopplung zwischen beiden (mit dem Resultat verbesserter Gate-Treiber-Eigenschaften).

Das führt zu einer weitaus überlegenen HF-Transistor-Charakteristik. Die sogenannten parasitären Short-Channel-Effekte, also die Verringerung des Übertragungsleitwertes (Transconductance) infolge der ungünstigen Proportion der Gate-Länge zum Kanalabstand (idealerweise mit einem Verhältnis von mehr als 15:1) werden beim Skalieren der Transistor-Gates auf weniger als 0,15 μm mit dem Einsatz von ultradünnen AlN-Barrieren unterdrückt. Außerdem maximiert die AlN-Barriere den für dieses Materialsystem inhärenten piezoelektrischen Effekt. Damit ergibt sich eine Ladungsträgerdichte von mehr als 2∙1013 cm–2 im 2DEG- (zweidimensionales Elektronengas) Kanal des Transistors, womit die Ausgangsleistungsdichte gesteigert werden kann. Mit geeignetem thermischem Layout lassen sich so signifikante Verkleinerungen der Chips erzielen.

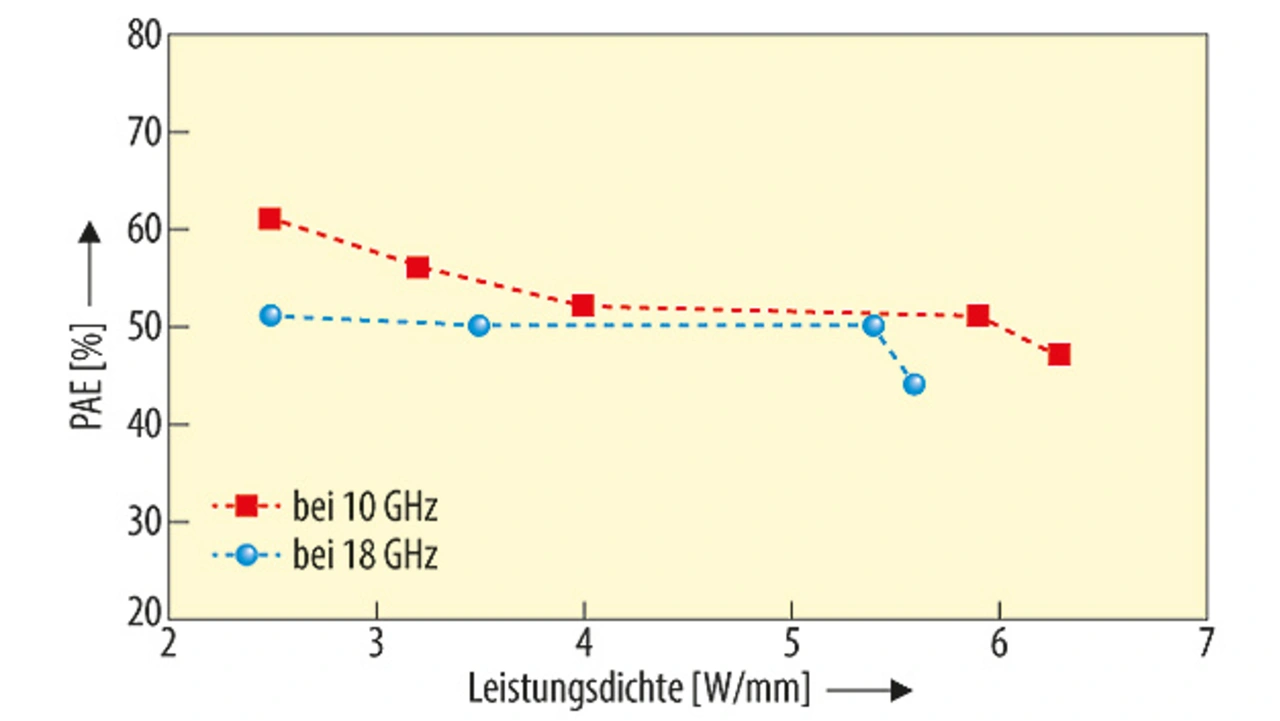

In einer Kollaboration mit IEMN-CNRS wurden Transistoren auf EpiGaNs GaN-on-SiC-HF-Wafern hergestellt, die eine Leistungsdichte von mehr als 5 W/mm bei einer Betriebsfrequenz von 18 GHz aufweisen, zusammen mit einem Leistungs-Wirkungsgrad (power added efficiency, PAE) größer als 50 % (Bild 2). Die hohe Leistung wird sogar bei viel höheren Frequenzen bis 40 GHz aufrechterhalten.Transistoren mit einer Gate-Länge von 120 nm zeigten eine Cut-off-Frequenz der Leistungsverstärkung oberhalb von 230 GHz bei UDS=20 V. Ein 2×25-μm-AlN/GaN-HEMT erreichte immer noch einen Spitzenwert der Leistungsdichte von 4,5 W/mm, zusammen mit einem maximalen PAE von 46,3 % bei 40 GHz.

- GaN – Die Zeit ist reif

- Weitere Schwerpunkte der GaN-Technologie-Entwicklung

- GaN in HF-Leistungsanwendungen

- GaN-on-Si für Leistungsschalter