Formel 1 der Bits

FPGAs als Schnittstellten in Embedded-Systemen

Fortsetzung des Artikels von Teil 1

Serial RapidIO und PCI-Express

Betrachtet man Applikationen in den Bereichen Wireless, Medizin oder Militär/ Luftfahrt, so wird man feststellen, dass dort sehr viele Daten aufgenommen und berechnet werden müssen. Diese Last wird auf mehrere DSPs verteilt, die aber auch miteinander kommunizieren müssen. Mehrere DSPs zu verschalten, kann sich beliebig schwierig auf der Boardseite gestalten. Daher wurde der RapidIO-Standard eingeführt, der Kommunikationsteuerung über einen Switch erlaubt.

Jobangebote+ passend zum Thema

Neben der parallelen Leitungsführung wurde hier auch ein serieller Ansatz definiert – Serial RapidIO. Hier werden je nach Standard eine, zwei oder vier Leitungen verwendet, die Daten mit bis zu 3,125 Gbit/s oder mit 5 Gbit/s übertragen. Serial RapidIO findet man häufig bei DSPs der Firmen Texas Instruments und Freescale.

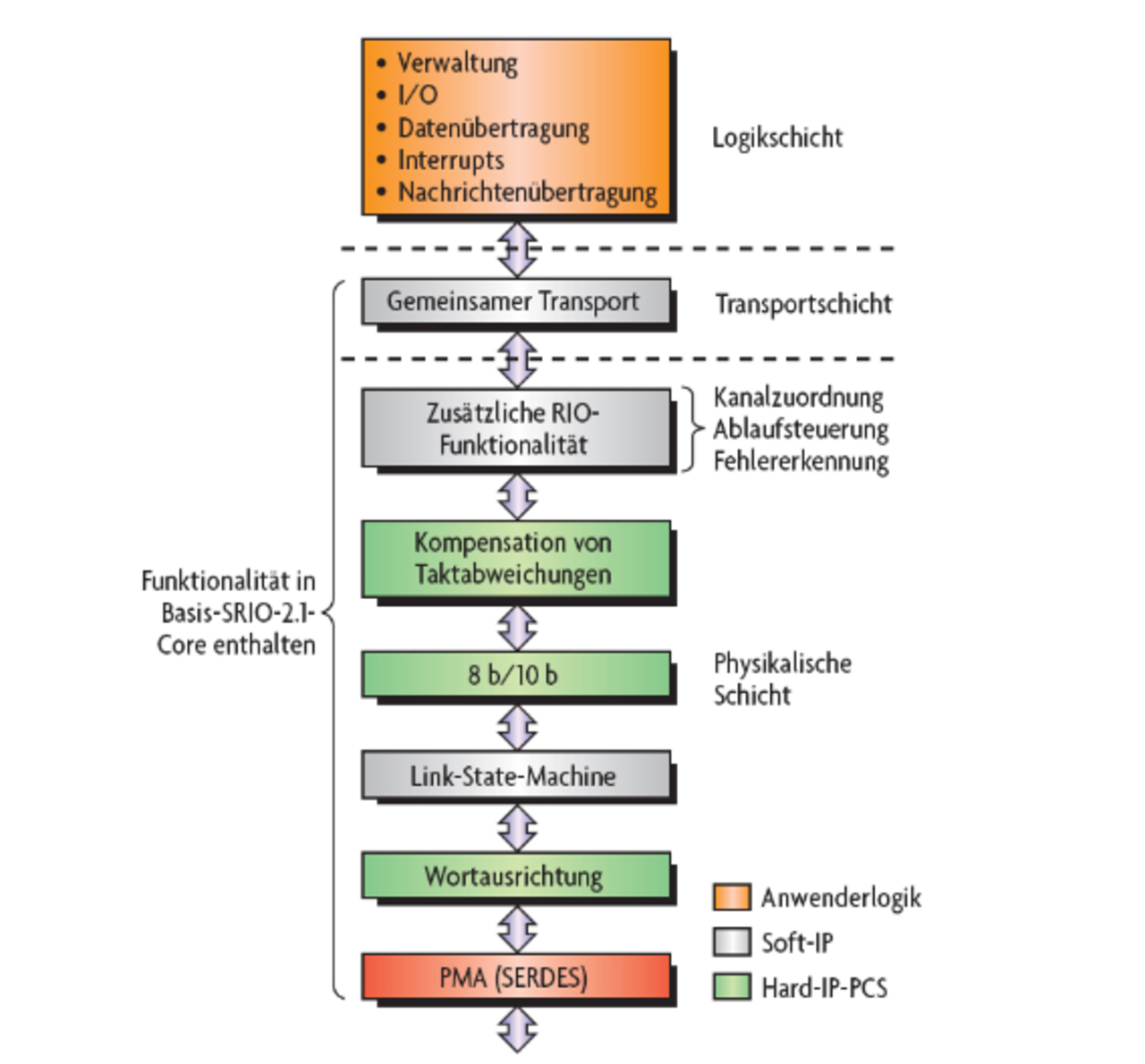

Das Serial-RapidIO- Protokoll ist auch wieder, wie in Bild 5 gezeigt, aus verschiedenen Schichten aufgebaut. Die physikalische Schicht beinhaltet die elektrische Schnittstelle, Logik zur Fehlererkennung und die Ablaufsteuerung. Die Transportschicht kümmert sich um die Adressierung der Datenpakete, damit diese am richtigen Endpunkt ankommen. Für den Anwender am wichtigsten ist die Logikschicht, da von dieser die empfangenen Daten kommen und seine Daten zum Senden übergeben werden. Diese drei Schichten werden im FPGA wieder aus einer Kombination von fest verdrahteten Komponenten und Soft-IP realisiert. Auch hier müsste man ohne integrierte SERDES-Blöcke wieder auf einen zusätzlichen externen Baustein zurückgreifen.

Im April 2003 wurde die Spezifikation von PCI-Express veröffentlicht. Hier wurden die bisherigen Nachteile von PCI durch eine neue sternförmige, vollduplexe Architektur, die mit seriellen Kanälen mit 2,5 Gbit/s arbeitet, ausgemerzt. Zudem können beim Umstieg von PCI auf PCI-Express vorhandene Software-Treiber weiterverwendet werden.

Um für größere Bandbreiten- Anforderungen gerüstet zu sein, kann man auch bei PCI-Express mehrere Kanäle benutzen. Die Kanalanzahl wird in der Literatur als x1, x2, x4, x8 usw. gekennzeichnet. Schon die Verwendung eines x1- Links stellt theoretisch 2 Gbit/s in beide Richtungen zur Verfügung. Eine klassische 32-bit-33- MHz-PCI-Verbindung könnte theoretisch nur 1 Gbit/s in einer Richtung zur Verfügung stellen.

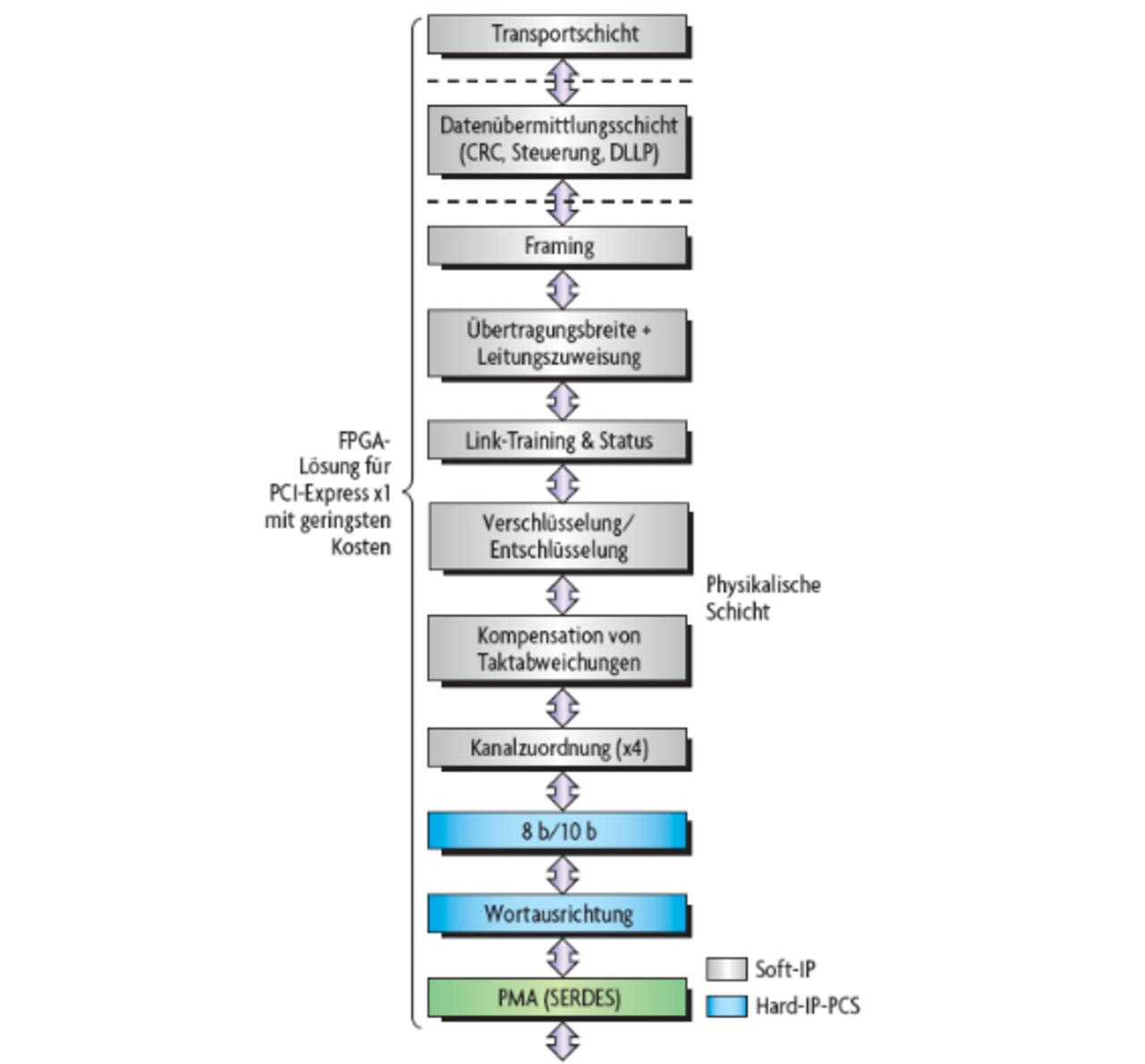

Wie die meisten Protokolle ist auch PCI-Express in verschiedene Protokollschichten eingeteilt. Die SERDES-Blöcke der ECP3-Familie bieten einige Funktionen der physikalischen Schicht bereits fest verdrahtet in den SERDES-Blöcken an. Die restlichen Schichten bis zur Transaktions-Schicht werden in Soft-IP realisiert, die in den programmierbaren Zellen des FPGA untergebracht wird (Bild 6). Dies hat gegenüber fest verdrahteten IP-Cores den großen Vorteil, dass man auf Änderungen in der Spezifikation schnell reagieren kann. Mittels des Tools IPExpress lässt sich der PCI-Express- Core vor der Generierung entsprechend den Anforderungen konfigurieren.

Um in diese Thematik einen schnellen Einstieg zu finden, steht ein Design- Kit zur Verfügung. Dieses beinhaltet ein PCI-Express-Board für eine x1- und eine x4-Verbindung, aber auch entsprechende Beispiele für komplette PCIExpress- Designs inklusive der Quellen (HDL und Software-Treiber). Eines der Beispiele zeigt den Einsatz eines DMAControllers. Ein DMA-Controller ist immer dann wichtig, wenn viele Daten bewegt werden sollen, aber der Prozessor nicht belastet werden soll.

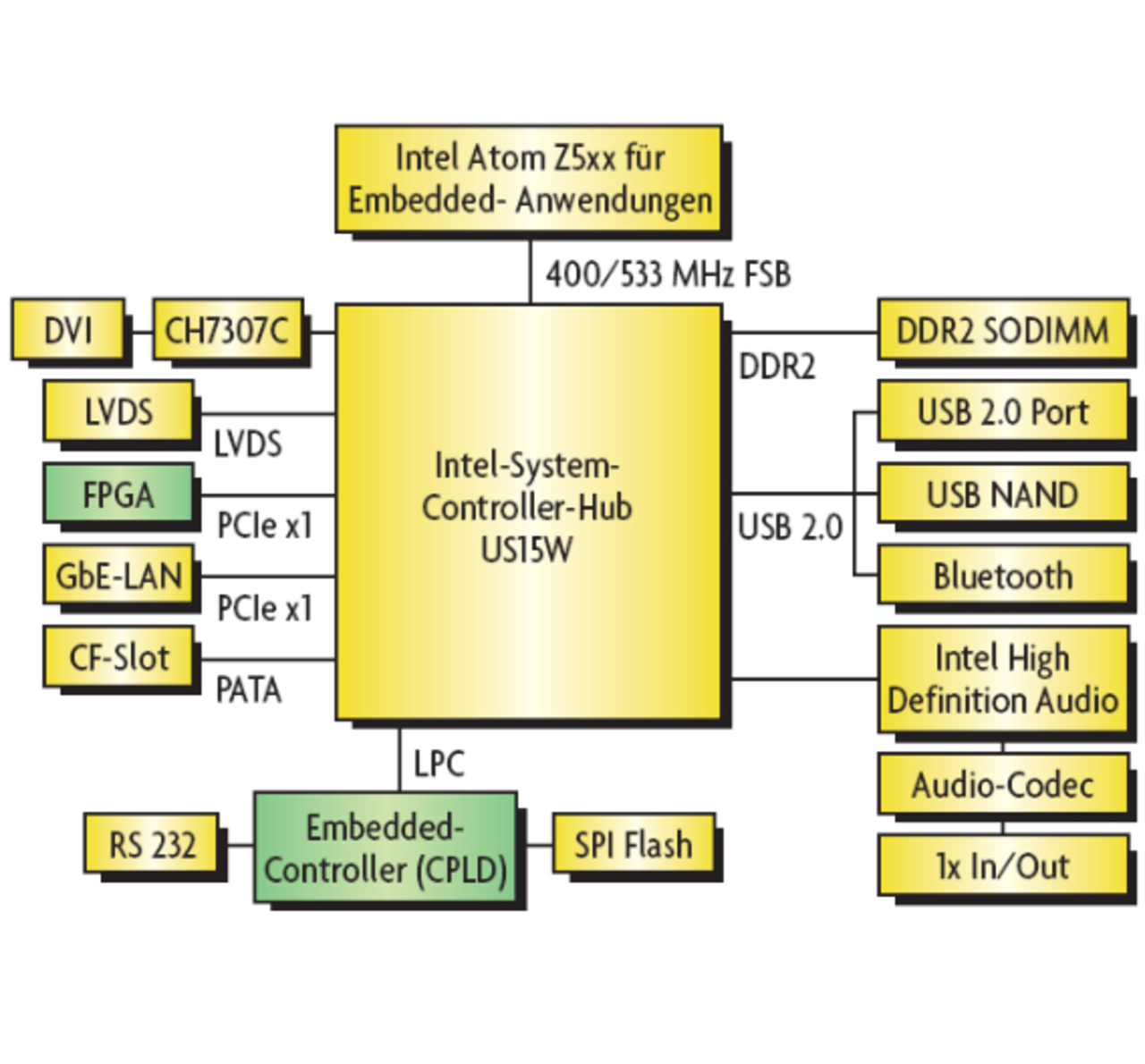

Wo sind nun aber die Hauptanwendungen dieser Protokolle in Embedded- Systemen? PCI-Express ist zum Beispiel immer notwendig, wenn es um den Atom-Prozessor geht. Dieser Prozessor eignet sich wegen seiner geringen Verlustleistung besonders für Embedded-Systeme wie industrielle Steuerungen, Sicherheitssysteme, Industrial- Ethernet (z.B. Sercos3), Point- Of-Sale-Anwendungen oder für Multimedia- Applikationen im Auto.

Allerdings hat Intel bei der Prozessor/ Chipset-Kombination auf alle älteren Schnittstellen verzichtet. Somit ist immer eine PCI-Express-Anbindung notwendig, um mit dem Rest das Systems zu kommunizieren (Bild 7).

FPGA mit SERDES

Es wurde nun schon bei den diversen Protokollen festgestellt, dass eine ideale Lösung die Kombination von SERDES mit dem FPGA ist, um sich vollständig von den Nachteilen paralleler Busstrukturen lösen zu können. In der Anfangszeit standen allerdings nur teure High-End-FPGAs mit integrierten SERDES-Kanälen zur Verfügung. Dies wurde vielleicht noch in hochwertigen Telecom-Systemen akzeptiert, aber nicht bei kostensensitiven Applikationen aus den Bereichen Industrie oder Medizin.

Aus diesem Grund gibt es bereits die zweite Generation von preisgünstigen FPGAs mit integrierten SERDES- Kanälen, die Lattice-ECP3-Familie. Diese arbeitet mit bis zu 16 seriellen Kanäle mit bis zu 3,125 Gbit/s. Darüber hinaus stehen bis zu 150 k LUT, DSP-Blöcke mit Multiplizierern, Addierern/Subtrahierern und Akkumulatoren und bis zu 6,8 Mbit interner Speicher zur Verfügung. Die DSP-Blöcke können zur Verarbeitung der Daten verwendet werden und können somit DSPs entlasten oder in einigen Fällen überflüssig machen.

Ein wichtiges Thema ist auch die Leistungsaufnahme, da diese die Dimensionierung der Netzteile beeinflusst, aber, noch wichtiger, auch für Abwärme verantwortlich ist, die wieder vom System abgeführt werden muss. Wie der Artikel gezeigt hat, werden gerade schnelle serielle Kommunikationen immer mehr eingesetzt, und eine kombinierte Lösung bietet natürlich Vorteile. Es wird Platz auf der Leiterkarte eingespart, das EMV-Verhalten fällt positiver aus, und durch die vom Hersteller zur Verfügung gestellten IP-Cores können die Funktionen sehr schnell implementiert werden.

- FPGAs als Schnittstellten in Embedded-Systemen

- Serial RapidIO und PCI-Express

- Literatur und Autor