Frühzeitig über alle verbrauchsspezifischen Kenndaten Bescheid wissen

Welche Leistungsaufnahme hat mein ASIC-Design?

Fortsetzung des Artikels von Teil 1

Welche Leistungsaufnahme hat mein ASIC-Design?

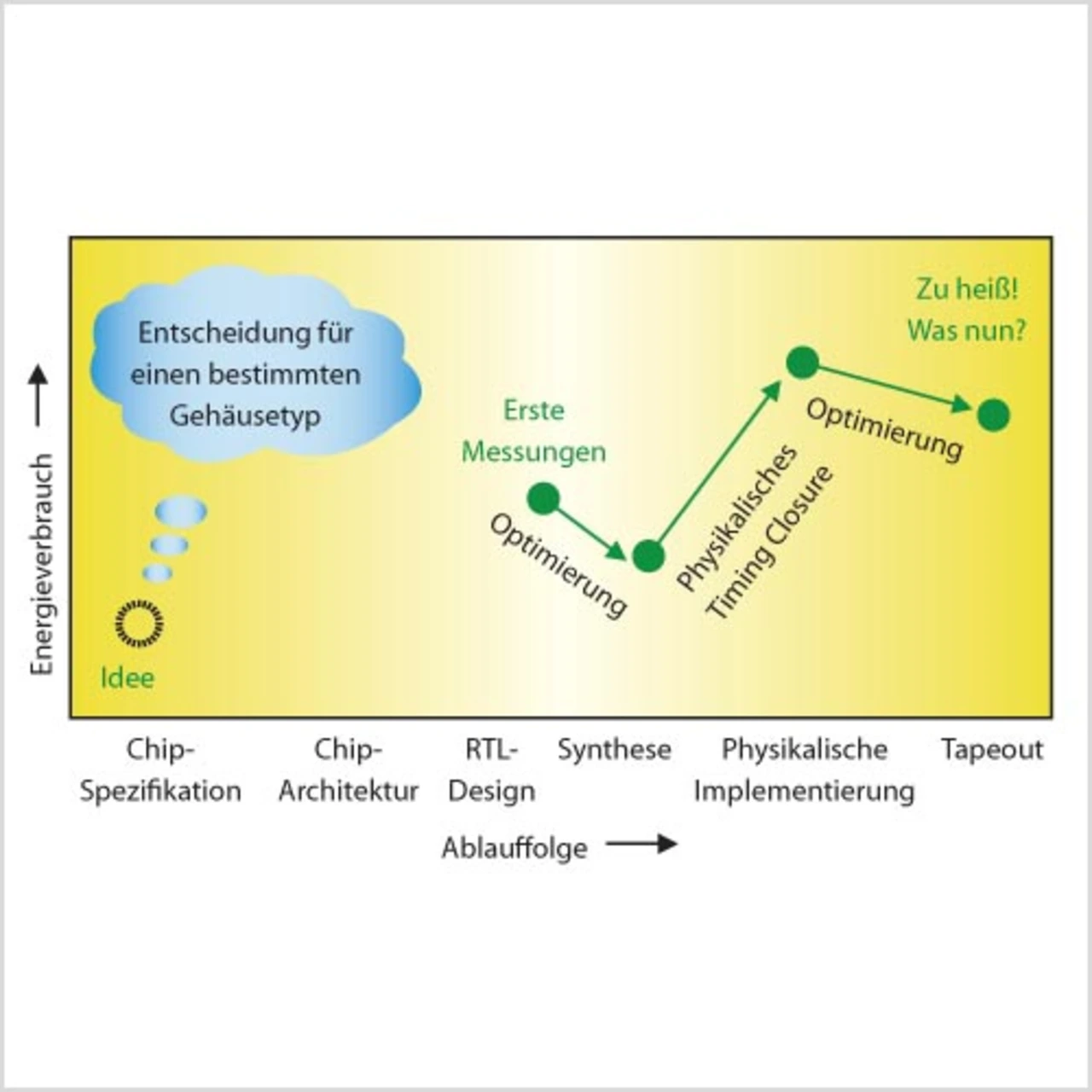

Dieser Umstand äußert sich meist erst während der physikalischen Implementierung, wo das Timing Closure aufgrund langer Leitungen immer anspruchsvoller wird. An diesem Punkt erfordert eine Timing-Optimierung in der Regel ein Upsizing, bei dem durch den Einsatz von Zellen mit niedrigeren Schaltspannungen (aber hohen Leckströmen), einem zusätzlichen Puffer und anderen Verfahren die Leistungsaufnahme erhöht wird. Der Designzyklus ist dann allerdings zu weit fortgeschritten, um nochmals die RTL-Struktur oder die Leistungsarchitektur ändern zu können oder um Verfahren wie mehrfache Versorgungsspannungen oder Power-Shut-off zu nutzen. Diese Änderungen würden letztendlich eine erneute funktionelle Verifikation – unter Umständen einen erneuten Durchlauf der Implementierung – erforderlich machen. Die IC-Entwickler müssen in dieser Phase zumindest unangenehme Entscheidungen treffen, denn mit steigendem Stromverbrauch müssen unter Umständen ein anderes Gehäuse ausgewählt oder bestimmte Funktionen wieder entfernt werden, um das geforderte Leistungsbudget nicht zu überschreiten. Das Projekt läuft im wahrsten Sinne des Wortes „aus dem Ruder“.

Jobangebote+ passend zum Thema

Bild 1 veranschaulicht ein typisches Szenario, bei dem durch eine nicht mögliche Vorhersagbarkeit der Leistung und das bevorstehende Tapeout dem Entwickler nur noch zwei Möglichkeiten bleiben. Entweder ignoriert er die Kosten und erweitert sein Design mit einem teuren Kühlungsmechanismus oder er ignoriert den Zeitplan und überarbeitet die Architektur. Die Hauptursache dafür könnte sein, dass die Leistungsaufnahme nicht effektiv genug oder nicht frühzeitig genug im Prozess gemessen worden ist. Wer also künftig bei seinen Designs die Leistungsvorhersagbarkeit verbessern will, der sollte sich fragen, welche Faktoren die Leistung und parallel dazu die Vorhersagbarkeit beeinflussen.

Jeder Entwickler muss sich zuerst im Klaren sein, dass Entscheidungen und Aktionen, die frühzeitig im Designprozess durchgeführt werden, eine deutlich größere Auswirkung auf das Ergebnis haben als Maßnahmen zu einem späteren Zeitpunkt. Andererseits muss er in Kauf nehmen, dass früh getroffene Voraussagen im Flow meist ungenauer sind. Er wird also versuchen, möglichst frühzeitig mit umfassenden, groben Verfahren zu experimentieren. Und je solider die Implementierung wird, desto genauer sind die Voraussagen und desto feiner die Verfahren, die er dann nutzen kann.

Die erste Kenngröße, die den Stromverbrauch des Chips beeinflusst, ist die eigentliche Chip-Spezifikation:

- Welche Funktionen soll der Halbleiterbaustein enthalten?

- Welche Frequenz wird für den Chip und welche für die größeren Blöcke benötigt?

- Welche Prozessgeometrie kommt zum Einsatz?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Stromverbrauchs-Analysen muss man vor dem Syntheseschritt durchführen

- Welche Leistungsaufnahme hat mein ASIC-Design?