Frühzeitig über alle verbrauchsspezifischen Kenndaten Bescheid wissen

Welche Leistungsaufnahme hat mein ASIC-Design?

Fortsetzung des Artikels von Teil 3

Welche Leistungsaufnahme hat mein ASIC-Design?

Wie bereits erwähnt, ist die Designspezifikation geschäfts- und marktorientiert und hat den größten Einfluss auf die Leistungsaufnahme. Damit ist es wichtig, dass hier die Entscheidungen mit einem genauen Verständnis über die leistungsbestimmenden Parameter getroffen werden. Am besten verwendet man dazu eine Methode, welche die Erfahrungen von bisherigen Designs mit so vielen realen Implementierungsinfomationen als möglich kombiniert. Dies lässt sich beispielsweise durch den Einsatz eines frühzeitigen physikalischen Prototypings in Kombination mit einer RTL-Leistungseinschätzung erreichen. Die Teile des Designs, die wiederverwendet werden, können im neuen Zusammenhang und mit neuen Bibliotheken erneut betrachtet werden. Dies erlaubt eine sehr viel genauere Schätzung, die auch implementierungsspezifische Details berücksichtigt. Der Rest kann nach wie vor geschätzt werden, indem man diese als Design-Objekte darstellt. Auf diese Weise steht ein früher Prototyp auf Chipebene für weitere Entscheidungen zur Verfügung, der sich, sobald im Entwurfsprozess mehr Details verfügbar werden, weiter verfeinern lässt.

Jobangebote+ passend zum Thema

Natürlich ist die Schätzung des Stromverbrauchs auch stark vom Betriebsprofil und den Schaltaktivitäten des Designs abhängig. Frühe Prototypen können Schätzungen auf der Basis von Standard-Schaltaktivitäten nutzen, da die Messungen grob sind und nicht das gesamte RTL zur Erzeugung der Schaltaktivität zur Verfügung steht. Auf jeden Fall erfordert der Implementierungsprozess detailliertere Eingangsinformationen, für welche die aktuellen Schaltaktivitäten benötigt werden. Zudem ist es wichtig, sicherzustellen, dass die Schaltaktivitäten genau dem geplanten Betriebsprofil des Chips entsprechen. Funktionelle Verifikations-Testbenches sind hierfür nicht ausreichend. Denn sie sind darauf ausgerichtet, alle funktionellen Szenarien so effizient wie möglich abzudecken – mit anderen Worten, ohne viel Wiederholung. Im Hinblick auf das Beispiel Mobiltelefon oder Netzwerk-Switch beinhalten echte Betriebsprofile allerdings viele Wiederholungen und wenige Grenzfälle, auf die sich die Verifikation konzentriert. Die beste Methode, um Schaltaktivitäten zu erfassen, sind gesonderte Simulationsdurchläufe zur Erfassung der Betriebsaktivitäten. Und weil dies oft sehr lange dauert, lässt sich die Effizienz mit Hilfe der Hardware-Beschleunigung deutlich verbessern. Emulation bietet sich dafür an, da diese die wirkliche Software ausführen und dabei eine gute Testmenge der Schaltaktivitäten generieren kann.

In dieser Phase des Designprozesses muss der Entwickler noch Kompromisse hinsichtlich der Implementierung machen, also zum Beispiel festlegen, welche Teile des Chips entscheidend für die Leistungsfähigkeit sind und welche nicht. Zudem muss er Entscheidungen darüber treffen, welche Spannungspegel erforderlich sind oder ob ein variables Verfahren wie die dynamische Spannungs- oder Frequenzskalierung genutzt werden soll. Er hat auch festzulegen, welche Teile des Chips über längere Zeit inaktiv sind und deshalb abgeschaltet werden können, um Verlustleistung zu reduzieren. Er muss ferner definieren, wie schnell ein Block, der abgeschaltet worden ist, später wieder eingeschaltet werden kann? Wenn ein vollständiger Reset-Zyklus zu viel Zeit kostet, kann man das Wiedereinschalten u.a. dadurch beschleunigen, dass man den Status in einen immer betriebsbereiten Speicher legt. Die schnellste Variante indes ist die Verwendung von State-Retention-Registern. Wie zu erwarten, gibt es auch bei diesem Ansatz eine gewisse Einschränkung, da man für diesen Lösungsansatz ein zusätzliches Power-Routing benötigt.

Die Implementierungsarchitektur als Ganzes hat eine große Auswirkung auf die Leistungsaufnahme, aber selbst in dieser Phase sind Kompromisse hinsichtlich der Frequenzziele und der Implementierungsdurchführbarkeit noch notwendig. Man sollte zudem ausreichend Zeit für „was wäre wenn“-Analysen einplanen, um mit ihnen sinnvolle Kompromisse hinsichtlich der komplexen Zusammenhänge in Bezug auf Leistungsaufnahme, Timing und Platzbedarf voraussagen zu können. Darüber hinaus ist es sinnvoll, dass der Entwickler implementierungsgenaue Messungen durchführt – entweder anhand aktueller Synthese-Ergebnisse oder anhand eines virtuellen Halbleiterprototypen. Am Ende dieses Designschrittes jedenfalls dürften sehr brauchbare Schätzungswerte bezüglich des Stromverbrauchs, der Timing-Durchführbarkeit, der physikalischen Durchführbarkeit und der funktionellen Richtigkeit vorliegen.

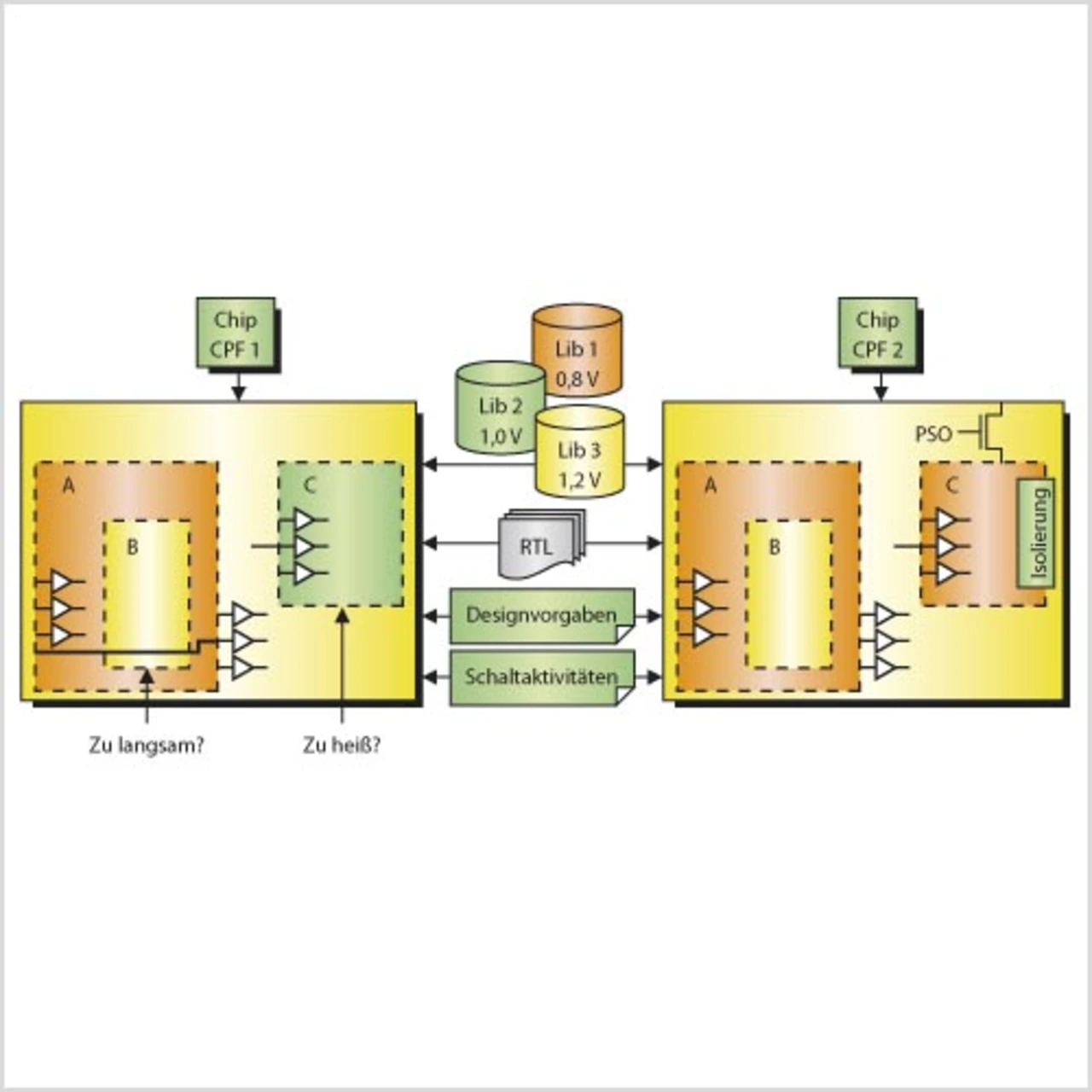

Bild 2 gibt beispielhaft wieder, wie eine „was wäre wenn“-Power-Architektur-Untersuchung auf Basis einer zentralen Power-Format-Spezifikation ablaufen könnte.

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Welche Leistungsaufnahme hat mein ASIC-Design?

- Stromverbrauchs-Analysen muss man vor dem Syntheseschritt durchführen

- Welche Leistungsaufnahme hat mein ASIC-Design?