IC-Schaltungsentwurf ist mit der physikalischen Implementierung des Gehäuses zu verbinden

SiP statt SoC: Entwurf eines HF-Systems

Fortsetzung des Artikels von Teil 4

SiP statt SoC: Entwurf eines HF-Systems

Alles zusammen ermöglicht nicht nur den gemeinsamen Entwurf („Co-Design“) der verwendeten ICs, z.B. von HF-Frontend-IC und digitalem Basisband-IC, sondern auch der weiteren Komponenten auf dem Gehäuse-Substrat.

Die wichtigsten Implementierungsschritte für den Entwurf von HF-System-in-Packages können wie folgt zusammengefasst werde

- Schaltungsentwurf und Simulation,

- physikalische SiP-Implementierung,

- Extraktion parasitärer Effekte und erneute Simulation.

Jobangebote+ passend zum Thema

Diese Schritte werden in den folgenden Abschnitten weiter erläutert. Bei dem zugrundeliegenden Designbeispiel handelt es sich – wie bereits erwähnt – um eine WLAN-802.11-b-Applikation. Das Design besteht aus einem HF-IC in 180-nm-CMOS-Technik, einem Analog/Mixed-Signal-IC in 90-nm-CMOS-Technik als Interface zum Basisband sowie verschiedenen passiven Komponenten und einem separaten Power-Amplifier-Modul (PA) auf einem LTCC-Keramik-Substrat. Alles zusammen wird in einem Gehäuse mit einem organischen FR4-Substrat vereint.

Schaltungsentwurf und Simulation

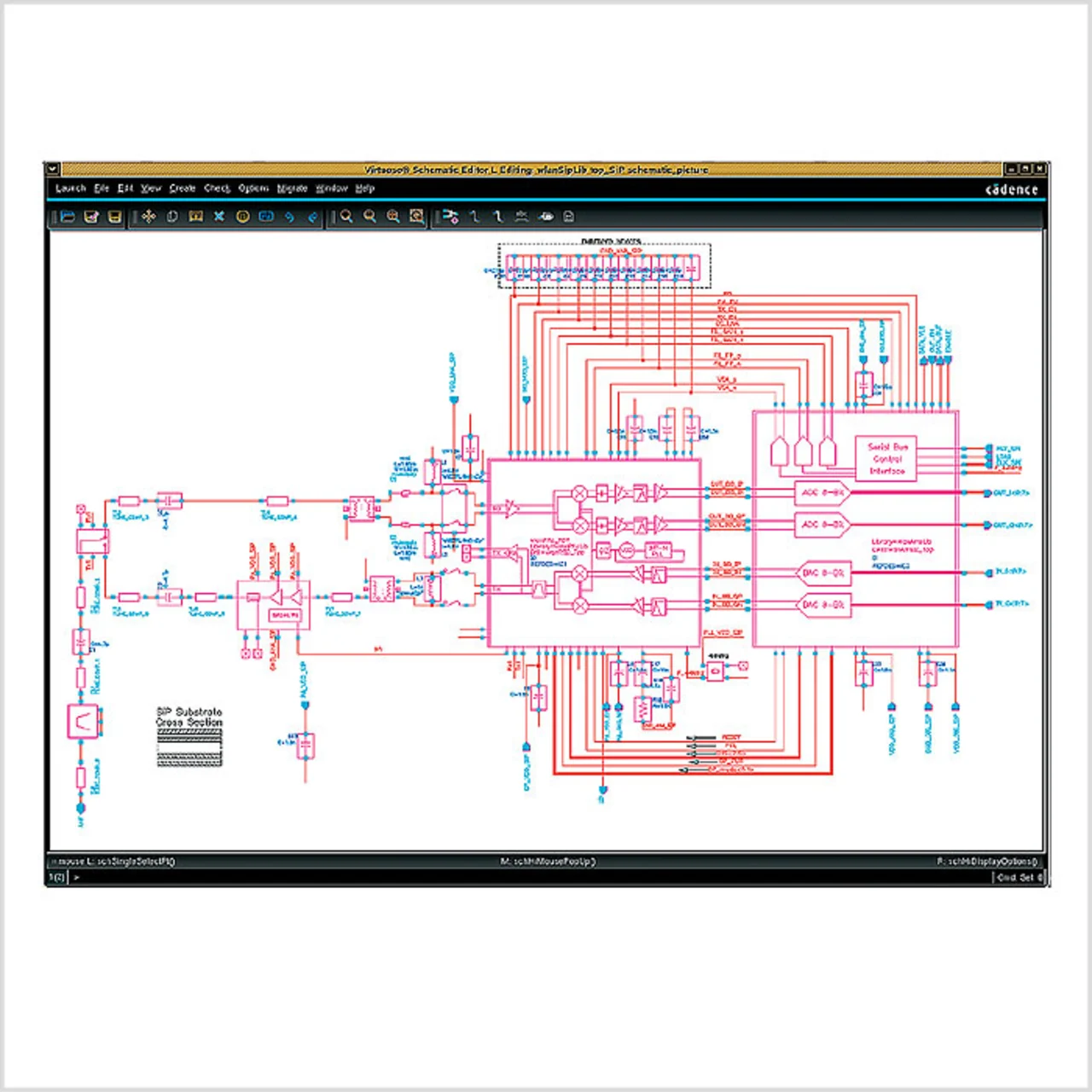

Der Entwurf beginnt mit der vollständigen Beschreibung des Gesamtsystems als Schaltplan inklusive aller Komponenten und deren Verbindungen. Bild 3 zeigt das entsprechende Top-Level-Schematic für das hier verwendete Schaltungsbeispiel einer WLAN-802.11-b-Sende-/Empfangseinheit. Neben den beiden ICs existieren zahlreiche Komponenten, die zusätzlich innerhalb des gemeinsamen Gehäuses integriert werden. Im linken Bildteil sind beispielsweise die HF-relevanten Bauteile (z.B. Filter, Schalter oder PA-Modul) zu erkennen, die sich zwischen Antenne und HF-IC-Eingang befinden. Aber auch Verbindungsleitungen auf dem Gehäusesubstrat und der Leiterplatte sowie die Bonddraht-Verbindungen zum HF-IC-Eingang werden bereits berücksichtigt.

Zusammen mit den zugehörigen Testbenches für die benötigten Messungen, z.B. Error-Vector-Magnitude (EVM) oder Bit-Error-Rate (BER), bildet dies eine simulierbare Systemspezifikation. Neben der richtigen Partitionierung und der Performance des Gesamtsystems lässt sich, bei geeigneter Modellierung, auch eine funktionale Verifikation bereits in diesem frühen Entwurfsstadium durchführen.

Der virtuelle Prototyp dient somit als Basis für kontinuierliche Regressions-Tests je nach Entwurfsstadium und erlaubt so eine frühzeitige Erkennung möglicher Probleme. Die einzelnen Blöcke können auf diese Weise unabhängig voneinander in verschiedenen Projektteams entworfen und optimiert werden.

Für die Top-Level-Simulation ist die Verwendung eines Mixed-Signal-Simulators notwendig, der sprachenunabhängig verschiedene Abstraktionsebenen und Simulationsverfahren unterstützt.

- SiP statt SoC: Entwurf eines HF-Systems

- Literatur

- Umfassendere Berücksichtigung parasitärer Effekte

- SiP statt SoC: Entwurf eines HF-Systems

- SiP statt SoC: Entwurf eines HF-Systems

- Durchgängiger Design-Flow, basierend auf realistischem Referenzdesign

- SiP statt SoC: Entwurf eines HF-Systems