IC-Schaltungsentwurf ist mit der physikalischen Implementierung des Gehäuses zu verbinden

SiP statt SoC: Entwurf eines HF-Systems

Fortsetzung des Artikels von Teil 5

Durchgängiger Design-Flow, basierend auf realistischem Referenzdesign

Um die genannten Herausforderungen zu adressieren, reichen keine inkrementellen Erweiterungen bestehender Entwurfswerkzeuge mehr aus. Es bedarf einer deutlichen Änderung des Entwurfs-Flows und der zugrundeliegenden Methodik, um vor allem die Lücke vom Schaltungsentwurf zur physikalischen SiP-Implementierung zu schließen. Dabei muss aber auf bestehende Tools, die sich im reinen IC-Entwurf bzw. der Gehäuse-Implementierung bewährt haben, aufgesetzt werden.

Cadence adressiert solch komplexe Design-Herausforderungen innerhalb bestimmter Applikationssegmente durch so genannte „Kits“ [1]. Im Rahmen derer werden anhand eines repräsentativen Designs alle relevanten Entwurfsschritte – basierend auf einer zugrundeliegenden Methodik – durchgeführt und ausführlich dokumentiert. Für den Wireless-Bereich handelt es sich bei dem verwendeten repräsentativen Design um eine WLAN-802.11-b-Applikation, und für den darin enthaltenen Transceiver-Baustein wurde der entsprechende HF-IC-Flow bereits in einem früheren Beitrag vorgestellt [2]. Weitere Informationen zum hier vorgestellten HF-SiP-Kit sind in [3] zu finden.

Jobangebote+ passend zum Thema

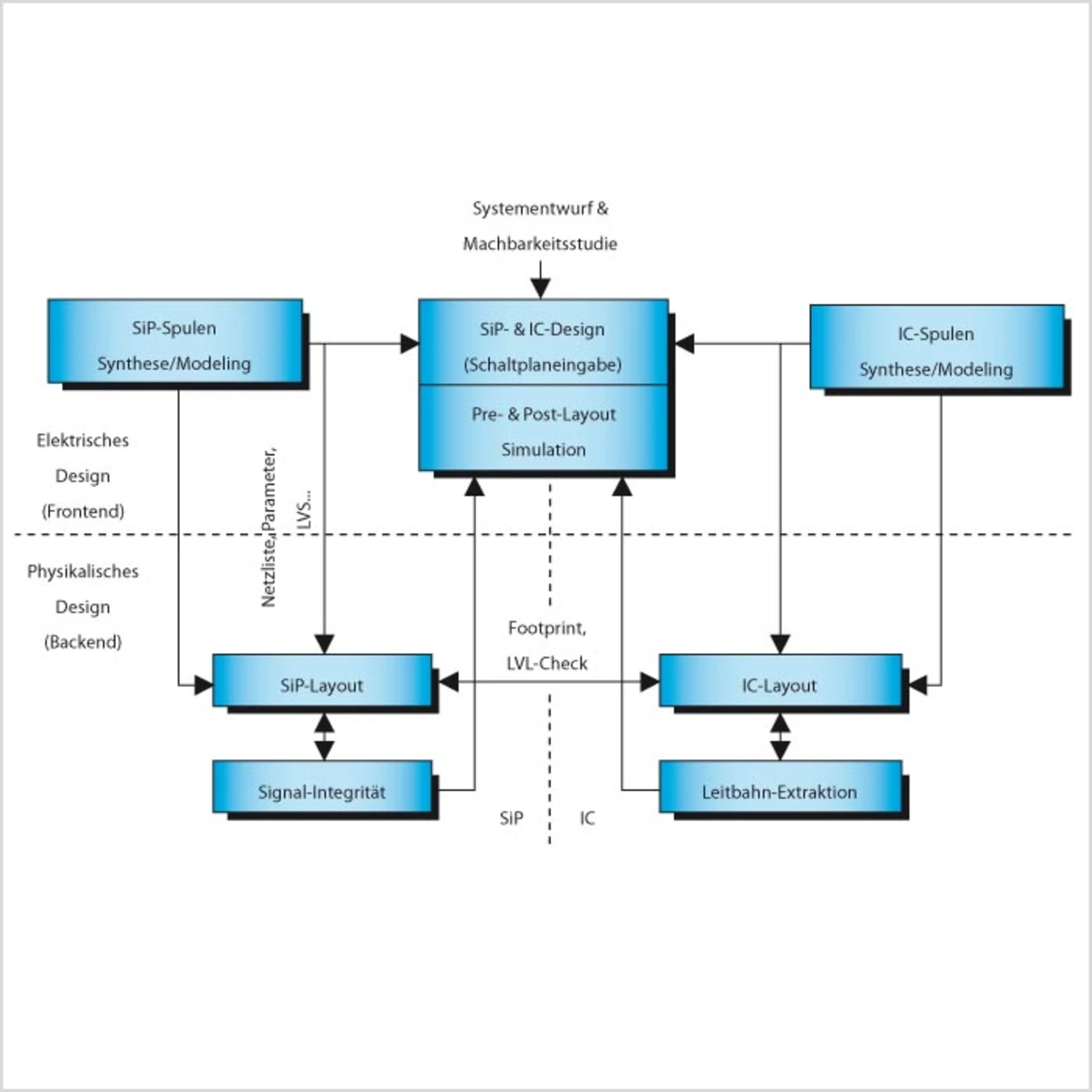

Der HF-SiP-Flow lässt sich generell in Schaltungsentwurf und Simulation (Frontend) sowie in physikalische Implementierung (Backend) unterteilen. Diese beiden Bereiche sind in Bild 2 entsprechend in der oberen bzw. unteren Hälfte zu finden. Des Weiteren unterscheidet das Flow-Diagramm zwischen SiP- (linke Bildhälfte) und IC-Entwurf (rechte Bildhälfte). Für den Frontend-Bereich gibt es diese Unterscheidung nicht wirklich – der Schaltungsentwurf ist also unabhängig von der angestrebten Integration.

Aufbauend auf Ergebnissen aus dem Systementwurf und einer ersten Machbarkeitsstudie, beginnt der Entwurf mit der Beschreibung des gesamten Systems in einem gemeinsamen Schaltplan. Die Entwurfsumgebung, z.B. Schaltplaneingabe-Tool und Simulationsumgebung, ist dabei die gleiche, wie sie für den Entwurf einzelner ICs verwendet wird. Der Schaltplan wird dazu durch die entsprechenden Komponenten, die sich außerhalb der ICs im bzw. auf dem Gehäuse-Substrat befinden, ergänzt – so lange, bis ein so genannter „Virtueller Prototyp“ des Gesamtsystem entstanden ist. Zusammen mit den zugehörigen Testbenches für die benötigten Messungen – wie Error-Vector-Magnitude (EVM) oder Bit-Error-Rate (BER) – bildet dieser eine simulierbare Systemspezifikation. Bis hierher entsprechen der Entwurfs-Flow und die zugrundeliegende Methodik damit weitestgehend dem eines HF-ICs [1].

Bei der physikalischen Implementierung eines SiP kommt es durch die damit verbundene Aufbau- und Verbindungstechnik zu unterschiedlichen Anforderungen an das Entwurfswerkzeug gegenüber einem monolithisch integrierten Chip. Mit Bonddraht-Verbindungen oder Die-Stacking sind hier nur zwei Beispiele genannt, die durch herkömmliche IC-Layout-Tools nicht abgedeckt werden. Aber auch hier gilt es, vom IC-Entwurf zu „lernen“. Entscheidend dafür ist die neu bereitgestellte, enge Verzahnung von Frontend und Backend, was im IC-Entwurf bereits seit langem etabliert ist.

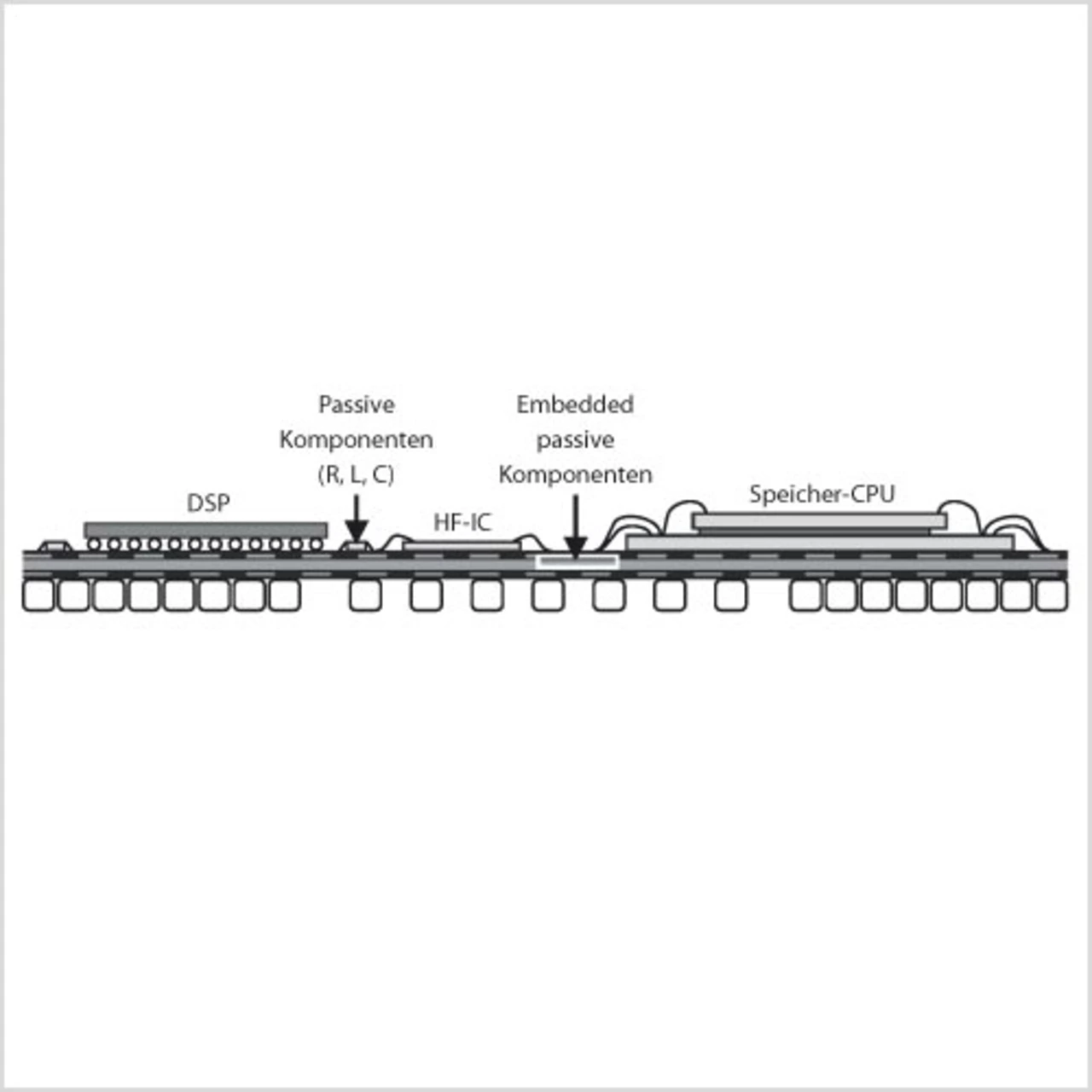

Ein weiteres Merkmal von SiP ist die mögliche vertikale Integration von Komponenten. Dabei „stapelt“ man beim so genannten Die-Stacking mehrere Chips übereinander. Die Verbindung der Chips zum Gehäusesubstrat erfolgt wahlweise durch Bonddrähte oder Flip-Chip-Montage (siehe Bild 1).

SoC und SiP stellen die zwei wesentlichen Herstellungsverfahren für komplexe integrierte Halbleiterbausteine dar. Welche Variante letztendlich günstiger ist, hängt von einer Vielzahl von Faktoren ab – z.B. dem geforderten Funktionsumfang, der erwarteten Stückzahl oder dem zur Verfügung stehenden Entwicklungszeitraum. Oft ist es nicht wirklich eine Frage für das eine oder das andere, sondern vielmehr eine Frage dessen, wie viel effizient auf einem einzelnen Chip integriert werden kann und welche Teile als separater Die realisiert oder direkt ins Gehäusesubstrat eingebunden werden sollten.

Dadurch ist das Gehäuse nicht mehr nur das Bindeglied zwischen Chip und Leiterplatte, sondern Teil des Gesamtsystems. Dies erfordert eine ganzheitliche Betrachtung – vom Schaltkreisdesign bis zur physikalischen Implementierung.

- SiP statt SoC: Entwurf eines HF-Systems

- Literatur

- Umfassendere Berücksichtigung parasitärer Effekte

- SiP statt SoC: Entwurf eines HF-Systems

- SiP statt SoC: Entwurf eines HF-Systems

- Durchgängiger Design-Flow, basierend auf realistischem Referenzdesign

- SiP statt SoC: Entwurf eines HF-Systems