IC-Schaltungsentwurf ist mit der physikalischen Implementierung des Gehäuses zu verbinden

SiP statt SoC: Entwurf eines HF-Systems

Fortsetzung des Artikels von Teil 3

SiP statt SoC: Entwurf eines HF-Systems

Der eigentliche Knackpunkt und die Besonderheit von drahtlosen Übertragungssystemen gegenüber anderen komplexen Mixed-Signal-Schaltungen liegt im HF-Frontend. Zwischen der Antenne und dem Ab- bzw. Aufwärtsmischer in der Empfangs- bzw. Sendeeinheit ist das eigentliche Nutzsignal noch dem für die Übertragung notwendigen hochfrequenten Trägersignal überlagert. Neben den damit verbundenen Anforderungen an den Schaltungsentwurf und die deutlich höhere Sensitivität gegenüber parasitären Effekten stellt dies eine zusätzliche Herausforderung für die Gesamtsimulation dar. Herkömmliche transiente Simulationen sind für die notwendigen Systemtests zur Überprüfung der zulässigen Bit-Error-Rate meist zu langwierig. Neben speziellen Analysen wie Envelope oder Fast-Spice zur effizienteren Simulation kommt hier vor allem geeigneten Modellierungsmethoden besondere Bedeutung zu. Wichtig ist, dass bereits zu Projektbeginn alle notwendigen Tests und die damit verbundenen Simulationen bzw. erforderlichen Abstraktionslevel definiert sind.

Jobangebote+ passend zum Thema

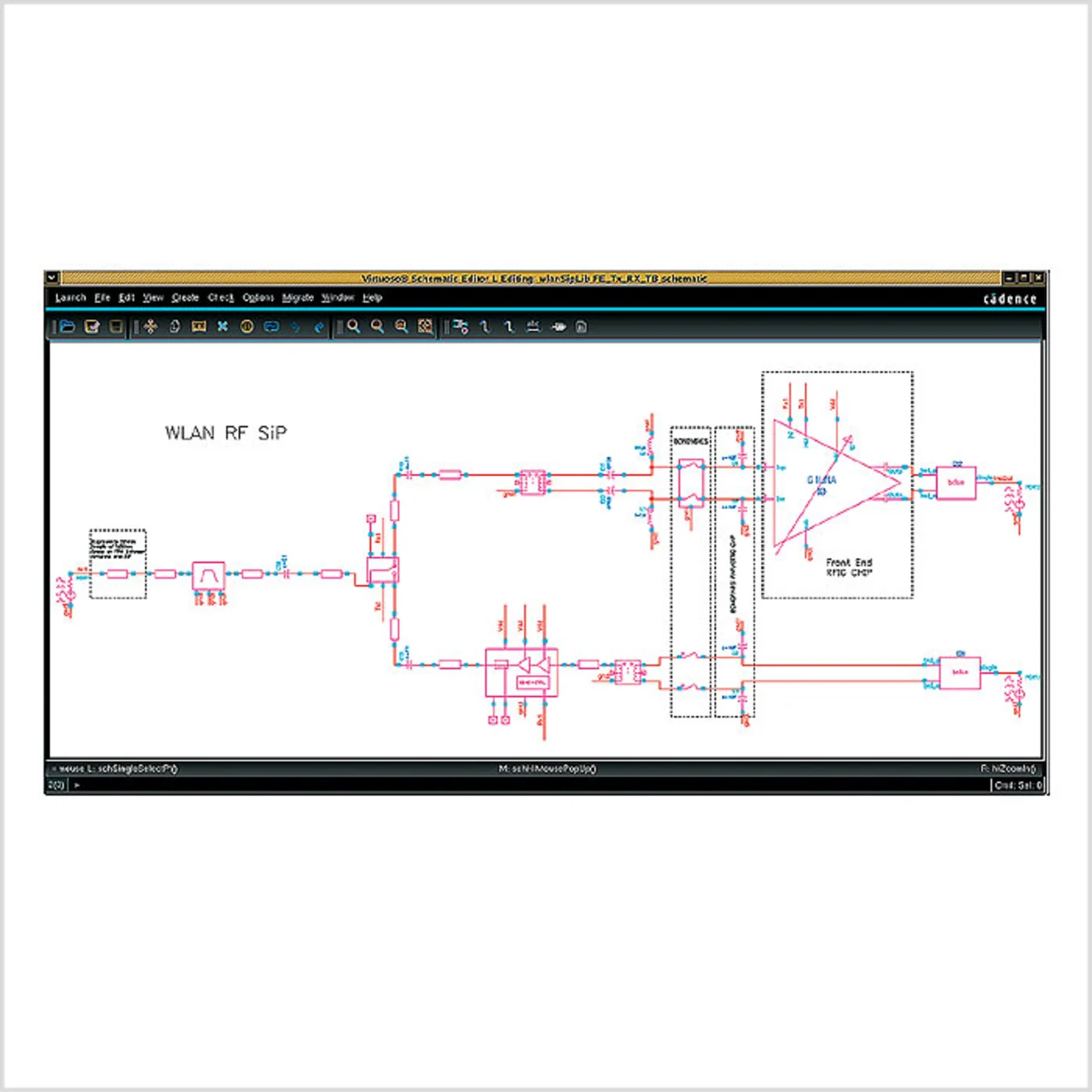

Neben den auf dem Top-Level basierenden Testbenches für die Gesamtsimulation sind auch zahlreiche Betrachtungen von Sub-Systemen und vor allem der Übergänge zwischen größeren Baugruppen notwendig. Wie bereits erwähnt, ist vor allem das HF-Frontend genauer zu untersuchen. Bild 4 zeigt eine entsprechende Testbench, die die Simulation des Empfangspfades von der Antenne bis zum Ausgang des Low-Noise-Amplifiers (LNA), der sich bereits auf dem HF-IC befindet, erlaubt.

Für die jeweiligen Testbenches lassen sich – je nach Entwurfsfortschritt – die Konfigurationen, also die Abstraktionsebenen der einzelnen Blöcke und Komponenten, beliebig variieren. So kann ein zunächst verwendetes Verhaltensmodell sehr einfach gegen eine genauere Modell-Beschreibung (z.B. ein S-Parameter-File für ein verwendetes Filter) ausgetauscht und später auch durch zusätzliche parasitäre Informationen wie Kontaktzuleitungen, die aus dem Layout extrahiert worden sind, ergänzt werden.

Physikalische SiP-Implementierung

Ab einem bestimmten Punkt ist das Design weit genug fortgeschritten, um mit der physikalischen Layout-Implementierung beginnen zu können. Dies sollte möglichst frühzeitig geschehen, um auf diese Weise initiale Abschätzungen bezüglich Gehäusegröße oder I/O-Anordnung zu überprüfen.

Da das Gesamtsystem bereits vollständig als Schaltplan beschrieben ist, kann nahezu automatisch ins Layout übergegangen werden – und zwar unter Sicherstellung der richtigen Konnektivität zwischen den einzelnen Bauteilen. Für jede zu platzierende Komponente existiert dazu eine physikalische Repräsentanz. Diese werden zum Beispiel für die verwendeten Dies innerhalb des IC-Layout-Tools generiert, oder sie bestehen für verwendete SMD-Bauteile vorab als Bibliothekselement. Durch die geschaffene Verbindung von Schaltplan und Layout lassen sich weitere Entwurfsschritte wie Checks Layout vs. Schematic (LVS), Cross-Probing oder die Back-Annotation von Layout-Parametern ins Schematic realisieren.

- SiP statt SoC: Entwurf eines HF-Systems

- Literatur

- Umfassendere Berücksichtigung parasitärer Effekte

- SiP statt SoC: Entwurf eines HF-Systems

- SiP statt SoC: Entwurf eines HF-Systems

- Durchgängiger Design-Flow, basierend auf realistischem Referenzdesign

- SiP statt SoC: Entwurf eines HF-Systems