IC-Schaltungsentwurf ist mit der physikalischen Implementierung des Gehäuses zu verbinden

SiP statt SoC: Entwurf eines HF-Systems

Fortsetzung des Artikels von Teil 1

Literatur

Neben den Leitbahnen stellen Bonddrähte oder im Substrat integrierte Spulen weitere Herausforderungen für die Modellierung dar. Hier bedarf es meist elektromagnetischer Simulatoren, um gerade die dreidimensionale Struktur oder die Interaktion zwischen einzelnen Elementen ausreichend genau zu erfassen [6]. Auch hier muss der Designer verschiedene Lösungsmethoden zur Verfügung haben, die eine flexible Wahl zwischen Extraktionsgenauigkeit und -geschwindigkeit erlauben. Neben der notwendigen Anbindung unterschiedlicher EM-Simulatoren ist aber vor allem die effiziente Back-Annotation des extrahierten Modells oder S-Parameter-Files für einen effizienten Flow entscheidend.

Eine durchgängige Entwurfsumgebung, basierend auf einer fortschrittlichen Methodik, ist Grundvoraussetzung zur erfolgreichen Realisierung hochintegrierter, drahtloser Datenübertragungssysteme, und dem entspricht der eben beschriebene Flow, der eine skalierbare Front-to-Back-Lösung für HF-System-in-Packages enthält. Diese verbindet Schaltungsentwurf und Simulation einschließlich der IC-Bausteine mit der physikalischen Implementierung des gemeinsamen Gehäuses. go

[1] www.cadence.com/products/kits/index.aspx?lid=cadence_kits

[2] Hartung, J.: Durchgängiger Design-Flow für RFIC-Designs. Elektronik 2006, H. 14, S. 56ff.

[3] www.cadence.com/products/kits/rf_sip_methodology/index.aspx

[4] Wittmann, R.; Hartung, J.; Wassener, H.-J.; Tränkle, G.; Schröter, M.: RF Design Technology for Highly Integrated Communication Systems. Proceedings DATE 03, März 2003, S. 842 bis 847, IEEE Computer Society.

[5] Dunham, W.; Kirkham, R.; Stolarz, D.; Hartung, J.: RF Module Design: Requirements and Issues. RF Design Journal, Juni 2003.

[6] Munteanu, I.; Becker, U.; Thoma, P.; Wagner, B.; Hartung, J.: 3D Electromagnetic Field Simulation for Analog Design. Analog 2002 Konferenz, 13./14. Mai 2002, Bremen.

Jobangebote+ passend zum Thema

| Dr.-Ing. Jürgen Hartung juergenh@cadence.com |

Für die physikalische Implementierung ist die Verwendung von Constraints wichtig, da man mit ihnen entsprechende Erkenntnisse aus dem Schaltungsentwurf mit in das Layout übernehmen kann. Sind beispielsweise bestimmte Leitungen als kritisch eingestuft worden, werden entsprechende Vorgaben – wie das differenzielle Verdrahten der Leitung oder bestimmte Abschirmungsmaßnahmen – vom nachfolgenden Floorplanner und Router ohne erneute Eingabe berücksichtigt. Damit sind auch die einzelnen Schritte der physikalischen Implementierung, ähnlich dem Schaltungsentwurf, wiederholbar und erlauben so eine schnelle und flexible Reaktion auf Änderungen (sog. ECOs – Engineering Change Orders).

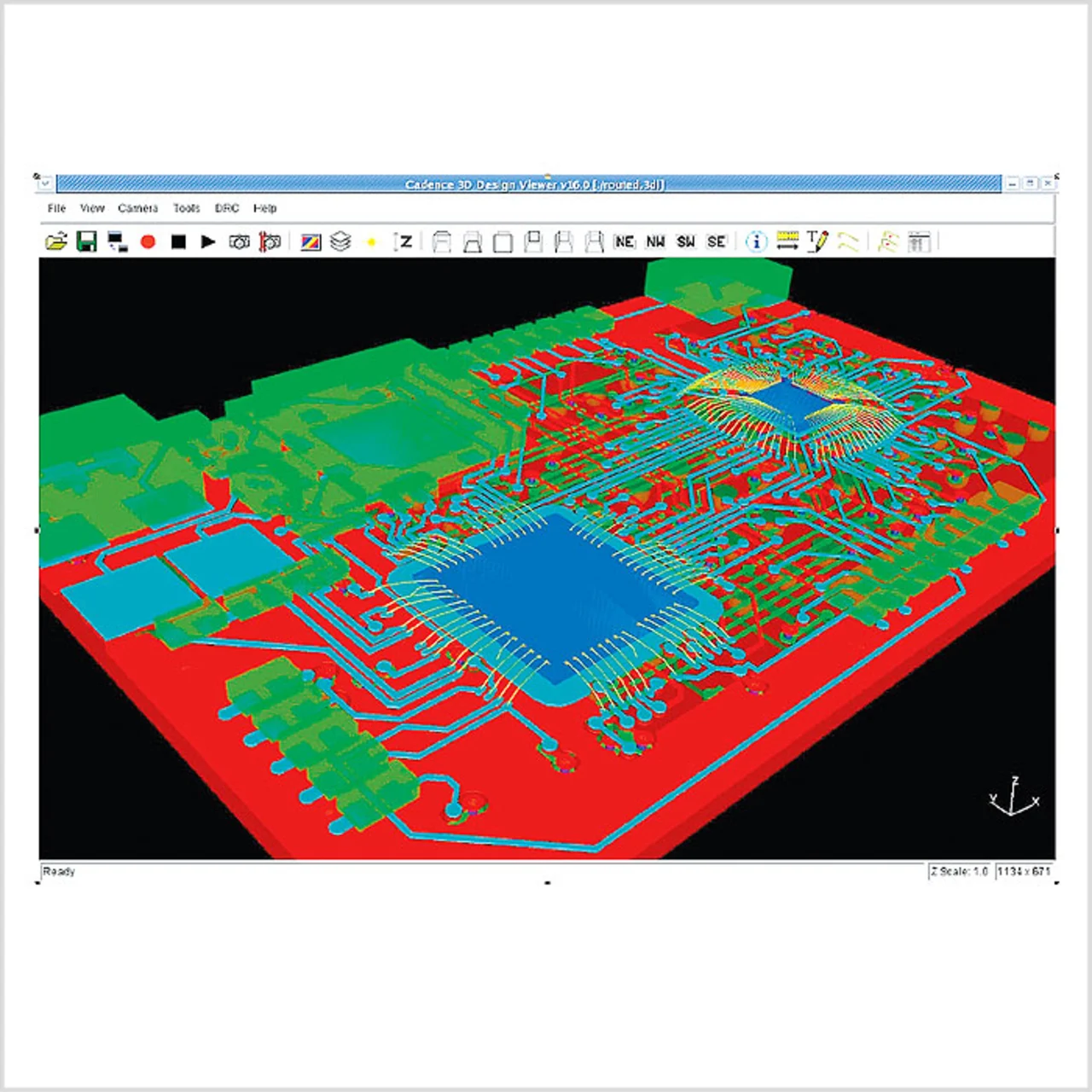

Nach der Platzierung der einzelnen Komponenten erfolgt die Verdrahtung. Durch die enthaltenen Konnektivitäts-Informationen können offene Verbindungen im Layout sichtbar gemacht werden, was beispielsweise das manuelle Verdrahten kritischer HF-Netze erleichtert. Abschließend erfolgt die Überprüfung der Design-Regeln. Neben der Verwendung entsprechender Werkzeuge ist auch die dreidimensionale Visualisierung des Layouts zur Prüfung z.B. der Bonddraht-Verbindungen hilfreich (siehe Bild 5).

- SiP statt SoC: Entwurf eines HF-Systems

- Literatur

- Umfassendere Berücksichtigung parasitärer Effekte

- SiP statt SoC: Entwurf eines HF-Systems

- SiP statt SoC: Entwurf eines HF-Systems

- Durchgängiger Design-Flow, basierend auf realistischem Referenzdesign

- SiP statt SoC: Entwurf eines HF-Systems