Marktübersicht

FPGA-Designsoftware: Von Web-based bis zum "Maßanzug"

Fortsetzung des Artikels von Teil 1

C-zu-FPGA-Synthese mit Hilfe von „Impulse CoDeveloper“

Mit dem Programmwerkzeug Impulse CoDeveloper werden Systementwickler angesprochen, die einen zeitsparenden Weg suchen, um ihre in der Programmiersprache C entwickelten Algorithmen in FPGA-Technologie umzusetzen. Der von der eVision Systems GmbH lieferbare CoDeveloper eignet sich für Anwendungen der Bild- und Video-Bearbeitung, der digitalen Signalverarbeitung sowie für Methoden der Datenkomprimierung und Verschlüsselung. Ein weiteres Anwendungsfeld ist die Hardware-Beschleunigung komplexer Algorithmen, die z.B. in den Bereichen Bioinformatik und der statistischen Auswertung von Finanzdaten (High Performance Computing) vorkommen.

Der CoDeveloper ist ein auf dem ANSI-C-Standard basierendes Synthese-Werkzeug und hilft Entwicklern, die Vorteile der FPGA-Technologie für die Algorithmen-Beschleunigung zu nutzen. Es werden derzeit die Zieltechnologien von Xilinx und Altera unterstützt. Um komplette FPGA-Lösungen in Bezug auf Verifikation und Beschleunigung der umgesetzten Algorithmen anbieten zu können, arbeitet man ferner mit weiteren Plattformherstellern wie Pico Computing zusammen.

Aldec Riviera-Pro für komplexe Simulationen

eVision Systems, ein Spezialist für FPGA-Dienstleistungen und –Schulungen, bietet mit Riviera-Pro zudem einen Simulator für die Verifikation komplexer ASICs und großer FPGA-Designs an. Der Single-Kernel-Simulator, der VHDL-, Verilog- und SystemC-Modelle analysiert, enthält auch eine komfortable Debug-Umgebung. Hinzu kommen weitere nützliche Programmroutinen wie Accelerated Waveform Viewer und Code Coverage, ferner SystemVerilog-, PSL- und OVA- Assertions sowie Functional Coverage. Mit dem Programmpaket lassen sich VHDL- und Verilog-Code-Linting ebenso durchführen wie DSP-Algorithmus-Design/Co Verifikation mit Hilfe von MATLAB und Simulink. Nebenbei ist das Tool-Set Script-kompatibel mit anderen HDL-Simulatoren, und es werden neben Windows- auch Unix-Systeme (z.B. Linux) unterstützt.

Jobangebote+ passend zum Thema

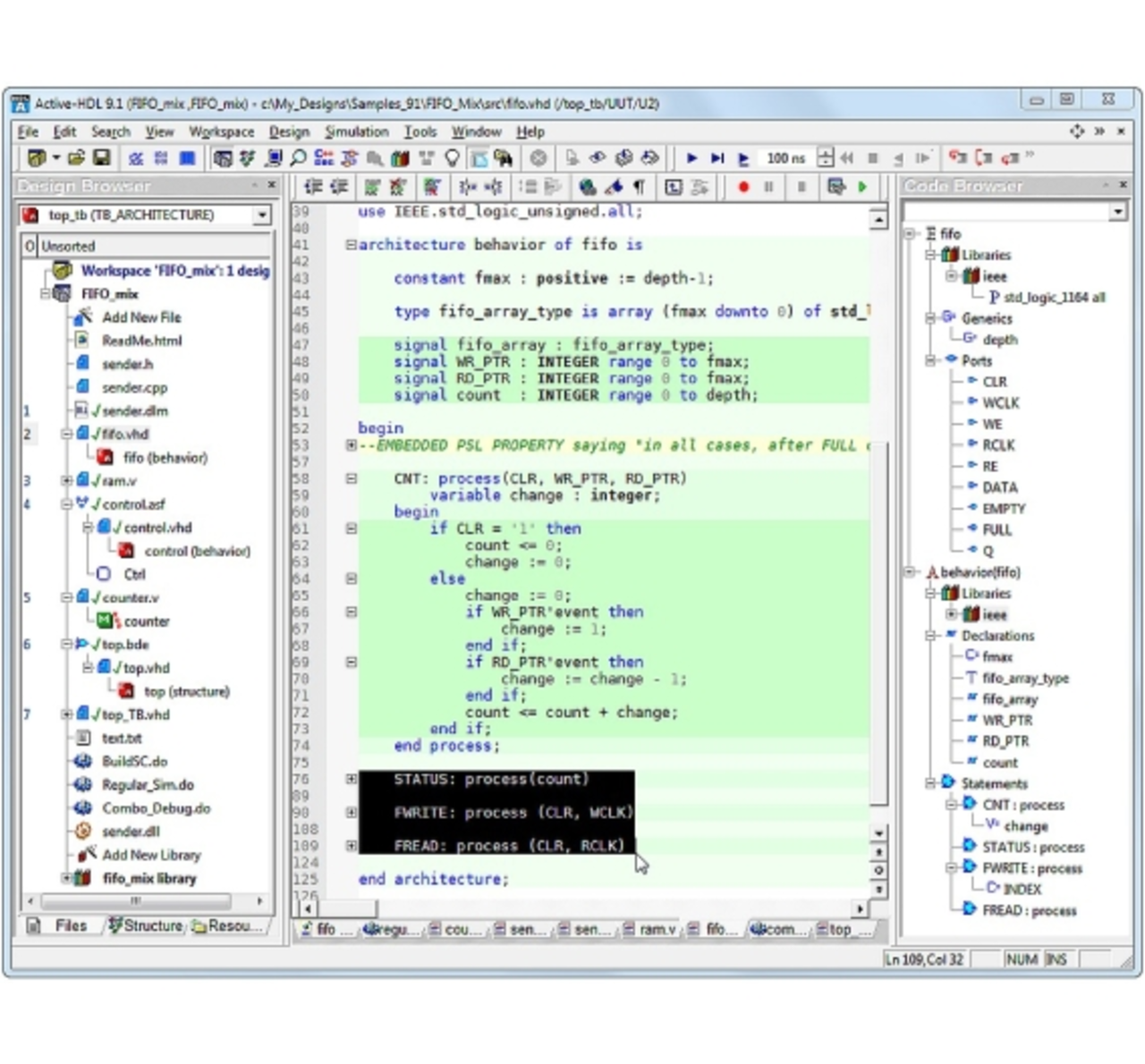

Aldec Active-HDL für den kompletten FPGA-Designprozess

Die im US-Bundesstaat Nevada ansässige Softwarehaus Aldec hat mit Active-HDL ein weiteres Programmpaket entwickelt, das derzeit in der Version 9.1 vermarktet wird und eine vollständig integrierte Entwicklungsumgebung für das Design und die Verifikation von FPGAs darstellt.

Designentwürfe werden dabei mit Hilfe der Hardwarebeschreibungssprachen VHDL, Verilog und/oder C/C++ erstellt. Active HDL ist in verschiedenen Konfigurationen verfügbar, die dem Anforderungsprofil der Anwender entgegenkommen:

- Active-HDL Designer Edition eignet sich für Kunden, die von Zeit zu Zeit kleinere und mittlere FPGA-Designs entwickeln (ca. 40 bis 50 Mann-Tage pro Jahr)

- Active-HDL PE ist für Kunden gedacht, die regelmäßig kleine und mittlere FPGA-Designs entwickeln oder komplexe IP-Cores (z.B: PCI Express) einsetzen (ca. 50 bis 120 Mann-Tage/Jahr)

- Active-HDL EE nutzen jene Kunden, welche den Hauptteil Ihrer Arbeit mit dem VHDL- oder Verilog-Entwurf verbringen (mehr als 120 Mann-Tage/Jahr) und komplexe bis hoch komplexe FPGA-Designs entwickeln.

JTAG-FPGA- & -Board-Testwerkzeuge

Mit Hpe_JTAG von Gleichmann Electronics Research hat der Dienstleister eVision Systems ein weiteres Werkzeug im Programm, das allerdings für die Test und Fehleranalyse von Hardware mit JTAG-fähigen Bausteinen geeignet ist. Hpe_JTAG ermöglicht dem Entwickler die volle Kontrolle über die logischen Zustände seiner I/O-Register, welche über die Boundary Scan Chain zugänglich sind. Für einen Bruchteil der üblichen Kosten kann das Skript-fähige Werkzeug auch für automatisierte Tests in der Produktion eingesetzt werden.

Das Werkzeug unterstützt die JTAG-Anweisungen wie SAMPLE, EXTEST und INTEST: Letztere wird eingesetzt, um die internen Funktionen des Bausteins in derJTAG-Kette zu kontrollieren. Mit der Anweisung kann der Wert der Output-Pins bestimmt werden, und der Wert der Input-Pins kann dabei gelesen werden. Dabei ist zu beachten, dass die Verfügbarkeit der INTEST-Anweisungen von den jeweiligen Eigenschaften der Bausteine abhängig ist.

- FPGA-Designsoftware: Von Web-based bis zum "Maßanzug"

- C-zu-FPGA-Synthese mit Hilfe von „Impulse CoDeveloper“

- Ein „Diamant“ unter den Tools für Programmierbare Logikbausteine?

- Kombinierte Hard-und Software-Entwurfswerkzeuge zu Paketlösungen

- Synopsys liefert für FPGA-Designs Synthese-Tools mit „Knopfdruck-Philosophie“